# THE SUITABILITY OF ACTIVE INDUCTORS FOR A WIDE RANGE OF CMOS IMPLEMENTATIONS

#### by

#### Muhammed Mustafa Kızmaz

$\operatorname{B.S.},$  Electrical and Electronics Engineering, Boğaziçi University, 2022

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillment of the requirements for the degree of Master of Science

Graduate Program in Electrical and Electronics Engineering Boğaziçi University

#### ACKNOWLEDGEMENTS

I would like to thank my supervisor, Prof. Oğuzhan Çiçekoğlu for his guidance, motivation, advice, and invaluable contributions in the process of my thesis. I found his inestimable guidance with me at every moment of this study. It was an excellent opportunity for me to work with him.

I would like to express my sincere gratitude to my company, TUBITAK BILGEM.

I appreciate the support of my lab, TUTEL, in the successful conclusion of my thesis.

I also want to extend my great thanks to Assoc. Prof. Tufan Coşkun Karalar and Assist. Prof. Faik Başkaya for being part of my evaluation committee of this thesis.

Moreover, I would want to show my appreciation to Prof. Norbert Herenscar and Assoc. Prof. Salih Ergün for their collaboration during the thesis process.

Finally, I sincerely thank my wife, little daughters, parents, and sisters for their encouragement, patience, and unconditional trust. When I got weary, their love raised me again. It would not have been possible to complete this study without their support.

#### ABSTRACT

# THE SUITABILITY OF ACTIVE INDUCTORS FOR A WIDE RANGE OF CMOS IMPLEMENTATIONS

Integrated circuits (ICs) form the heart of today's technology thanks to their prominent features such as minimal size, reduced cost, high reliability, and low power consumption. Then, inductors have found a wide range of uses in modern IC implementations. These application areas can be exemplified by impedance matching, bandwidth enhancement, gain boosting, frequency selection, phase shifters, and LC oscillators. The frequently preferred method for the required inductances is using CMOS spiral inductors. However, spiral inductors have significant shortcomings that limit their use in CMOS realization. For example, spiral inductors consume a large chip area, and it is impossible to tune their inductance values. Moreover, these inductors have low quality factors (Q) and low self-resonant frequencies. Due to the drawbacks of spiral inductors, researchers have been looking for alternatives. One of these approaches is active inductors (AIs), which use active circuit components to synthesize required inductance. Numerous AI topologies have been presented in the literature. Each architecture may be selected depending on the inductance needs of the application. Thus, AIs have a broad variety of applications in CMOS implementations due to their diversity of topologies. This thesis demonstrates that employing AIs is feasible for a range of CMOS implementations. Its feasibility is proven by designing an AI-based wide-tunable LC voltage-controlled oscillator (LC-VCO), a lattice-based allpass filter, and an autonomous chaotic oscillator.

### ÖZET

## AKTİF İNDÜKTÖRLERİN GENİŞ YELPAZEDE CMOS UYGULAMALARI İÇİN UYGUNLUĞU

Entegre devreler (IC'ler), minimum boyut, düşük maliyet, yüksek güvenilirlik ve düşük güç tüketimi gibi öne çıkan özellikleri sayesinde günümüz teknolojisinin kalbini oluşturmaktadır. İndüktörler de modern entegre devre (IC) uygulamalarında geniş kullanım alanına sahip bileşenlerlerden biridir. Bu uygulama alanları empedans eşleştirme, bant genişliği geliştirme, kazanç artırma, frekans seçimi, faz kaydırıcılar ve LC osilatörler olarak örneklendirilebilir. CMOS uygulamalarında ihtiyaç duyulan endüktanslar için sıklıkla tercih edilen yöntem spiral indüktörlerin kullanılmasıdır. Ancak, spiral indüktörler CMOS uygulamalarındaki kullanımlarını sınırlayan önemli eksikliklere sahiptir. Orneğin, spiral indüktörler büyük silikon alanı tüketir ve endüktans değerlerinin kontrolü mümkün değildir. Ayrıca, bu indüktörler düşük kalite faktörlerine (Q) ve rezonans frekansına sahiptir. Bu dezavantajlardan dolayı, araştırmacılar CMOS endüktans gerçeklenmesi için farklı alternatifler üzerine çalışmaktadır. Yaklaşımlardan biri, gerekli endüktansı sentezlemek için aktif devre bileşenlerini kullanan aktif indüktör (AI) yapılarıdır. Literatürde çok sayıda AI topolojisi sunulmuştur. Kullanıldığı uygulamanın endüktans ihtiyaçlarına bağlı olarak farklı AI mimarileri tercih edilebilir. Bu nedenle, Al'lar, sahip oldukları topoloji çeşitliliği sayesinde çeşitli CMOS uygulamalarında yer bulur. Bu tezde, frekansı ayarlanabilir LC voltaj kontrollü osilatör (LC-VCO), lattice tabanlı tam geçirgen filtre ve otonom kaotik osilatör tasarlanarak AI devrelerinin CMOS uygulamaları için uygulanabilirliği kanıtlanmıştır.

## TABLE OF CONTENTS

| Α( | CKNC | )WLED   | GEMENTS                              | iii |

|----|------|---------|--------------------------------------|-----|

| Αl | BSTR | ACT .   |                                      | iv  |

| ÖZ | ZET  |         |                                      | V   |

| LI | ST O | F FIGU  | TRES                                 | ix  |

| LI | ST O | F TABI  | LES                                  | iii |

| LI | ST O | F SYM   | BOLS                                 | iv  |

| LI | ST O | F ACR   | ONYMS/ABBREVIATIONS                  | ζV  |

| 1. | INT  | RODUC   | CTION                                | 1   |

| 2. | BAC  | CKGRO   | UND                                  | 3   |

|    | 2.1. | CMOS    | Spiral Inductors                     | 3   |

|    | 2.2. | Genera  | al Characteristics of AIs            | 4   |

|    | 2.3. | Funda   | mentals of Gyrator-C-Based AIs       | 6   |

|    |      | 2.3.1.  | Lossless Gyrator-C-Based GAIs        | 6   |

|    |      | 2.3.2.  | Lossy Gyrator-C-Based GAIs           | 8   |

|    |      | 2.3.3.  | Lossless Gyrator-C-Based FAIs        | 9   |

|    |      | 2.3.4.  | Lossy Gyrator-C-Based FAIs           | 11  |

|    | 2.4. | Perfori | mance Parameters of AIs              | 12  |

|    | 2.5. | Chapte  | er Summary                           | 15  |

| 3. | PRO  | POSEI   | O ACTIVE INDUCTOR CIRCUITS           | 16  |

|    | 3.1. | Propos  | sed Core Circuits                    | 16  |

|    |      | 3.1.1.  | Positive Active Inductor - 1 (PAI-1) | 16  |

|    |      | 3.1.2.  | Positive Active Inductor - 2 (PAI-2) | 17  |

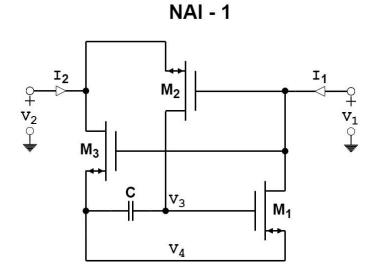

|    |      | 3.1.3.  | Negative Active Inductor - 1 (NAI-1) | 19  |

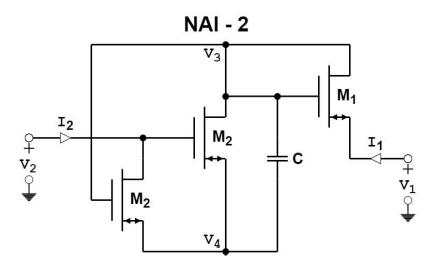

|    |      | 3.1.4.  | Negative Active Inductor - 2 (NAI-2) | 20  |

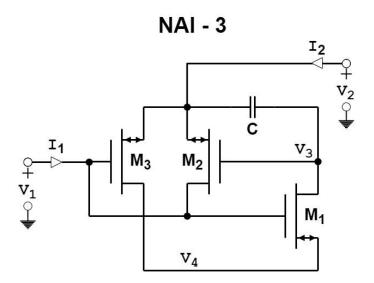

|    |      | 3.1.5.  | Negative Active Inductor - 3 (NAI-3) | 21  |

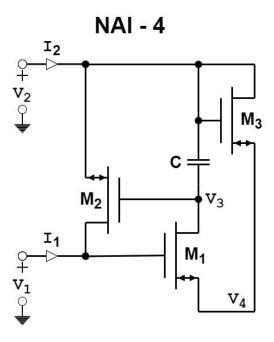

|    |      | 3.1.6.  | Negative Active Inductor - 4 (NAI-4) | 22  |

|    |      | 3.1.7.  | Negative Active Inductor - 5 (NAI-5) | 23  |

|    | 3.2. | Biased  | Circuit Configurations               | 24  |

|    |      | 3.2.1. | Biased Version of PAI-1                           | 24 |

|----|------|--------|---------------------------------------------------|----|

|    |      | 3.2.2. | Biased Version of NAI-5                           | 25 |

|    | 3.3. | Chapte | er Summary                                        | 26 |

| 4. | WID  | E-TUN  | VABLE LC-VCO DESIGN WITH A NOVEL ACTIVE INDUCTOR  | 27 |

|    | 4.1. | Chapte | er Introduction                                   | 27 |

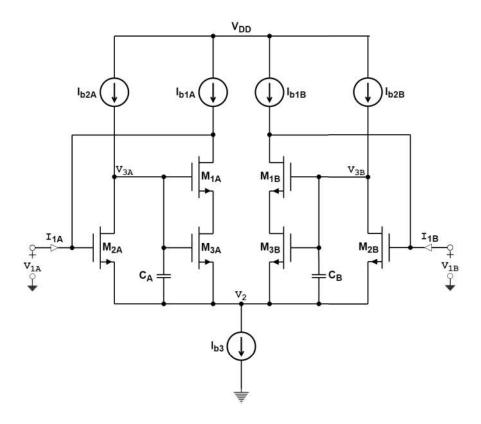

|    | 4.2. | Propos | sed FAI Circuit                                   | 28 |

|    | 4.3. | LC-VC  | CO Design                                         | 32 |

|    |      | 4.3.1. | Circuit Topology                                  | 33 |

|    |      | 4.3.2. | Design Procedure                                  | 34 |

|    | 4.4. | Simula | ation Results                                     | 39 |

|    |      | 4.4.1. | LC-VCO Dynamic Range and Phase Noise Analysis     | 39 |

|    |      | 4.4.2. | Rail-to-Rail Output Swing Improvement             | 41 |

|    |      | 4.4.3. | Frequency Tuning Mechanism                        | 43 |

|    |      | 4.4.4. | Literature Comparison and a Brief Discussion      | 45 |

|    | 4.5. | Chapte | er Summary                                        | 47 |

| 5. | A 4- | BITS A | ACTIVE INDUCTOR-BASED LATTICE 24.5—50 PS ALL-PASS |    |

|    | FILT | TER DE | ESIGN FOR 5G APPLICATIONS                         | 48 |

|    | 5.1. | Chapte | er Introduction                                   | 48 |

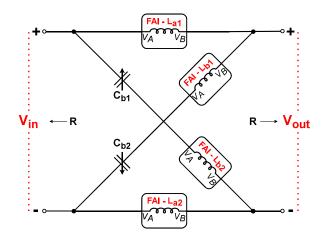

|    | 5.2. | Descri | ption of the Lattice All-Pass Filter Topology     | 49 |

|    | 5.3. | Propos | sed Floating Active Inductors (FAIs)              | 54 |

|    | 5.4. | Simula | ation Results                                     | 59 |

|    | 5.5. | Review | v of the Literature and Comparison                | 67 |

|    | 5.6. | Chapte | er Summary                                        | 68 |

| 6. | A DI | ESIGN  | OF AUTONOMOUS CHAOTIC OSCILLATOR ROBUST AGAINS    | Γ  |

|    | EXT  | ERNA   | L INTERFERENCE                                    | 69 |

|    | 6.1. | Chapte | er Introduction                                   | 69 |

|    | 6.2. | Auton  | omous Chaotic Oscillator                          | 70 |

|    | 6.3. | VDTA   | -Based Active Inductor                            | 73 |

|    | 6.4. | Simula | ation Results                                     | 77 |

|    | 6.5. | Chapte | er Summary                                        | 79 |

| 7  | CON  | ICLUSI | ON                                                | 80 |

| REFERENCES . |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 82 | 2 |

|--------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|----|---|

|--------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|----|---|

## LIST OF FIGURES

| Figure 2.1. | The scheme of lossless gyrator-C-based GAI                  | 7  |

|-------------|-------------------------------------------------------------|----|

| Figure 2.2. | The scheme of lossy gyrator-C-based GAI                     | 8  |

| Figure 2.3. | The equilavent RLC network of the lossy gyrator-C-based GAI | 9  |

| Figure 2.4. | The scheme of lossless gyrator-C-based FAI                  | 10 |

| Figure 2.5. | The scheme of lossy gyrator-C-based FAI                     | 11 |

| Figure 2.6. | The equivalent RLC network of the lossy gyrator-C-based FAI | 12 |

| Figure 3.1. | The core schematic of the proposed PAI-1 circuit            | 17 |

| Figure 3.2. | The core schematic of the proposed PAI-2 circuit            | 18 |

| Figure 3.3. | The core schematic of the proposed NAI-1 circuit            | 19 |

| Figure 3.4. | The core schematic of the proposed NAI-2 circuit            | 20 |

| Figure 3.5. | The core schematic of the proposed NAI-3 circuit            | 21 |

| Figure 3.6. | The core schematic of the proposed NAI-4 circuit            | 22 |

| Figure 3.7. | The core schematic of the proposed NAI-5 circuit            | 23 |

| Figure 3.8. | The schematic of the biased version of PAI-1 circuit        | 24 |

| Figure 3.9.  | The schematic of the biased version of NAI-5 circuit                                       | 25 |

|--------------|--------------------------------------------------------------------------------------------|----|

| Figure 3.10. | The schematic of the fully differential NAI-5 circuit                                      | 26 |

| Figure 4.1.  | The core circuit of the proposed AI                                                        | 29 |

| Figure 4.2.  | The biased version of the proposed AI circuit                                              | 30 |

| Figure 4.3.  | The equivalent RLC network of the lossy gyrator-C-based FAI                                | 31 |

| Figure 4.4.  | Characteristics of the proposed FAI                                                        | 33 |

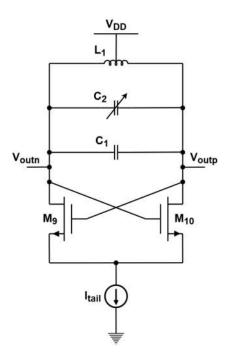

| Figure 4.5.  | Bottom-biased NMOS cross-coupled LC-VCO scheme                                             | 34 |

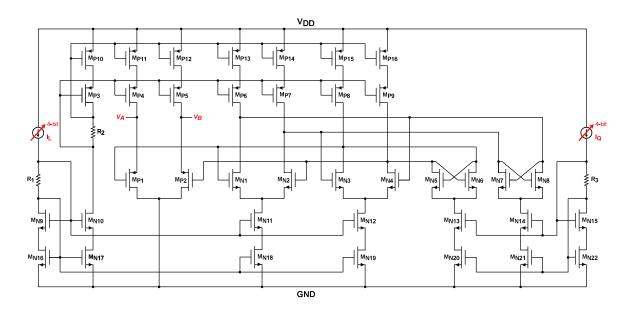

| Figure 4.6.  | The detailed schematic of the designed LC-VCO                                              | 35 |

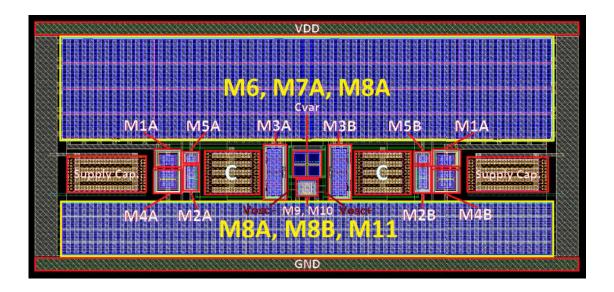

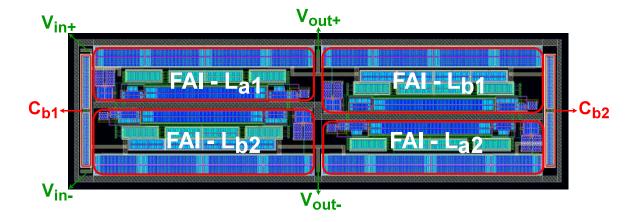

| Figure 4.7.  | The layout of the designed LC-VCO                                                          | 37 |

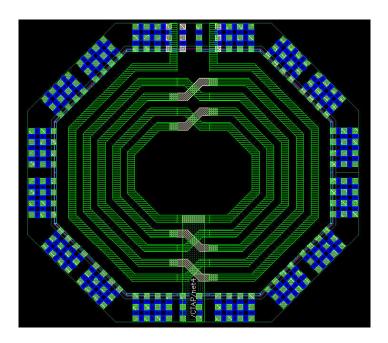

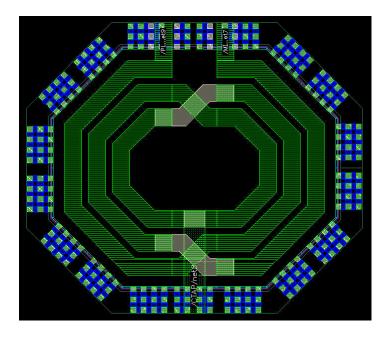

| Figure 4.8.  | The spiral inductor with the same inductance value as the FAI used in the designed LC-VCO  | 39 |

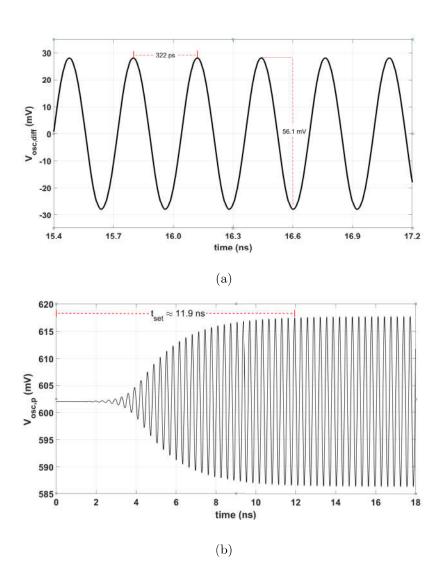

| Figure 4.9.  | (a) Differential output. (b) Settling time of the oscillator                               | 40 |

| Figure 4.10. | Phase noise of the designed oscillator                                                     | 41 |

| Figure 4.11. | The buffer schematic for rail-to-rail oscillation                                          | 42 |

| Figure 4.12. | Oscillation frequency versus control voltage for each 8 clusters                           | 44 |

| Figure 5.1.  | Flow graph of the procedure to generate the prototype all-pass filter denominator $E_n(s)$ | 50 |

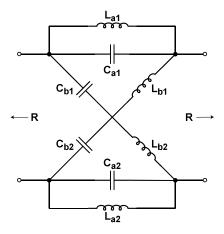

| Figure 5.2.  | The schematic of the second-order lattice all-pass network                                   | 52    |

|--------------|----------------------------------------------------------------------------------------------|-------|

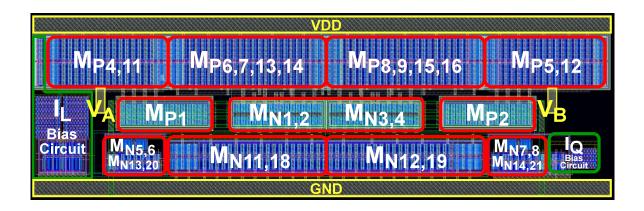

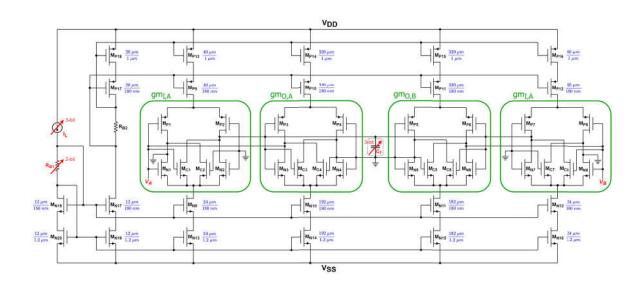

| Figure 5.3.  | Proposed CMOS implementation of FAIs                                                         | 55    |

| Figure 5.4.  | The equivalent RLC network of the designed FAIs                                              | 55    |

| Figure 5.5.  | The layout of the FAI-La circuit with the dimension of 110 $\mu$ m $	imes$ 30 $\mu$ m        | ı. 59 |

| Figure 5.6.  | The final schematic of the designed second-order lattice APF                                 | 60    |

| Figure 5.7.  | The layout of the designed lattice APF with the dimension of 240 $\mu$ m $\times$ 70 $\mu$ m | 61    |

| Figure 5.8.  | The spiral inductor with the same inductance value as the FAI-L $_{\!a}$ circuit             | 61    |

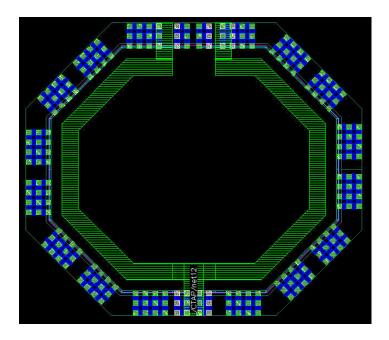

| Figure 5.9.  | The spiral inductor with the same inductance value as the FAI-L $_{\rm b}$ circuit           | 62    |

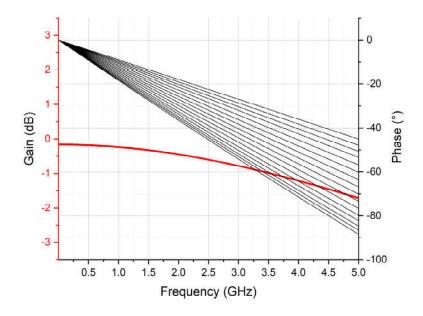

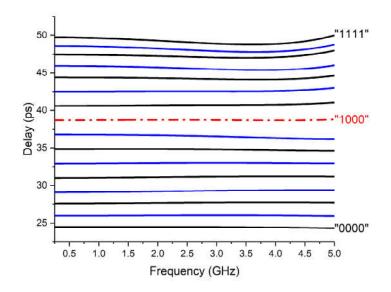

| Figure 5.10. | The frequency response of the designed APF for different tuning configurations               | 63    |

| Figure 5.11. | The group delay of the designed APF for different tuning configurations                      | 64    |

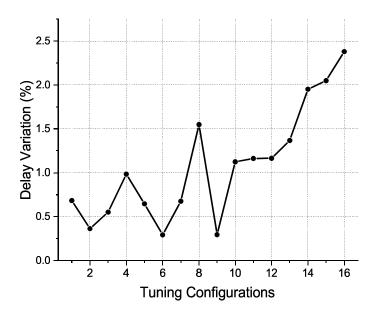

| Figure 5.12. | The group delay variations of the designed APF for different tuning configurations           | 64    |

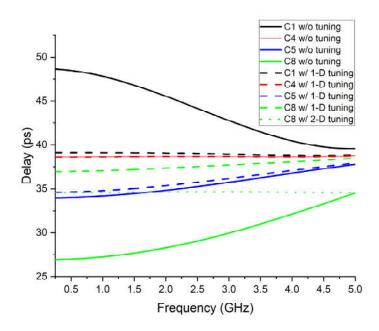

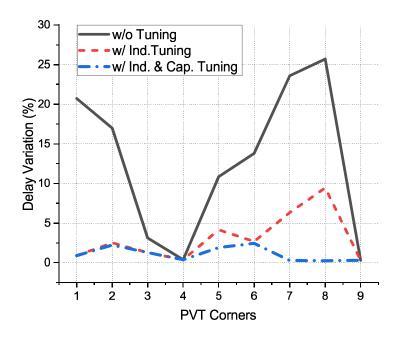

| Figure 5.13. | The group delay of the designed APF for PVT corners                                          | 65    |

| Figure 5.14. | The group delay variations of the designed APF for PVT corners.                              | 66    |

| Figure 6.1. | The schematic of the proposed chaotic oscillator                              | 70 |

|-------------|-------------------------------------------------------------------------------|----|

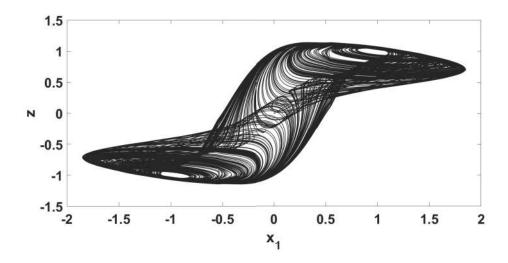

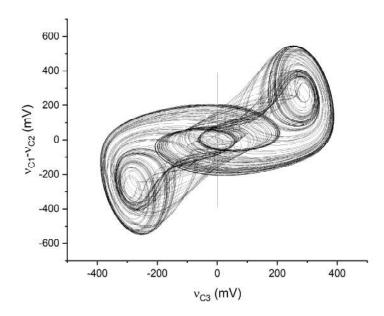

| Figure 6.2. | The chaotic trajectory of the designed system with numerical analysis.        | 73 |

| Figure 6.3. | The schematic of the designed FAI                                             | 74 |

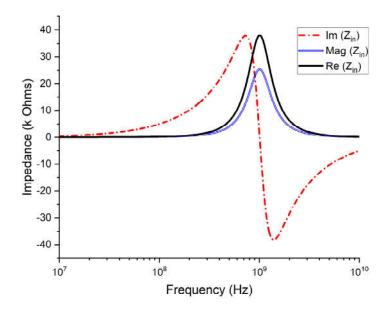

| Figure 6.4. | The input impedance graphs of the designed FAI for the nominal tuning setting | 76 |

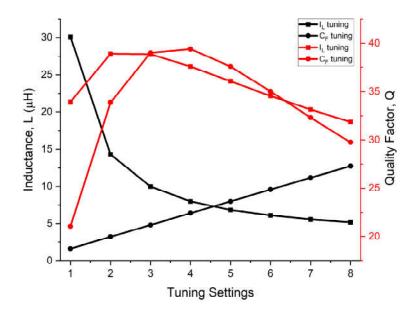

| Figure 6.5. | The inductance and quality factor of the FAI for different tuning settings    | 77 |

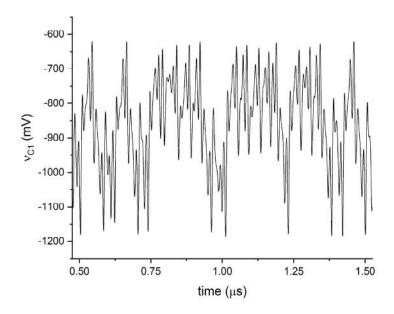

| Figure 6.6. | Transient simulation results for the $v_{C1}$ node                            | 78 |

| Figure 6.7. | The simulated chaotic trajectory of the designed oscillator                   | 78 |

## LIST OF TABLES

| Table 4.1. | Parameters of the designed FAI for the $Cluster_{100}$ case                       | 36 |

|------------|-----------------------------------------------------------------------------------|----|

| Table 4.2. | Aspect ratios of the transistors in the designed LC-VCO shown in Figure 4.6       | 38 |

| Table 4.3. | Transistor dimensions of the buffer shown in Figure 4.11                          | 43 |

| Table 4.4. | Comparing the designed LC-VCO with the literature                                 | 46 |

| Table 5.1. | Component values of the proposed lattice filter                                   | 53 |

| Table 5.2. | Aspect ratios of the transistors in the designed FAIs shown in Figure 5.3         | 58 |

| Table 5.3. | Final component values of the proposed lattice filter and their tuning ranges.    | 60 |

| Table 5.4. | Descriptions of each PVT corner introduced in Figures 5.13 and 5.14.              | 66 |

| Table 5.5. | Literature Comparison                                                             | 67 |

| Table 6.1. | Aspect ratios of the transistors in the suggested chaotic oscillator (Figure 6.1) | 73 |

| Table 6.2. | Transistor sizes of the transconductance stages of the designed FAI (Figure 6.3)  | 74 |

#### LIST OF SYMBOLS

A Angular coefficient

C<sub>p</sub> Equivalent parallel capacitance of inductors

C<sub>ox</sub> Oxide capacitance of MOS transistors

$E_n(s)$  Allpass filter denominator

f<sub>t</sub> Transition frequency of MOS transistors

g<sub>m</sub> Transconductance of MOS transistors

H(s) Transfer function

L Length of MOS transistors

L<sub>act</sub> Equivalent inductance of AI

P<sub>dc</sub> DC power consumption

R<sub>p</sub> Equivalent parallel resistance of inductors

R<sub>s</sub> Equivalent series resistance of inductors

V<sub>sat</sub> Saturation voltage of MOS transistors

V<sub>th</sub> Threshold voltage of MOS transistors

W Width of MOS transistors

Q Quality Factor

$\mu_{\rm n}$  Electron mobility

$\tau_0$  Constant term of the delay function

$\tau_{\rm g}(\Omega)$  Group delay function

$\phi(\Omega)$  Phase function

$\Omega$  Normalized frequency

### LIST OF ACRONYMS/ABBREVIATIONS

AI Active Inductor

APF Allpass Filter

ASIC Application Specific Integrated Circuit

CMOS Complementary Metal-Oxide Semiconductor

DTR Delay Tuning Range

FAI Floating Active Inductor

FOM Figure of Merit

GAI Grounded Active Inductor

IC Integrated Circuit

ICMR Input Common-Mode Range

KCL Kirchoff Current Law

LC-VCO LC Voltage-Controlled Oscillator

MOS Metal-Oxide Semiconductor

MOSFET Metal-Oxide Semiconductor Field Effect Transistor

MSB Most significant bit

NAI Negative Active Inductor

NMOS N-type Metal-Oxide Semiconductor

OTA Operational Transconductance Amplifier

PAI Positive Active Inductor

PDK Process Design Kit

PLL Phase-locked Loop

PMOS P-type Metal-Oxide Semiconductor

PTR Percentage Tuning Range

PVT Process, Voltage, Temperature

RNG Random Number Generators

THD Total Harmonic Distortion

TSMC Taiwan Semiconductor Manufacturing Company

VCO Voltage-Controlled Oscillator

VDTA Voltage Differencing Transconductance Amplifier

#### 1. INTRODUCTION

With each passing day, technology increases its prevalence and importance in human life. The widespread use of integrated circuits is one of the fundamental reasons for this increase. As the use of integrated circuits expands, new production technologies continue to be developed in this area. Undoubtedly, the ability to manufacture on-chip inductors is an essential milestone in this technological evolution. Before on-chip inductors were available, off-chip passive inductors were used in communication circuits with limited bandwidth and high cost. With the discovery of IC-compatible inductors in the early 1990s [1], the usage of inductors has increased considerably. Impedance matching circuits, bandwidth enhancement methods, gain boosting techniques, frequency selection systems, RF phase shifters, and LC oscillators can be given as examples of the application areas of on-chip inductors [2–6].

Inductors, which are so popular and widely utilized, have their own set of draw-backs. The main disadvantages of CMOS spiral inductors are that they have a non-tunable structure, consume large silicon areas, have low self-resonant frequencies, and have low quality factors [2,7]. These unfavorable characteristics highlighted above have led researchers to work on finding different alternatives to the CMOS spiral inductors. As a result of these circumstances, active inductors (AIs) have a significant presence in the literature [8–35]. Als attracted attention due to their small chip area requirement, large and tunable inductance, self-resonant frequency, and quality factor.

Gyrator-C-based topologies are frequently preferred for AI synthesis. They consist of two back-to-back transconductance stages and a capacitor. In the literature, the transconductance stages of gyrator-C networks are implemented in various ways [9, 12–14]. While [9] employs single transistors to implement the transconductance stages, [12] chooses Voltage Differencing Transconductance Amplifiers (VDTAs) for the same purpose. Differential pairs are used as transconductance stages in [13] whereas Operational Transconductance Amplifiers (OTA) are preferred in [14]. For instance,

single transistor structures enable the design of AI circuits with fewer components, while VDTA-based transconductance stages improve the input common-mode range (ICMR) of the AI. Thus, various AI architectures may be feasible for different application areas, which makes AIs suitable in a very large number of application areas. To illustrate the CMOS implementation diversity of AIs, this thesis designs a wide-tunable LC-VCO circuit for circuits that need a large frequency range, such as phase-locked loop (PLL), a lattice network-based allpass filter structure for 5G applications, and a chaotic oscillator for hardware security applications.

Chapter 2 provides the background information needed to better understand the rest of the thesis. Chapter 3 includes the proposed novel positive and negative AI circuits to be used in CMOS implementations. In Chapter 4, a wide-tunable LC-VCO circuit is designed using proposed novel AI circuits based on the MOSFET-C approach of gyrator-C networks. Chapter 5 describes the design of tunable lattice network-based allpass filter for 5G applications. Chapter 6 discuses the AI-based chaotic oscillator architecture for random number generators (RNGs) in hardware security applications. Finally, the thesis is concluded in Chapter 7.

#### 2. BACKGROUND

This chapter discusses some critical topics related to this thesis in order to make the subsequent chapters more understandable. Section 2.1 introduces CMOS spiral inductors and summarizes their shortcomings. Section 2.2 discusses pros and cons of AI structures in comparison to their spiral counterparts. Then, in Section 2.3, the fundamentals of gyrator-C-based inductors synthesis with grounded and floating configuration are presented. Then, the criteria for evaluating the performance of AIs are discussed in Section 2.4. Finally, the chapter is concluded in Section 2.5.

#### 2.1. CMOS Spiral Inductors

It is one of the critical issues of modern CMOS technologies to realize on-chip inductors, also known as spiral inductors. In today's CMOS technologies, both stacked and planar spiral inductors can be produced. Semiconductor foundries provide comprehensive characterization and accurate component models of these inductors. Thus, designers have the opportunity to carry out their designs by using and simulating these models comfortably. Although multiple metal layers are available in modern CMOS technologies, only the top metal is used to build a planar spiral inductor. Otherwise, parasitic capacitance between the spiral inductor and the substrate can be increased, which is undesirable. Thus, planar spiral inductors have low inductance values; but their parasitic capacitances are also low. On the other hand, the inductance value can be significantly increased by stacking the other metals. However, undesirable parasitic capacitances will be higher for stacked spiral inductors since bottom metal layers are used. CMOS spiral inductors are known for their high linearity and low noise levels. Spiral inductors have a variety of limitations that impact their performance and applications. These drawbacks arising from their physical geometries and the CMOS technologies they are implemented can be listed as follows:

- They have non-tunable inductance values: Once the number of spiral turns is determined, the inductance value of a CMOS spiral inductor is fixed. It is not possible to tune its inductance with a simple control mechanism. There are two possibilities to increase its inductance: increasing the number of spiral turns, which consumes a huge amount of chip area; or having several metal layers stacked, which causes more parasitic capacitance.

- They consume a large silicon area: The silicon area required for routing the spiral of the inductors is high due to the low inductance of spiral inductors. Since the inductance is directly proportional to the spiral turns, a reasonable inductance can only be obtained with a few turns. Moreover, most CMOS technologies do not allow you to put another device under the spiral inductors. Hence, the spiral inductor consumes a significant portion of the silicon alone.

- They have low self-resonant frequencies: The shunt capacitance between the spiral inductor and the substrate forms an LC tank with the series inductance of the spiral inductor. Since the large metal area of the inductor causes large parasitic capacitances, the self-resonant frequency of the LC tank becomes low. The typical self-resonant frequency of spiral inductors is in the low GHz range.

- They have relatively low quality factors: CMOS spiral inductors have an ohmic loss at high frequencies, limiting their quality factors (Q). The skin-effect-induced resistance of the spiral and the resistance produced by eddy currents in the substrate are two factors that contribute to the ohmic loss of spiral inductors.

#### 2.2. General Characteristics of AIs

Circuits that do not contain an inductor but have inductive characteristics are called AIs. These networks have inductive behavior in a specific frequency band under specified DC biasing conditions and signal-swing limitations. The benefits of AIs are listed below:

• They have large and tunable inductance values: The inductance value of an AI is inversely proportional to the transconductance values of the transistors in it.

Thus, this situation makes it possible to obtain large inductance values using small transistors. Also, the inductance value of the circuit can be tuned by adjusting the bias currents of the transistors. In addition to this coarse tuning, fine-tuning can also be done by changing the capacitor values in the circuit.

- A small chip area is enough for them: Generally, MOS transistors are used in AI circuits. Further, the transconductance values of these transistors are inversely proportional to the inductance of the circuit. Thus, the silicon area of the transistors is incomparably smaller than the spiral inductors.

- They have large and tunable self-resonant frequencies: Als having a high self-resonant frequency are commonly preferred in general applications. For instance, when an AI is used in a low-pass filter, the filter will operate at frequencies below its self-resonant frequency. Thus, an AI having a high self-resonant frequency will have an extensive frequency range for proper operation. Especially for simple structures of CMOS AIs, the self-resonant frequency approaches the transit frequencies ( $f_t$ ) of the MOS transistors.

- They have large and tunable quality factors: The ohmic loss of CMOS AIs defines the quality factors, determined mainly by the finite output resistance of the transistors in the circuit. In the literature, cascodes, regulated cascodes, and negative resistor compensation techniques are applied to enhance the quality factors of AIs by increasing the equivalent output resistances of the transistors.

Besides the advantages mentioned above, there are also difficulties with AIs.

These drawbacks will be discussed below:

- They have limited dynamic range: The inductive characteristics of AIs are based on the DC biasing conditions of the transistors. Thus, the voltage swing on AI ports can directly affect the circuit operation, limiting the dynamic range. Some studies focus on the dynamic range problem in the literature. For instance, the Class AB configuration is proposed to expand the dynamic range [15].

- They are noisy circuits: Since AI circuits consist of MOS transistors, they have noisy characteristics, unlike noiseless spiral inductors. In particular, as the com-

plexity of the circuit increases, the noise it contains also increases. In the literature, some techniques are applied to minimize the noise of AIs. For example, in [16], noise has been tried to be reduced by increasing the quality factor of the AI used in an LC oscillator.

- They are sensitive to process variations: Process variations change many parameters of MOS transistors, especially the threshold value. Thus, the inductance value and quality factor of AIs are directly affected as many parameters change, particularly transconductances and output resistances of the transistors [18]. The effects of these variations are tried to be reduced by using tunability of inductance and quality factor of AIs.

- They can be affected by supply voltage fluctuations: Although the characteristics of spiral inductors are not dependent on the supply voltage, unfortunately, the same is not valid for AIs since DC biasing conditions are directly affected by supply voltage fluctuation. Some of the fluctuation effects can be reduced by using less sensitive topologies and preferring replica-biasing methods [19].

#### 2.3. Fundamentals of Gyrator-C-Based AIs

Gyrator-C-based AIs can be examined under two main categories: single-ended and differential. These groups can also be called grounded and floating, respectively. In this section, the working principles of grounded active inductors (GAIs) and floating active inductors (FAIs) are investigated. In order to understand their working principles more easily, the behavior of lossless AI circuits will be discussed in Sections 2.3.1 and 2.3.3. Then the effect of parasitic resistances and capacitances will be shown in Sections 2.3.2 and 2.3.4.

#### 2.3.1. Lossless Gyrator-C-Based GAIs

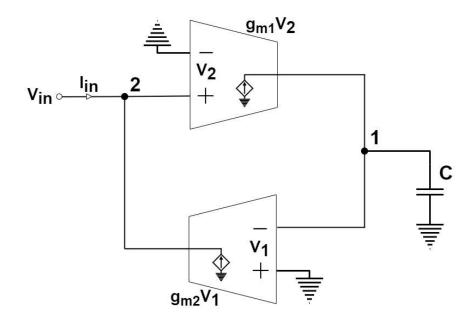

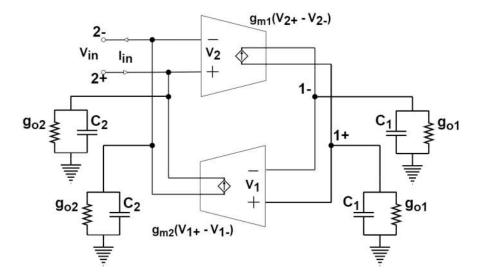

Systems with two back-to-back transconductance stages and a capacitor connected to one of the ports are called gyrator-C networks. As shown in Figure 2.1, one of the transconductance stages is positive while the other one is negative. When the

input and output impedances of the transconductance stages are ignored, it is called lossless gyrator-C networks. Even though the lossless gyrator-C network does not exist in practice due to parasitic capacitances and finite conductances of MOS transistors, it is examined to understand the working principle of the gyrator-C based AIs.

Figure 2.1. The scheme of lossless gyrator-C-based GAI.

The admittance seen looking at port 2 of the gyrator-C network can be expressed by

$$Y_{in} = \frac{1}{Z_{in}} = \frac{I_{in}}{V_2} = \frac{1}{s(\frac{C}{g_{m1}g_{m2}})},$$

(2.1)

which evidences that gyrator-C network has an inductive behaviour with the inductance of

$$L = \frac{C}{g_{m1}g_{m2}}. (2.2)$$

As seen in Equation (2.2), the inductance value of gyrator-C based AIs is proportional to the load capacitance and inversely proportional to the transconductances of the

MOS transistors. By adjusting these parameters, tunable inductive behavior can be obtained as an important property of AIs.

As shown in Figure 2.1, negative and positive transconductance stages are needed to implement the gyrator-C network. A common source amplifier can be used for a negative transconductance stage, while common-gate, common-drain, and differential-pair amplifiers can be used for positive transconductance stages.

#### 2.3.2. Lossy Gyrator-C-Based GAIs

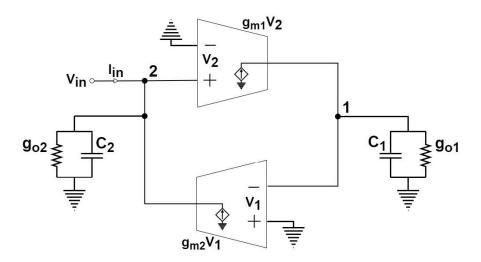

Although lossless inductance was examined in the previous section, AIs encountered in practice are lossy due to the parasitic resistance and capacitance of transistors. The block diagram of lossy gyrator-C GAI is pictured in Figure 2.2.

Figure 2.2. The scheme of lossy gyrator-C-based GAI.

The admittance seen looking at port 2 of the lossy gyrator-C network can be expressed by

$$Y_{in} = \frac{1}{Z_{in}} = \frac{I_{in}}{V_2} = sC_2 + g_{o2} + \frac{1}{s(\frac{C_1}{g_{m1}g_{m2}}) + \frac{g_{o1}}{g_{m1}g_{m2}}},$$

(2.3)

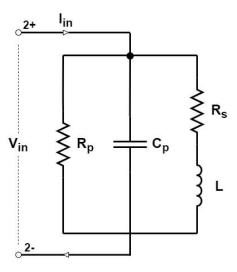

while the RLC network equivalent of the lossy gyrator-C GAI is shown in Figure 2.3. The parameters of the RLC system defined by Equation (2.3) can be represented by

$$R_{p} = \frac{1}{g_{o2}},$$

$$R_{s} = \frac{g_{o1}}{g_{m1}g_{m2}},$$

$$C_{p} = C_{2},$$

$$L_{act} = \frac{C_{1}}{g_{m1}g_{m2}}.$$

(2.4)

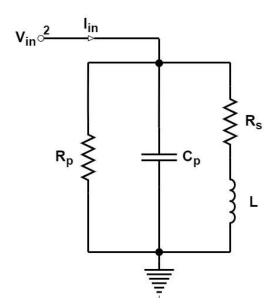

Figure 2.3. The equilarent RLC network of the lossy gyrator-C-based GAI.

As seen in Equation (2.4), ohmic loss of the AI can be reduced by maximizing  $R_p$  and minimizing  $R_s$  to obtain high-quality inductive behavior. For this purpose, in the literature, Q-enhancement techniques are applied to the inductors [17]. Q-enhacement techniques are used in the designs presented in Chapter 5 and Chapter 6.

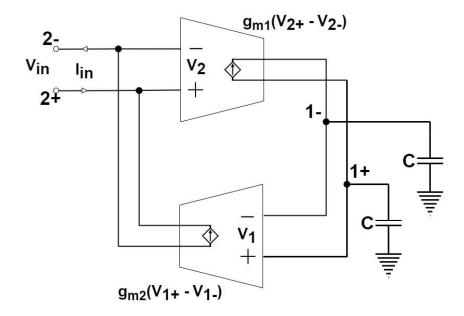

#### 2.3.3. Lossless Gyrator-C-Based FAIs

Gyrator-C networks are called gyrator-C FAIs when both terminals are not connected to the ground or power supply. Floating inductors are obtained by making

the transconductance stages of the grounded inductors differential as demonstrated in Figure 2.4.

Figure 2.4. The scheme of lossless gyrator-C-based FAI.

The admittance seen looking at port 2 of the lossless gyrator-C network is slightly different than the grounded counterpart as

$$Y_{in} = \frac{1}{Z_{in}} = \frac{I_{in}}{V_{in2}^{+} - V_{in2}^{-}} = \frac{1}{s(\frac{2C}{q_{m1}q_{m2}})},$$

(2.5)

which shows that gyrator-C network has a floating inductance expressed by

$$L = \frac{2C}{g_{m1}g_{m2}}. (2.6)$$

The few advantages of FAIs over grounded ones can be listed as follows:

- The voltage swing of floating inductors is twice that of the grounded counterparts thanks to their differential configuration.

- DC voltage offset between two ports of the AIs are eliminated.

- Differentiating the structure of the AI circuit reduces harmonic distortions.

- They are more suitable for use with noisy digital circuits since their differential structures lessen the impact of common-mode noise.

#### 2.3.4. Lossy Gyrator-C-Based FAIs

The system diagram of lossy gyrator-C FAI is depicted in Figure 2.5.

Figure 2.5. The scheme of lossy gyrator-C-based FAI.

These circuits are similar in behavior to the lossy grounded inductors. The admittance equation becomes:

$$Y_{in} = \frac{1}{Z_{in}} = \frac{I_{in}}{V_{in2}^{+} - V_{in2}^{-}} = s\frac{C_2}{2} + \frac{g_{o2}}{2} + \frac{1}{s(\frac{C_1}{2g_{m1}g_{m2}}) + (\frac{g_{o1}}{2g_{m1}g_{m2}})}.$$

(2.7)

The parameters of the equivalent RLC circuit of the lossy grounded inductor, depicted in Figure 2.6, can be represented by

$$R_{p} = \frac{2}{g_{o2}},$$

$$R_{s} = \frac{g_{o1}/2}{g_{m1}g_{m2}},$$

$$C_{p} = \frac{C_{2}}{2},$$

$$L_{eq} = \frac{C_{1}/2}{g_{m1}g_{m2}}.$$

(2.8)

Figure 2.6. The equivalent RLC network of the lossy gyrator-C-based FAI.

Unlike Equation (2.4), the number 2 is added to the RLC parameters in Equation (2.8) due to the differential structure of the floating inductor. Since this circuit also has a differential structure, it has the advantages mentioned in Section 2.3.3.

#### 2.4. Performance Parameters of AIs

The most significant figure-of-merits that offer quantitative measurements of AIs performance are examined in this section.

- Inductance Tunability: AIs are useful circuits for systems where large inductance tuning range is required, such as filters, phase-locked loops, and voltage-controlled oscillators. According to Equation (2.2), it is possible to control the inductance of a gyrator-C AI by varying the transconductances of the MOS transistor and the load capacitance. The former method can be used as coarse tuning method since the transconductances of the transistors have large tuning range. The latter one can be used for as the fine tuning mechanism of the inductance since varactors have a small tuning range. Tuning range of the load capacitor can be increased by using digital control, but it can complicate the system as the chip will need a digital interface.

- Quality Factor: The quality factor (Q), independent of voltage and current in CMOS spiral inductors, depends on the voltage and current swing in AIs. For linear inductors, including AIs, Q value can be calculated as

$$Q = \frac{Im[Z]}{Re[Z]}. (2.9)$$

As seen in [10], for conventional gyrator-C based active inductors, there are two main ways of increasing Q: increasing  $g_{o1}$  or increasing transconductance values  $g_{m1}$  and  $g_{m2}$ . The transconductance values can be directly adjusted by controlling the bias currents of the circuit, but this method is not usually preferred since it changes the inductance value of the circuit at the same time. On the other hand, different techniques have been proposed to increase  $g_{o1}$ . This value can be increased by choosing transistors with large lengths, or cascode devices are can be added to the circuit. Moreover, in some studies, negative resistance circuits are also added to increase the effective  $g_{o1}$ .

• Frequency Range: The inductive characteristic of a lossy gyrator-C AI is limited to a certain frequency range. To understand the frequency response of the AI, the RLC equivalent equation can be studied as

$$Z = \left(\frac{R_s}{C_p L}\right) \frac{s \frac{L}{R_s} + 1}{s^2 + s\left(\frac{1}{R_p C_p} + \frac{R_s}{L}\right) + \frac{R_p + R_s}{R_p C_p L}},\tag{2.10}$$

$$\omega_p \approx \sqrt{\frac{1}{LC_p}} = w_o. \tag{2.11}$$

Z also has a zero at frequency

$$\omega_z = \frac{R_s}{L} = \frac{g_{o1}}{C_1}. (2.12)$$

As seen in Equation (2.11) and Equation (2.12), upper bound of the inductive frequency range of the AI is determined by the self-resonant frequency  $\omega_o$  while its lower bound is limited by  $\omega_z$ . To optimize the frequency range of an AI for a desired inductance value, both  $R_s$  and  $C_p$  should be reduced.

- Power consumption: In gyrator-C AIs, dc power is consumed to obtain transconductance from the MOS transistors while CMOS spiral inductors do not consume any static power. Because the transconductance and inductance values are inversely proportional, high inductance values can be achieved with low dc currents. Thus, dc power consumption is not a big issue for AIs.

- Noise: As different from CMOS spiral inductors, AIs show high noise behavior since they contain MOS transistors. In [10], detailed noise analysis of gyrator-C networks are included. For the sake of simplicity, detailed information is not included in this thesis. In [36], PMOS transistors are preferred for cascode structure to reduce the noise. Moreover, they can eliminate the nonlinear body effect since they can be produced in separate n-wells.

- Linearity and signal sensitivity: The large voltage swing on the AI can change the small signal characteristics of the MOS transistors in the gyrator-C network. It can even cause the transistors to go out of saturation when the swing is large enough. This situation causes the AI to exhibit nonlinear behavior so that its critical parameters such as inductance value and quality factor change according to the voltage swing on it. This problem is one of the important reasons that prevent the AI from being used widely.

- PVT variation sensitivity: Process, supply voltage and temperature variation can directly affects the dc biasing of the MOS transistors in AIs. Hence, the figure-

of-merits of the AI, especially the inductance value and the quality factor, have deteriorated. Constant  $g_m$  biasing techniques can be applied to minimize the supply sensitivity of the circuit. On the other hand, corner analysis and Monte Carlo analysis can be made for process and temperature variation analysis. According to these simulations, design parameters can be tuned to achieve minimal variation in the circuit operation. Moreover, tunable parameters can also be effective to reduce the effect of these variations.

#### 2.5. Chapter Summary

After a discussion of the benefits and drawbacks of spiral inductors and AIs, fundamental concepts of gyrator-C-based AI circuits has been presented. It was demonstrated that gyrator-C networks may be used to make both grounded and floating AIs. Then, performance parameters of AIs have been investigated to understand what to expect from a well designed circuit.

#### 3. PROPOSED ACTIVE INDUCTOR CIRCUITS

In this chapter, novel positive and negative gyrator-C-based AI circuits are presented. Then, some of the proposed circuits are biased so that their transistors operate at the saturation region. Properly biased circuits can be utilized in various CMOS implementations. To demonstrate that they are suitable circuits in IC applications, the proposed circuit in Section 3.1.1 is used for the LC-VCO design presented in Chapter 4.

#### 3.1. Proposed Core Circuits

Novel positive and negative gyrator-C-based AI circuits are introduced in this section. Core circuit schematics of the proposed AIs are demonstrated, and their small signal equations are briefly explained.

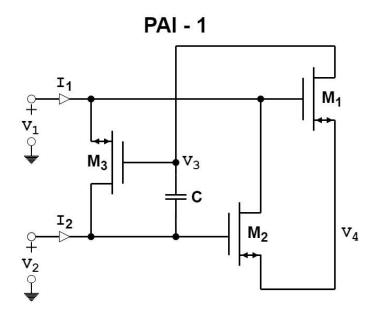

#### 3.1.1. Positive Active Inductor - 1 (PAI-1)

Figure 3.1 represents the first proposed positive active inductor circuit, PAI-1. The double arrows mean the transistors can be both NMOS or PMOS. Kirchoff current law (KCL) equations of the small signal representation of the circuit PAI-1 are shown as

$$-I_{1} - g_{m3}(V_{3} - V_{1}) + g_{m2}(V_{2} - V_{4}) = 0,$$

$$-I_{2} - g_{m3}(V_{3} - V_{1}) + sC(V_{2} - V_{3}) = 0,$$

$$g_{m1}(V_{1} - V_{4}) + sC(V_{3} - V_{2}) = 0,$$

$$-g_{m1}(V_{1} - V_{4}) - g_{m2}(V_{2} - V_{4}) = 0.$$

(3.1)

Figure 3.1. The core schematic of the proposed PAI-1 circuit.

When the KCL equations in Equation (3.1) are solved, the equivalent inductance of the proposed circuit PAI-1 can be calculated as

$$L = \frac{C}{(g_{m3})^2}, \quad \text{if} \quad g_{m3} = \frac{g_{m1}g_{m2}}{(g_{m1} + g_{m2})}.$$

(3.2)

As seen in Equation (3.2),  $g_m$  values of each transistor should be adjusted together to not disturb the inductive behavior. Further, the inductance can also be varied by changing the capacitor C.

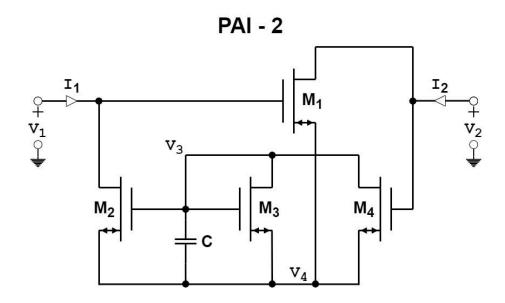

#### 3.1.2. Positive Active Inductor - 2 (PAI-2)

The core circuit of the proposed active inductor PAI-2 is depicted in Figure 3.2, which includes four transistors and one capacitor.

Figure 3.2. The core schematic of the proposed PAI-2 circuit.

KCL small signal equations of PAI-2 circuit can be expressed as

$$-I_{1} + g_{m2}(V_{3} - V_{4}) = 0,$$

$$-I_{2} + g_{m1}(V_{1} - V_{4}) = 0,$$

$$g_{m3}(V_{3} - V_{4}) + g_{m4}(V_{2} - V_{4}) + sC(V_{3} - V_{4}) = 0,$$

$$-g_{m1}(V_{1} - V_{4}) - g_{m2}(V_{3} - V_{4}) - g_{m3}(V_{3} - V_{4}) - g_{m4}(V_{2} - V_{4}) + sC(V_{4} - V_{3}) = 0.$$

$$(3.3)$$

According to the individual equations in Equation (3.3), the inductance value of the proposed circuit PAI-2 can be represented by

$$L = \frac{C}{g_{m2}g_{m4}}, \quad \text{if} \quad g_{m1}g_{m3} = g_{m2}g_{m4}. \tag{3.4}$$

The inductance of circuit PAI-2 can be tuned by adjusting both  $g_{m2}$  and  $g_{m4}$  values of the transistors. In order not to disturb the inductive behavior,  $g_{m1}$  and  $g_{m3}$  values should be increased at the same time.

#### 3.1.3. Negative Active Inductor - 1 (NAI-1)

Figure 3.3 represents the first proposed negative active inductor circuit, NAI-1. KCL small signal equations of NAI-1 circuit can be stated as

$$-I_{1} + g_{m1}(V_{3} - V_{4}) = 0,$$

$$-I_{2} - g_{m2}(V_{1} - V_{2}) + g_{m3}(V_{1} - V_{4}) = 0,$$

$$g_{m2}(V_{1} - V_{2}) + sC(V_{3} - V_{4}) = 0,$$

$$-g_{m1}(V_{3} - V_{4}) - g_{m3}(V_{1} - V_{4}) + sC(V_{4} - V_{3}) = 0.$$

(3.5)

Figure 3.3. The core schematic of the proposed NAI-1 circuit.

When the KCL equations in Equation (3.5) are solved, the equivalent negative inductance of the proposed circuit NAI-1 can be represented by

$$L = -\frac{C}{g_{m1}g_{m2}}. (3.6)$$

Transconductance values  $g_{m1}$ ,  $g_{m2}$  and the capacitor C can control the inductance value of the circuit NAI-1. All three parameters can be used for tuning since there is no if condition for the inductive behavior of the proposed circuit.

#### 3.1.4. Negative Active Inductor - 2 (NAI-2)

Figure 3.4 shows the schematic of the proposed negative active inductor circuit, NAI-2. KCL small signal equations of the proposed NAI-2 circuit can be described as

$$-I_{1} - g_{m1}(V_{3} - V_{1}) = 0,$$

$$-I_{2} + g_{m3}(V_{3} - V_{4}) = 0,$$

$$g_{m1}(V_{3} - V_{1}) + g_{m2}(V_{2} - V_{4}) + sC(V_{3} - V_{4}) = 0,$$

$$-g_{m3}(V_{3} - V_{4}) - g_{m2}(V_{2} - V_{4}) + sC(V_{4} - V_{3}) = 0.$$

(3.7)

Figure 3.4. The core schematic of the proposed NAI-2 circuit.

According to the equations in Equation (3.7), the negative inductance of the circuit NAI-2 can be expressed by

$$L = -\frac{C}{g_{m2}g_{m3}}, \quad \text{if} \quad g_{m1} = \frac{g_{m2}g_{m3}}{g_{m2} + g_{m3}}.$$

(3.8)

As seen in Equation (3.8), the negative inductance value of the circuit NAI-2 can be tuned by changing the capacitor C and the transconductances of the MOS transistors  $M_2$  and  $M_3$  if  $g_{m_1}$  meets the requirement of the given condition.

#### 3.1.5. Negative Active Inductor - 3 (NAI-3)

Figure 3.5 represents a novel negative active inductor circuit, NAI-3. KCL equations of the small signal equivalent of the circuit NAI-3 can be written as

$$-I_{1} + g_{m2}(V_{3} - V_{2}) = 0,$$

$$-I_{2} - g_{m2}(V_{3} - V_{2}) - g_{m3}(V_{1} - V_{2}) + sC(V_{2} - V_{3}) = 0,$$

$$g_{m1}(V_{1} - V_{4}) + sC(V_{3} - V_{2}) = 0,$$

$$-g_{m1}(V_{1} - V_{4}) + g_{m3}(V_{1} - V_{2}) = 0.$$

(3.9)

Figure 3.5. The core schematic of the proposed NAI-3 circuit.

From the Equation (3.9), the negative inductance value of the circuit NAI-3 can be derived as

$$L = -\frac{C}{q_{m2}q_{m3}}. (3.10)$$

As seen in Equation (3.9), the circuit NAI-3 has an inductive behaviour depending on the capacitor C and the transconductances of the MOS transistors M2 and M3. Since there is no conditional statement of its inductive behaviour, it is possible to tune the inductance directly without affecting the inductive characteristics of the circuit.

# 3.1.6. Negative Active Inductor - 4 (NAI-4)

Figure 3.6 shows a proposed novel negative active inductance circuit, NAI-4. KCL small signal equations of NAI-4 circuit can be described as

$$-I_{1} + g_{m2}(V_{3} - V_{2}) = 0,$$

$$-I_{2} + g_{m2}(V_{3} - V_{2}) + g_{m3}(V_{2} - V_{4}) + sC(V_{2} - V_{3}) = 0,$$

$$g_{m1}(V_{1} - V_{4}) + sC(V_{3} - V_{2}) = 0,$$

$$-g_{m1}(V_{1} - V_{4}) - g_{m3}(V_{2} - V_{4}) = 0.$$

(3.11)

Figure 3.6. The core schematic of the proposed NAI-4 circuit.

According to the equations in Equation (3.11), the inductance of the proposed circuit NAI-4 can be expressed by

$$L = -\frac{C(g_{m1} + g_{m3})}{g_{m1}g_{m2}g_{m3}}. (3.12)$$

which shows that the inductance of the circuit NAI-4 can be tuned by adjusting the  $g_{m1}$ ,  $g_{m2}$  and  $g_{m3}$  values.

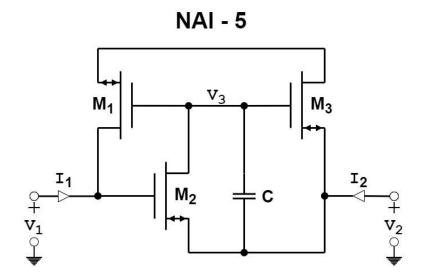

# 3.1.7. Negative Active Inductor - 5 (NAI-5)

Figure 3.7 represents the negative active inductance circuit, NAI-5. KCL small signal equations of NAI-5 circuit can be stated as

$$-I_{1} + g_{m1}(V_{3} - V_{4}) = 0,$$

$$-I_{2} - g_{m2}(V_{1} - V_{2}) - g_{m3}(V_{3} - V_{2}) + sC(V_{2} - V_{3}) = 0,$$

$$g_{m2}(V_{1} - V_{2}) + sC(V_{3} - V_{2}) = 0,$$

$$-g_{m1}(V_{3} - V_{4}) + g_{m3}(V_{3} - V_{2}) = 0.$$

(3.13)

Figure 3.7. The core schematic of the proposed NAI-5 circuit.

When the small signal KCL equations in Equation (3.13) are solved, the equivalent inductance of the circuit NAI-5 can be calculated as

$$L = -\frac{C}{q_{m2}q_{m3}}. (3.14)$$

which demonstrates that the inductance value NAI-5 circuit can be linearly controlled by adjusting the  $g_{m2}$  and  $g_{m3}$  values. Moreover, inductance tuning does not affect the inductive characteristics of the circuit since there is no conditional statement in Equation (3.14).

# 3.2. Biased Circuit Configurations

This chapter presents biased versions of several of the core circuits proposed in Section 3.1.

# 3.2.1. Biased Version of PAI-1

Figure 3.8 depicts the biased configuration of the core circuit PAI-1 presented in Section 3.1.1. For DC shifting purpose, diode connected NMOS transistors  $M_4$  and  $M_5$  added to the circuit in Figure 3.1. Then, bias currents  $I_{b1-4}$  are added to provide required tail currents. For this circuit,  $M_1$  and  $M_2$  transistors are selected NMOS type while  $M_3$  is chosen as PMOS type. The complementary version of this configuration can also be biased correctly according to the requirements of the system to be used.

Figure 3.8. The schematic of the biased version of PAI-1 circuit.

Although the circuit given in Figure 3.8 has floating characteristics, there is a DC offset between its two terminals. To eliminate the DC offset and improve the THD behavior of the circuit, this structure can be joined together with its duplicated version to create fully differential topology. This technique is used in the LC-VCO design presented in Chapter 4.

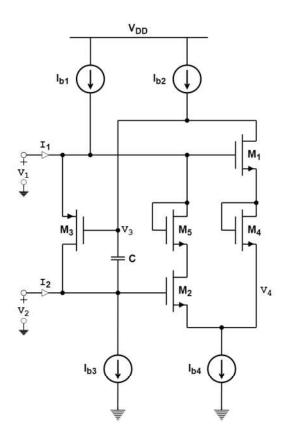

# 3.2.2. Biased Version of NAI-5

Figure 3.9 demonstrates the biased version of the NAI-5 core circuit given in Figure 3.7. All transistors are chosen as NMOS type in this configuration, but different transistor types can be selected if needed. For example, the case where all transistors are PMOS can also be properly biased. Moreover, bias currents I<sub>b1-3</sub> are added to provide required tail currents.

Figure 3.9. The schematic of the biased version of NAI-5 circuit.

Figure 3.10 illustrates the fully differential form of the biased NAI-5 circuit shown in Figure 3.9, which is obtained by connecting two NAI-5 circuits from their  $v_2$  nodes.

Figure 3.10. The schematic of the fully differential NAI-5 circuit.

For the fully differential version, the equivalent inductance equation given (3.14) is revised as follows

$$L = -\frac{2C}{g_{m2}g_{m3}}. (3.15)$$

# 3.3. Chapter Summary

This chapter has proposed gyrator-C-based PAI and NAI circuits, as well as biased configurations of several of them. Moreover, small signal equations and corresponding inductance values of the suggested circuit have been included, along with summary comments concerning the circuit equations. As seen in Chapter 4, the proposed AI architectures in this chapter are compatible with CMOS implementations.

# 4. WIDE-TUNABLE LC-VCO DESIGN WITH A NOVEL ACTIVE INDUCTOR

# 4.1. Chapter Introduction

Voltage-controlled oscillators (VCOs) are critical components of modern communication and signal processing systems. They are crucial for Phase-Locked Loop (PLL) circuits used for synchronization and frequency demodulation. PLLs are generally fully integrated structures that try to lock onto an off-chip reference clock. LC-VCOs are often preferred in such systems due to low phase noise performance [37]. However, CMOS implementations of LC-VCOs require spiral inductors, which consume a significant amount of silicon area. Additionally, these structures lack a wide tuning range. These limitations of spiral inductors-based VCO architectures have prompted researchers to look for alternatives. In this direction, apart from the ring oscillator-based architectures mentioned in [38,39], LC-VCO architectures employing AIs rather than spiral inductors are described as in [20–22].

Als outperform spiral inductors in terms of tunable factors such as inductance value and quality factor (Q). Additionally, they occupy considerably less silicon area than spiral inductors, making them significantly more cost-effective. On the other hand, they cannot meet spiral inductors' phase noise performance and consume static current [10]. The literature involves a number of AI structures based on a variety of different principles [23–27]. Among these topologies, MOS-only gyrator-C-based topologies have risen to prominence due to their low number of transistors and ability to achieve high frequencies [28, 29].

In this chapter, a low-supply LC-VCO based on a novel gyrator-C FAI is designed. It has a wide frequency range due to the tuning mechanism that takes advantage of the FAI's tunability. It is unsuitable for RF applications due to its poor phase noise performance compared to spiral inductors. It is, however, a circuit capable of locating

itself in areas where phase noise is not a significant factor. For instance, its low supply operation and wide tuning range make it an excellent choice for PLLs in digital circuits commonly designed today.

The remainder of this chapter will proceed in the following manner: Section 4.2 introduces the proposed FAI. The frequency response and bias conditions of the circuit are examined, and the design parameters are taken into account while determining the inductor parameters. Section 4.3 discusses the design process for a wide-tuning-range LC-VCO based on the suggested FAI. Section 4.4 presents the Cadence Design Suite post-layout simulation results for the designed oscillator. Additionally, the mechanism that enables wide-tuning is described, as are the oscillator's benefits and drawbacks. Finally, the study was concluded, and future work is discussed in Section 4.5.

#### 4.2. Proposed FAI Circuit

The main principle in generating an AI is to obtain a circuit that satisfies the following two-port short circuit admittance matrix equation:

$$\begin{bmatrix} I_1 \\ I_2 \end{bmatrix} = \frac{1}{sL_{\text{act}}} \begin{bmatrix} 1 & -1 \\ -1 & 1 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix}, \tag{4.1}$$

where  $L_{\rm act}$  is the equivalent inductance value of the AI. In this chapter, we will focus on gyrator-C based architecture, which constitutes a significant part of the proposed AIs in the literature [9, 15, 21, 28, 29]. Among the gyrator-C-based applications, the MOSFET-C approach was preferred considering high-frequency performance and the number of transistors required to implement it.

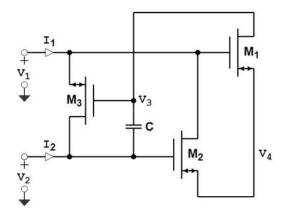

The core circuit of the proposed AI, computed using the design automation method [30, 31], is illustrated in Figure 4.1. The proposed circuit has floating inductance behavior, which is a valuable feature that expands the circuit's application area. The bidirectional arrows indicate that the transistors in the core circuit may be

either PMOS or NMOS as both transistor types have an identical small-signal equivalent model. Considering this information, it may seem possible to create  $2^n$  different circuits; however, some are not applicable due to bias constraints. As a result, one or more circuits can be designed with the same small-signal characteristics of the core circuit and can be properly biased.

Figure 4.1. The core circuit of the proposed AI.

Replacing MOS transistors with their small-signal models, and when the KCL equations of the AI circuit are solved, the equivalent inductance of the proposed circuit can be calculated as

$$L_{\text{act}} = \frac{C}{(g_{\text{m3}})^2}, \quad \text{if} \quad g_{\text{m3}} = \frac{g_{\text{m1}}g_{\text{m2}}}{(g_{\text{m1}} + g_{\text{m2}})}.$$

(4.2)

which shows that  $g_m$  values of the transistors  $M_1$ ,  $M_2$ , and  $M_3$  should be adjusted together to avoid disturbing the inductive behavior.

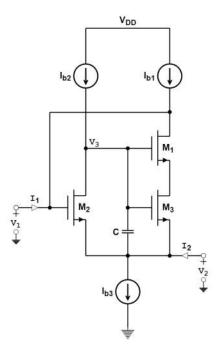

The proposed core circuit must be properly biased for the actual design so that transistor behavior similar to that of the small-signal representation is obtained. Thus, the transistor sizes and tail currents should be adjusted to guarantee that all transistors operate in saturation within the specified operating range. For this design,  $M_1$  and  $M_2$  transistors are chosen as NMOS due to the high speed of the NMOS type. Then,

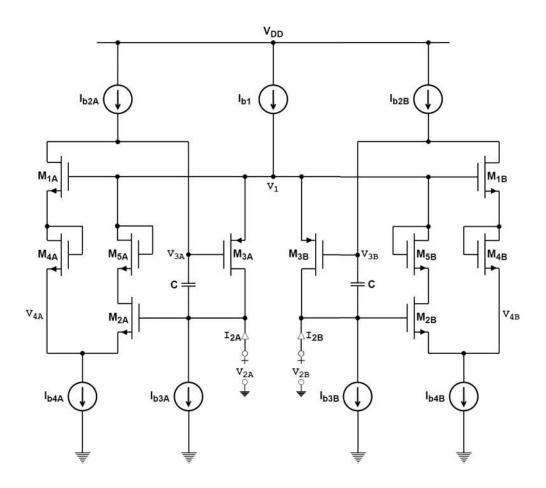

$M_3$  transistor is selected as PMOS due to proper bias need. Figure 4.2 represents the biased version of the proposed circuit in differential (floating) form. While the proposed core circuit is a floating inductor, an AI is created by joining two core circuits at their  $V_1$  nodes. This eliminates DC offset between the inductor's ports. Additionally, the differential circuit performs better in terms of the percentage total harmonic distortion (%THD) than the core circuit. Transistors  $M_1$ ,  $M_2$ , and  $M_3$  are the same as shown in Figure 4.1. Moreover, transistors  $M_4$  and  $M_5$  are added to the circuit for DC shifting purposes for proper biasing.

Figure 4.2. The biased version of the proposed AI circuit.

Taiwan Semiconductor Manufacturing Company (TSMC) 65 nm process design kit (PDK) with a core supply voltage of 1.2 V was preferred in this study. This supply voltage is appropriate in terms of power consumption ( $P_{\rm dc}$ ) and the lifetime of the

transistors. On the other hand, however, it restricts the number of transistors that can be stacked. As seen in Figure 4.2, there are three distinct lines between power and ground where transistors are stacked: the line of  $M_1$ ,  $M_4$ ,  $I_{b2}$ ,  $I_{b4}$ ; the line of  $M_2$ ,  $M_5$ ,  $I_{b1}$ ,  $I_{b4}$ ; and the line of  $M_3$ ,  $I_{b1}$ ,  $I_{b3}$ . Given that each of the current sources from  $I_{b1}$  to  $I_{b4}$  are implemented using a single transistor current mirror, the total number of stacked transistors for each line is not more than four, which is suitable for low voltage operation.

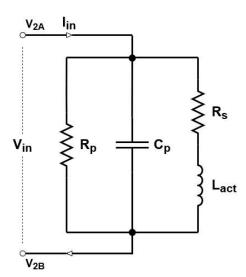

The parasitic capacitances and finite output impedances of the transistors are not taken into account when obtaining Equation (4.2). However, especially the large size of the transistor strengthens the parasitic effects. This causes the designed circuit to deviate from the calculated inductive behavior. In the useful frequency range, the behavior of the designed active inductor fits to the model in Figure 4.3. The computed corresponding values are listed in Section 4.3.

Figure 4.3. The equivalent RLC network of the lossy gyrator-C-based FAI.

The second chapter of [10] delves into small-signal analyses of gyrator-C networks and the parasitic effects on their inductive behavior. While designing the active AI for this design, attention will be paid to the points highlighted in [10].

In the proposed system shown in Figure 4.1, the main reason for  $R_p$  is the impedance seen from  $V_2$  node when  $V_1$  node is grounded, that is, the output impedance of the transistor  $M_3$ . Thus, in applications requiring a high-Q value, the  $R_p$  value can be enhanced by reducing the current flowing through  $M_3$ . On the other hand, decreasing current can reduce the  $g_{m3}$  value, hence raising the equivalent inductance of the circuit. Therefore, in circuits where low inductance is required, a trade-off between lowering the inductance value and increasing the Q value may occur.

The value of  $R_s$  is another factor that distracts AIs from their ideal behavior. The  $R_s$  value is inversely proportional to the  $g_{m3}$  value and the impedance seen from  $V_1$  node. The other non-ideal component of the AI is  $C_p$  capacitance.  $C_p$  can be defined as the equivalent capacitor from AI input to the ground.

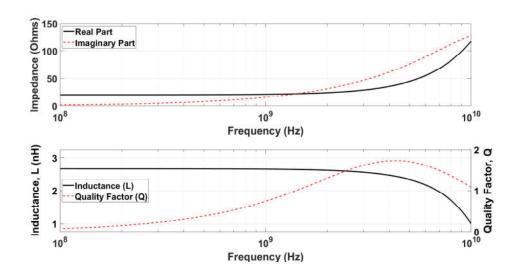

As highlighted above, a change to improve one of the non-ideal components of AIs may affect other parts. Thus, it is required to examine all parameters and improve in an iterative manner. This situation necessitates the use of advanced simulation environments. In this study, the Spectre Simulation Platform is used for circuit optimization. The impedance, inductance value, and quality factor graphs of the designed inductor circuit are given in Figure 4.4. The inductance values are calculated by taking the derivative of the imaginary part of the impedance graph. The quality factor is obtained by dividing the imaginary part of the impedance value by the real part.

# 4.3. LC-VCO Design

This Section explains the design of an LC-VCO circuit with the novel FAI suggested in the preceding section. While Section 4.3.1 discusses the preferred LC-VCO topology, Section 4.3.2 discusses the design approach and issues to consider throughout the design.

Figure 4.4. Characteristics of the proposed FAI.

# 4.3.1. Circuit Topology

The conventional LC-VCO structures include four categories of devices: inductors, capacitors, cross-coupled transistors, and current sources. Numerous alternative topologies have been proposed depending on the location of the inductors, types of cross-coupled transistors, and tail currents. To keep the chapter short, a comparison of various VCO topologies is not discussed here. Detailed information about comparing several architectures can be found in [40–42]. The suggested design employs a bottom-biased NMOS cross-coupled LC-VCO topology due to its superior high-frequency behavior and compatibility with AI applications as depicted in Figure 4.5.

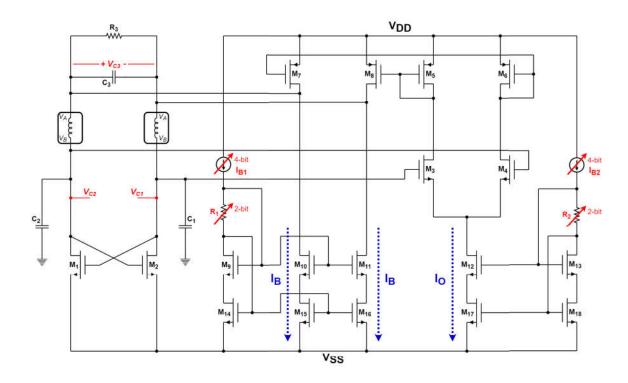

The detailed schematic of the designed LC-VCO is presented in Figure 4.6. Transistors  $M_{1A,B}-M_{5A,B}$  form the biased version of the proposed FAI, and transistors  $M_6$ ,  $M_{7A,B}$  and  $M_{8A,B}$  correspond to the current sources  $I_{b1}$ ,  $I_{b2A,B}$ , and  $I_{b3A,B}$ , respectively, as illustrated in Figure 4.2. As different from the Figure 4.2, cross-coupled transistors  $M_9$  and  $M_{10}$  are inserted between the FAI ports and the current sink transistor  $M_{11}$ . As illustrated in Figure 4.6, the total number of stacked transistors in any line does not exceed four after the addition of cross-coupled transistors. This demonstrates that the final design will also work in a low-supply environment.

Figure 4.5. Bottom-biased NMOS cross-coupled LC-VCO scheme.

#### 4.3.2. Design Procedure

In this section, an LC-VCO will be designed, working at 2.4 GHz–3.8 GHz with a  $V_{\rm DD}=1.2$  V supply voltage. In low-voltage systems, it is necessary to pay close attention to the number of stacked transistors to prevent headroom issues. As explained in Section 4.2, the proposed FAI is suitable for operation at low supply voltage. Due to the high operating frequency, short channel devices manufactured in the TSMC 65 nm technology were chosen for the design. Moreover, by designing a system in which both varactors and tail currents can control the operating frequency, the oscillator is provided to cover a wide frequency range. The remainder of this section describes the procedure for selecting VCO design parameters.

When designing classical LC-VCO structures with spiral inductors, the needed tail current and inductor  $R_p$  value are determined by considering the power budget and desired output voltage swing. It is vital to avoid exceeding a particular output swing in these systems, as there is a risk of cross-coupled transistors entering the

triode region. At this point, the FAI-based oscillator architecture used in this study is distinct from conventional structures. First, because the dynamic range of FAIs is already limited to a few tens of mV, it will not be sufficient to affect cross-coupled transistors. Secondly, as illustrated in Figure 4.6, the tail current of the oscillator affects the characterization of the inductor since it is also the bias current of the FAI. Thus, the required tail current and  $R_p$  value cannot be determined independently of each other. As a result, the inductance value required to achieve the target oscillation frequency will be determined first. Then, when the FAI reaches the appropriate inductance value at the defined frequencies, the required  $R_p$  value is determined to ensure that it does not exceed the dynamic range of the FAI.

Figure 4.6. The detailed schematic of the designed LC-VCO.

The oscillation frequency equation of an LC-tank is as follows:

$$f_{\rm osc} = \frac{1}{2\pi\sqrt{L_1C_1}},$$

(4.3)

while  $L_1$  and  $C_1$  are equivalent inductance and capacitance values of the LC-tank. When the equivalent capacitance of the LC-tank is assumed to be 1 pF, an inductance of around 2.8 nH is required for a 3 GHz oscillation. After allocating 300 fF of the tank's 1 pF equivalent capacitance to the varactor, the remaining part can be allocated to the FAI capacitances in two 350 fF halves as illustrated in

$$C_1 = C_{\text{var}} + 2C_{\text{ind}},\tag{4.4}$$

while  $C_{var}$  represents the capacitance of the varactor and  $C_{ind}$  represents the capacitance seen from the ports of each FAI.

Then, considering Equation (4.2), the value of  $g_{m3}$  should be roughly 9 mS to achieve the desired inductance value in the proposed FAIs. It is sufficient to flow 1 mA current through  $M_{3A,B}$  transistors to obtain desired  $g_{m3}$  value. The high current flowing through the  $M_{3A,B}$  transistor reduces the  $R_p$  value of the FAI, hence the Q value of the inductor. However, this is not a problem for the LC-VCO design, as the output swing must be kept low due to the dynamic range constraint of the FAI.

Table 4.1. Parameters of the designed FAI for the  $Cluster_{100}$  case.

| Parameter Type                       | Value             |

|--------------------------------------|-------------------|

| Inductance, $L_1$ (= $L_{act}$ )     | 2.55 nH           |

| Quality Factor, $Q$                  | 1.52              |

| Parallel Resistance, R <sub>p</sub>  | 567 Ω             |

| Parallel Capacitance, C <sub>p</sub> | 350 fF            |

| Series Resistance, R <sub>s</sub>    | $12.17~\Omega$    |

| Power Consumption $(P_{dc})$         | $9.6~\mathrm{mW}$ |

The approximate calculations described previously have been taken into account and the FAI has been designed with the parameters necessary to achieve the desired oscillation conditions. The bias current of the FAI is tuned in the designed LC-VCO to cover many frequency ranges referred to as clusters. As a result, the FAI's characteristics may vary between clusters. The parameters associated with the  $Cluster_{100}$  state, which we can define as the nominal case, are listed in Table 4.1. The inductance  $(L_1)$  and quality factor (Q) values in this table are for the nominal oscillation frequency of 3.105 GHz. Additionally, the inductor's impedance-frequency responses for the nominal case are shown in Figure 4.4 in Section 4.2.

After obtaining the basic parameters related to the FAI, the design phase of the cross-coupled transistors was started. In order to guarantee that the oscillation will occur despite the non-ideal effects in the devices, the transconductance values of the cross-coupled transistors should be determined as follows:

$$g_{\rm m9,10} \ge \frac{3}{R_{\rm p}}.$$

(4.5)

Figure 4.7. The layout of the designed LC-VCO.

Table 4.2. Aspect ratios of the transistors in the designed LC-VCO shown in Figure 4.6.

| Transistor                       | Width (W)             | Length (L)        |

|----------------------------------|-----------------------|-------------------|

| $M_{1A}, M_{1B}, M_{2A}, M_{2B}$ | $40~\mu\mathrm{m}$    | 60 nm             |

| $M_{3A}, M_{3B}$                 | $204.8~\mu\mathrm{m}$ | 60 nm             |

| $M_{4A}, M_{4B}$                 | $57.6~\mu\mathrm{m}$  | 60 nm             |

| $M_{5A}, M_{5B}$                 | $10~\mu\mathrm{m}$    | 60 nm             |

| $M_6$                            | $2240~\mu\mathrm{m}$  | $1~\mu\mathrm{m}$ |

| $M_{7A}, M_{7B}$                 | $672~\mu\mathrm{m}$   | $1~\mu\mathrm{m}$ |

| $M_{8A}, M_{8B}$                 | $614.4~\mu{\rm m}$    | $1~\mu\mathrm{m}$ |

| $M_9, M_{10}$                    | $16~\mu\mathrm{m}$    | 60 nm             |

| $M_{11}$                         | $409.6~\mu\mathrm{m}$ | $1~\mu\mathrm{m}$ |

| $M_{12}, M_{13}$                 | $51.2~\mu\mathrm{m}$  | $1~\mu\mathrm{m}$ |

| $M_{14}$                         | $112~\mu\mathrm{m}$   | $1~\mu\mathrm{m}$ |

When the bias current is reduced for different cluster values, the  $R_p$  value will increase, and the transconductance values of the cross-coupled transistors will decrease. Thus, setting the transconductances slightly higher for the nominal case would be more robust. Considering this situation, the transconductances of transistors  $M_9$  and  $M_{10}$  are determined as 5 mS. The transistor dimensions of the LC-VCO are listed in Table 4.2. The layout of the designed circuit is about 170  $\mu$ m × 80  $\mu$ m in size, as illustrated in Figure 4.7. If a spiral inductor was preferred in this design, a 180  $\mu$ m × 160  $\mu$ m structure as in Figure 4.8 would be needed. The inductor shown in Figure 4.8 was created using the inductance finder tool of the PDK, with a focus on minimizing the silicon area. Thus, it was attempted to enhance the inductance value by increasing the number of turns at the expense of obtaining a low quality factor. However, only the inductor alone has approximately twice the space of the LC-VCO layout shown in Figure 4.7. For the spiral inductor case, With the addition of current mirrors and capacitors, the consumed area will be more than twice that of the designed LC-VCO.

As seen in this example, the application of FAI is extremely cost effective in terms of silicon area.

Figure 4.8. The spiral inductor with the same inductance value as the FAI used in the designed LC-VCO.

#### 4.4. Simulation Results

To verify the circuit performance, the FAI and the LC-VCO are simulated using Cadence Design Suite in a TSMC 65 nm CMOS process. Parasitics from the layout are also considered in the simulations. The supply voltage is set to 1.2 V to minimize power consumption and enable the use of high-speed transistors in the process.

# 4.4.1. LC-VCO Dynamic Range and Phase Noise Analysis

Transient simulation results of the designed LC-VCO are shown in Figure 4.9(a). The oscillation occurs at 3.105 GHz with a differential amplitude of 56.1 mV. Moreover, the oscillator needs about 11.9 ns of settling time to start oscillating at the expected amplitude, as shown in Figure 4.9(b). Additionally, the THD value of 3.47% was

simulated. These simulation results were obtained when the circuit was in  $Cluster_{100}$  state and analog control voltage of the varactor ( $V_{ctr}$ ) was set to 1 V. Dynamic range is one of the most frequently noted shortcomings of AIs in the literature. Various studies have been conducted on this subject and numerous approaches have been explored as [15]. As previously stated, the narrow output voltage swing caused by the dynamic range limiting simplifies the LC-VCO design process. However, this poses a serious problem with the phase noise characteristics of the oscillator. The phase noise of an LC-VCO is inversely proportional to its amplitude, as it is clearly stated in [43], which includes an in-depth analysis of the phase noises of LC-VCOs.

Figure 4.9. (a) Differential output. (b) Settling time of the oscillator.

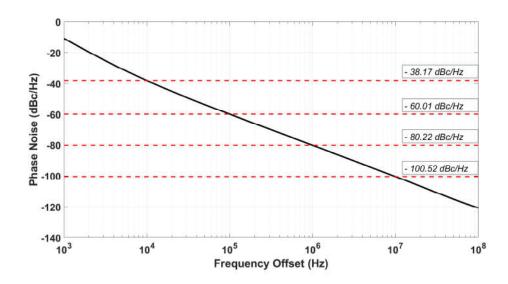

The phase noise characteristic of the designed circuit is shown in Figure 4.10. The LC-VCO, with a noise level of -80.22 dBc/Hz at a frequency offset of 1 MHz, appears to be insufficient for use in communication circuits where phase noise is crucial. However, it can be an acceptable trade-off for digital circuits where phase noise is not a key factor. To enable the usage of AIs in communication circuits, studies on the dynamic range should be accelerated. This is an excellent subject for further research.

Figure 4.10. Phase noise of the designed oscillator.

#### 4.4.2. Rail-to-Rail Output Swing Improvement

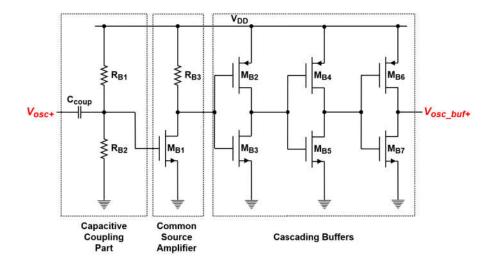

Although AIs significantly cut silicon costs, their small output swings make them unsuitable for LC-VCO designs. Here we introduce a system that transforms the oscillator output to rail-to-rail for applications where the phase noise performance of AI-based oscillators is adequate but not desirable due to the low output swing. Thanks to the buffer circuit whose schematic is given in Figure 4.11, the differential 56.1 mV signal swing obtained at 3.105 GHz can be increased to rail-to-rail by increasing the current consumption and silicon area a little more. The oscillator output is sensed using the capacitive coupling technique in the first stage of the buffer circuit, which isolates the signal from the common-mode voltage. When the C<sub>coup</sub> value is set to 500 fF

and the  $R_{B1}$  and  $R_{B2}$  values are set to 60 k $\Omega$ , the desired sensing at the appropriate frequencies can be accomplished. Additionally,  $R_{B3}$  value is set to 600  $\Omega$  to bias the transistor  $M_{B1}$  properly. However, since the 28 mV signal amplitude is insufficient to drive the following inverter, it is first boosted in the second part using a simple common source amplifier. Finally, the circuit is terminated with three successive buffers. Thanks to these buffers, the driving strength of the entire circuit is raised while the common source amplifier's load is decreased. The buffer sizes here can be customized for varied loads depending on the application area in which the oscillator will be employed.

Figure 4.11. The buffer schematic for rail-to-rail oscillation.

To operate properly in the 3 GHz frequency, the buffer circuit requires around 1.25 mA current. Since two buffers will be utilized for the oscillator's positive and negative ends, the overall current consumption will increase by roughly 2.5 mA, consuming 0.006 mm<sup>2</sup> silicon area. While simulations have proven that the buffer circuit works, they are not included in the post-layout results to allow for a fair comparison to published studies. The transistor dimensions of the buffer are listed in Table 4.3.

| Table 4.3. Transistor | dimensions of | the buffer s | hown in Figure 4.11. |

|-----------------------|---------------|--------------|----------------------|

|-----------------------|---------------|--------------|----------------------|

| Transistor Name                   | Width (W)           | Length (L) |

|-----------------------------------|---------------------|------------|

| $ m M_{B1}$                       | $24~\mu\mathrm{m}$  | 60 nm      |

| $M_{\mathrm{B2}},M_{\mathrm{B5}}$ | $1.2~\mu\mathrm{m}$ | 60 nm      |

| $ m M_{B3}$                       | 600 nm              | 60 nm      |

| $M_{\mathrm{B4}},M_{\mathrm{B7}}$ | $2.4~\mu\mathrm{m}$ | 60 nm      |

| $ m M_{B6}$                       | $4.8~\mu\mathrm{m}$ | 60 nm      |

# 4.4.3. Frequency Tuning Mechanism

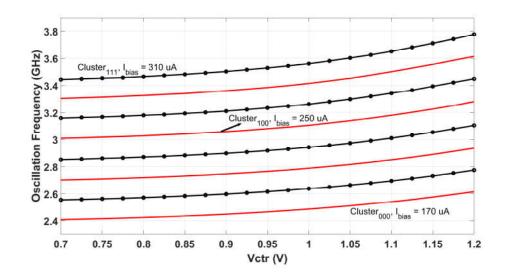

As discussed previously, this design utilizes a tuning mechanism to ensure that a broad frequency range is covered. Within each cluster, a frequency range of about 300 MHz is spanned by changing the  $V_{\rm ctr}$ . In addition, the bias current of the AI can be controlled digitally. The bias current ( $I_{\rm bias}$ ) of the circuit consists of a fixed current source of 170  $\mu$ A, and digital controllable current sources with 20, 40 and 80  $\mu$ A values. Thus, the bias current can be changed in increments of 20  $\mu$ A between values of 170  $\mu$ A and 310  $\mu$ A. The tail current of the inductor is generated by mirroring  $I_{\rm bias}$  current. While the  $I_{\rm bias}$  is 250  $\mu$ A in nominal condition, the oscillator consumes 8.5 mA. The overall current usage increases to 10.54 mA when the  $I_{\rm bias}$  current is set to 310  $\mu$ A for higher frequencies.

Figure 4.12 illustrates the simulation results of the control mechanism with 3-bit digital control, that is, with 8 different clusters. While  $V_{\rm ctr}$  voltage is tuned to get various frequency values on each curve,  $I_{\rm bias}$  current is digitally controlled to create transitions between the clusters. The circuit can continue to operate in this work when the bias current is varied between 170  $\mu$ A and 310  $\mu$ A. This way, a VCO operating between 2.4 GHz and 3.8 GHz was obtained. The percentage tuning range (PTR), which is expressed as the ratio of the difference between the higher frequency and lower frequency to the mean oscillation frequency (TR/ $f_{\rm osc-mean}$ ), is calculated as 45.16%. If wider tuning range is needed, more clusters can be obtained by increasing the number

of digital bits. But in such designs, care must be taken that the inductive behavior of the AI does not deteriorate with the change of the bias current.

Figure 4.12. Oscillation frequency versus control voltage for each 8 clusters.

This tuning mechanism is extremely useful in devices such as PLLs, where the VCO's frequency is tuned and locked to the target value. To begin, the correct frequency value will be sought by adjusting the  $V_{\rm ctr}$  voltage; if the  $V_{\rm ctr}$  voltage is insufficient, the  $I_{\rm bias}$  will be adjusted to toggle between clusters. In the case of certain changes in circuit behavior caused by non-ideal effects, distinct clusters were constructed to overlap by approximately 15% to ensure that no frequency values were missed during these transitions.

Spiral inductors, frequently used in classical LC-VCO topologies, cannot have tunable inductance values. Therefore, they may be insufficient in applications where a wide frequency range is covered such as the one described in this work. Traditionally, digitally-controlled capacitor bank architectures are favored for this reason [44]. Capacitor banks use a significant amount of silicon and complicate the layout due to matching requirements.

# 4.4.4. Literature Comparison and a Brief Discussion