# APPLICATION OF A PROTOTYPE PARALLEL PROCESSING COMPUTER

FOR A RECURRENT NEURAL NETWORK MODEL

b y

Bekir Alper Paksoy

B.S. in M.E., Boğaziçi University, 1990

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillment of the requirements for the degree of

Master of Science

in

Systems and Control Engineering

Bogazici University Library

39001100131583

Boğaziçi University

1992

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to Dr. Kemal Cılız, my thesis advisor, for his help, support, and guidance. I would like to thank Dr. Yorgo İstefanopulos for his help and guidance, Dr. Ömer Cerid for his kindness and lettting me use the Macs in his laboratory, Dr. Oğuz Tosun and Dr. Işıl Bozma for their interest in the subject, to Mehmet Göktürk for his support, and to the people who work in the Computer Center for their understanding and help. I am debted to Mr. Marshall Brain and Mr. Fred Heaton for their discussions and help about the Blitzen massively parallel processor and the Blitzen simulator. I would also like to thank to my family and my friends who granted me this thesis.

B. Alper Paksoy

#### **ABSTRACT**

this study, Hopfield's binary neural network model is simulated using a software package simulating a bit serial single instruction multiple data (SIMD) mesh array processor, called the Blitzen massively parallel processor (BMPP). First, the parallel algorithms required for the simulation are designed. Then, the parallel implementation of the Hopfield network model has been formulated using these algorithms. The parallel implementation has been analyzed for the speed and the processor utilization. To do this, time complexity of the parallel implementation is derived and compared with the time complexity of a sequential algorithm. Finally, simulation results are analyzed and compared with the analytical derivations. The parallel algorithm described in this study for the simulation of the Hopfield network model on the BMPP architecture achieves a maximum speedup in the order of the square root of the number of processors employed. It is also shown that, for the same algorithm, the maximum possible speedup can be achieved only at a finite number of processors, and the processor utilization decreases as the number of processors is increased.

#### ÖZET

Bu çalışmada Hopfield'ın ikili düzen beyinsel ağ modeli Blitzen yoğun paralel işlemcisi (BYPİ) adında bit seri tek komut çok veri esaslı iki boyutlu ağ düzenindeki dizilim işlemciyi benzeten bir yazılım paketi kullanılarak benzetilmiştir. İlk olarak benzetim için gerekli algoritmalar tasarımlanmıştır. Daha sonra, bu algoritmalar kullanılarak, Hopfield ağının paralel gerçekleştirimi formüle edilmiştir. Paralel gerçekleştirim hızlanma ve işlemci yararı açısından analiz edilmiştir. Bunu yapabilmek için, paralel gerçekleştirimin zaman karmaşıklığı türetilmiş ve bu karmaşıklık sırasal bir işlemcinin zaman karmaşıklığıyla karşılaştırılmıştır. Son olarakta, benzetim sonuçları analiz edilmiş ve analitik türetmelerle karşılaştırılmıştır. Hopfield beyinsel ağ modelinin BYPİ mimarisi üzerinde benzetimi için bu çalışmada betimlenen paralel algoritma kullanılan işlemci sayısının en fazla karekökü düzeyinde bir sağlamaktadır. Aynı algoritma hızlanma için, en hızlanmanın sadece sonlu sayıda işlemciyle gerçekleştirilebildiği ve işlemci yararının işlemci sayısı arttıkça azaldığıda gösterilmiştir.

## TABLE OF CONTENTS

|         |      |         |         |       |       |       |      |       |      |     |     |     |    |     |     | P | age  |

|---------|------|---------|---------|-------|-------|-------|------|-------|------|-----|-----|-----|----|-----|-----|---|------|

| ACKNOW  | /LED | GEMEN   | TS .    |       |       |       |      |       |      |     |     | 9   |    |     |     | • | iii  |

| ABSTRA  | CT   |         |         |       | • •   |       |      |       | •    |     | •   |     |    | •   |     |   | iv   |

|         |      |         |         |       |       |       |      |       |      |     |     |     |    |     |     |   |      |

| TABLE O | FCO  | NTENT   | S       |       |       |       | ٠    |       | •    |     |     | 9   | •  | •   | •   |   | vi   |

| LIST OF | FIGU | RES .   |         |       |       |       | •    |       | •    |     | •   |     | •  | ٠   | •   | • | viii |

| LIST OF | TABI | LES .   |         |       |       |       | •    |       | •    |     | •   | •   | ٥  |     |     |   | x v  |

| LIST OF | SYMI | 3OLS    |         |       |       |       |      |       |      | ۰   | •   | •   | •  |     |     |   | xvii |

| I       | INTE | RODUC   | TION    | •     |       |       | •    | • •   |      | •   |     | •   |    |     |     |   | 1    |

|         | 1.1  | A His   | torical | Pe    | rspec | ctive |      |       | ٠    | •   | ۰   | 0   |    |     |     | • | 1    |

|         | 1.2  | Scope,  | Purpo   | se,   | and   | Out   | ine  | of    | Th   | is  | Th  | esi | S  |     | •   |   | 4    |

| II      | BAS  | ICS IN  | PARAI   | LEI   | LPR   | OCE   | SSI  | NG    | •    |     |     | •   |    |     | •   |   | 6    |

|         | 2.1  | Paralle | l Com   | puti  | ing ( | Clas  | ses  |       | •    | •   |     |     |    |     | •   | • | 6    |

|         |      | 2.1.1   | Archi   | tecti | ire : | Base  | d (  | Clas  | sifi | ica | tio | n   |    |     |     |   | 8    |

|         |      | 2.1.2   | Struct  | ure   | Bas   | ed (  | Clas | ssifi | cat  | ion | l   | •   | •  | •   |     |   | 1 1  |

|         | 2.2  | Paralle | el Alg  | orit  | hms   |       |      |       | •    |     | •   |     | •  |     | •   | ٠ | 2 1  |

|         |      | 2.2.1   | Desig   | n A   | ppro  | oach  | es   |       |      |     |     | •   | •  |     |     |   | 21   |

|         |      | 2.2.2   | Direct  | ed    | Асус  | clic  | Gra  | phs   |      | •   | ۰   |     | •  | •   |     | a | 25   |

| •       |      | 2.2.3   | Comp    | utat  | ion   | Con   | nple | exit  | y    | ٠   | •   |     | •  | •   |     |   | 28   |

|         |      | 2.2.4   | Comn    | nuni  | catio | on (  | Com  | ple   | xity | 7   | •   | •   | •  | •   |     | • | 3 1  |

|         |      | 2.2.5   | Comb    | inec  | i Co  | mpl   | exit | ties  | an   | d   | Pe  | rfc | rn | nai | nce | € |      |

|         |      |         | Meas    | ure   | s.    |       |      |       |      | •   |     | •   |    |     |     |   | 36   |

| III     | IMP  | LEMEN   | TATIO   | ON I  | SSU   | ES A  | ND   | SII   | MU   | LA  | IT. | ON  | 1  |     |     |   | 39   |

|         | 3.1  | Design  | of th   | e P   | arall | el A  | lgo  | rith  | ms   | ٥   | •   |     |    |     |     |   | 39   |

|         |      | 3.1.1   |         |       |       |       |      |       |      |     |     |     |    |     |     |   |      |

|         |      | 3.1.2   | Matri   | x S   | torag | ge .  |      |       |      |     |     |     |    |     |     |   | 4 1  |

|         |      | 3.1.3   |         |       |       |       |      |       |      |     |     |     |    |     |     |   |      |

|         |      | 3.1.4   |         |       |       |       |      |       |      |     |     |     |    |     |     |   |      |

|         |      |         | Multi   | -     |       |       |      |       |      |     |     |     |    |     |     |   |      |

|         | 3.2  | Compl   | -       | -     |       |       |      |       |      |     |     |     |    |     |     |   |      |

|         |      | _       | Weigh   |       |       |       |      |       |      |     |     |     |    |     |     |   |      |

|         |      | 3.2.2   | _       |       |       |       |      |       |      |     |     |     |    |     |     |   |      |

|         |      | 3.2.3   |         |       |       | _     |      |       |      |     |     |     |    |     |     |   |      |

|         |      |         |         |       | -     |       | _    |       |      | -   |     |     |    |     |     |   |      |

|         | 3.3  | Sim  | ulat | ion  | R    | est | ilts | ·   |      |    |   |     |     |   |     |   | • | • | • | • | 60 |

|---------|------|------|------|------|------|-----|------|-----|------|----|---|-----|-----|---|-----|---|---|---|---|---|----|

|         |      | 3.3. | 1    | Res  | ults | fo  | r    | the | B    | MP | P |     |     | • |     | • | • | • | • |   | 61 |

|         |      | 3.3. | 2    | Res  | ults | f   | or   | the | IS   | P  |   |     |     |   |     |   | • |   |   | • | 67 |

|         | 3.4  | Ana  | lysi | s o  | f t  | he  | Si   | mul | lati | on | R | esi | ılt | S | ano | i |   |   |   |   |    |

|         |      | Disc | cuss | sion | S    |     | •    |     |      |    |   |     |     | • |     |   | • |   |   | ۰ | 69 |

|         |      | 3.4. | 1    | Spe  | edu  | р   | A    | nal | ysi  | S  |   |     |     | ٠ |     | • |   |   |   |   | 69 |

|         |      | 3.4. |      |      |      |     |      |     |      |    |   |     |     |   |     |   |   |   |   |   |    |

| ΙV      | CON  |      |      |      |      |     |      |     |      |    |   |     |     |   |     |   |   |   |   |   |    |

|         | 4.1  | Con  | clu  | sion | ı .  |     |      |     | ٠    |    |   |     | •   | • | •   |   | • |   |   | • | 87 |

|         | 4.2  | Futu | ire  | W    | ork  | •   | •    |     |      |    |   |     |     |   | •   | ٠ | • |   |   |   | 91 |

| APPEND  |      |      |      |      |      |     |      |     |      |    |   |     |     |   |     |   |   |   |   |   |    |

| APPEND: |      |      |      |      |      |     |      |     |      |    |   |     |     |   |     |   |   |   |   |   |    |

| APPEND  |      |      |      |      |      |     |      |     |      |    |   |     |     |   |     |   |   |   |   |   |    |

| APPEND: | IX D |      |      |      |      |     |      |     | ٠    | •  | • |     | •   |   |     |   | o |   |   | 9 | 99 |

| APPEND: |      |      |      |      |      |     |      |     |      |    |   |     |     |   |     |   |   |   |   |   |    |

| BIBLIOG |      |      |      |      |      |     |      |     |      |    |   |     |     |   |     |   |   |   |   |   |    |

| DEEEDEN |      |      |      |      |      |     |      |     |      |    |   |     |     |   |     |   |   |   |   |   |    |

# LIST OF FIGURES

|        |          |                                           | <u>Page</u> |

|--------|----------|-------------------------------------------|-------------|

| FIGURE | 2.1 (a)  | The SISD model.                           | 9           |

| FIGURE | 2.1 (b)  | The SIMD model.                           | 9           |

| FIGURE | 2.1 (c)  | The MISD model.                           | 9           |

| FIGURE | 2.1 (d)  | The MIMD model.                           | 10          |

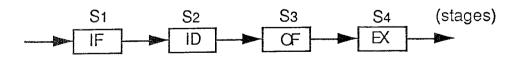

| FIGURE | 2.2      | The instruction pipelining.               | 1 1         |

| FIGURE | 2.3      | The concept of systolic array.            | 1 3         |

| FIGURE | 2.4      | A generalized array processor.            | 14          |

| FIGURE | 2.5      | PE interconnection schemes.               | 18          |

| FIGURE | 2.6      | A sequential noise removel algorithm.     | 24          |

| FIGURE | 2.7      | A parallel noise removal algorithm.       | 2 4         |

| FIGURE | 2.8      | A DAG for $(a+b)^2$ .                     | 26          |

| FIGURE | 2.9      | Another DAG for $(a+b)^2$ .               | 3 0         |

| FIGURE | 2.10 (a) | A single node broadcast on a 2-D mesh.    | 3 3         |

| FIGURE | 2.10 (b) | The corresponding spanning tree.          | 3 3         |

| FIGURE | 2.11 (a) | A single node accumulation on a 2-D mesh. | 3 4         |

|        |         |                                                                                                                           | Page |

|--------|---------|---------------------------------------------------------------------------------------------------------------------------|------|

| FIGURE | 3.6     | A parallel algorithm for (square) matrix-vector multiplication.                                                           | 5 3  |

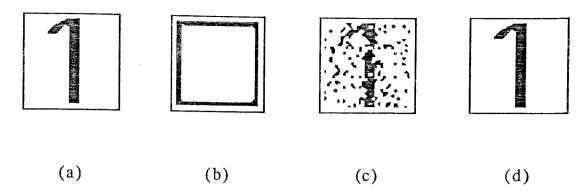

| FIGURE | 3.7 (a) | Images of the simulation test with 1K PEs (image class number 1).                                                         | 62   |

| FIGURE | 3.7 (b) | Images of the simulation test with 1K PEs(image class number 2).                                                          | 62   |

| FIGURE | 3.7 (c) | Images of the simulation test with 1K PEs (distorted input image).                                                        | 62   |

| FIGURE | 3.7 (d) | Images of the simulation test with 1K PEs (output image obtained after convergence).                                      | 62   |

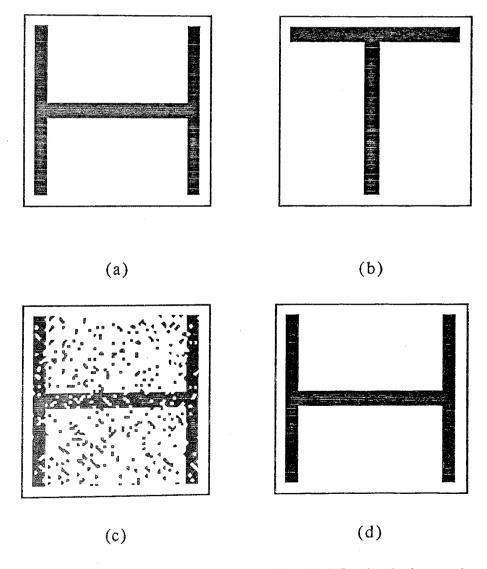

| FIGURE | 3.8 (a) | Images of the simulation test with 4K PEs (image class number 1).                                                         | 62   |

| FIGURE | 3.8 (b) | Images of the simulation test with 4K PEs (image class number 2).                                                         | 62   |

| FIGURE | 3.8 (c) | Images of the simulation test with 4K PEs (distorted input image).                                                        | 62   |

| FIGURE | 3.8 (d) | Images of the simulation test with 4K PEs (output image obtained after convergence).                                      | 62   |

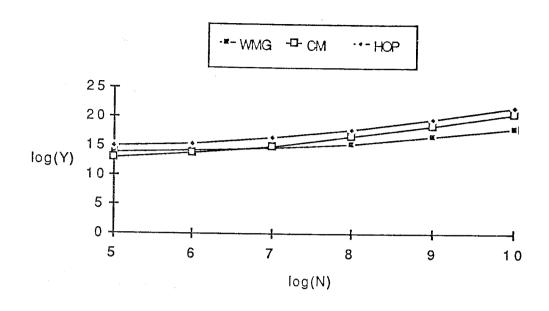

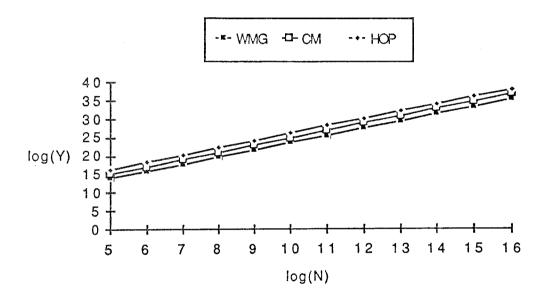

| FIGURE | 3.9 (a) | The logarithm of the number of cycles (log(Y)) vs. the logarithm of the problem size (log(N)) (graph of the data given in |      |

|        |         | Table 3.1 (a)) (1K PEs).                                                                                                  | 64   |

|        |          |                                                                                                                                                          | <u>Page</u> |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

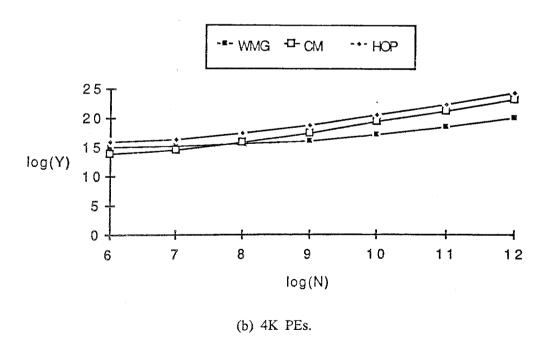

| FIGURE | 3.9 (b)  | The logarithm of the number of cycles $(\log(Y))$ vs. the logarithm of the problem size $(\log(N))$ (graph of the data given in Table 3.1 (b)) (4K PEs). | 6 4         |

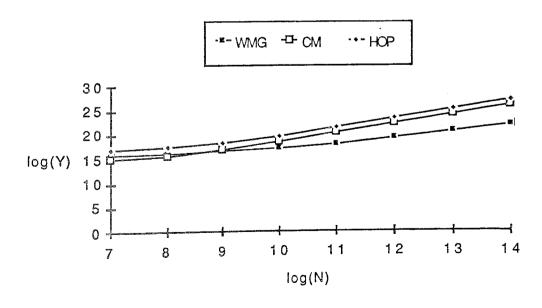

| FIGURE | 3.10 (a) | The logarithm of the number of cycles (log(Y)) vs. the logarithm of the problem size (log(N)) (graph of the data given in Table 3.2 (a)) (16K PEs).      | 66          |

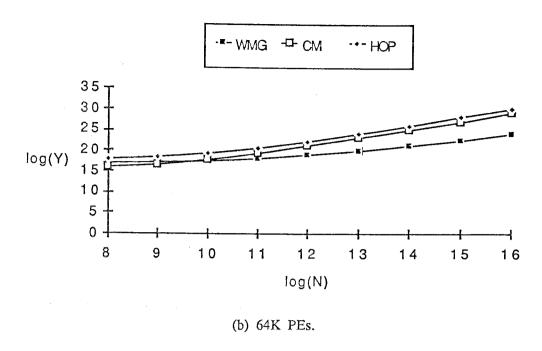

| FIGURE | 3.10 (b) | The logarithm of the number of cycles (log(Y)) vs. the logarithm of the problem size (log(N)) (graph of the data given in Table 3.2 (b)) (64K PEs).      | 67          |

| FIGURE | 3.11     | The logarithm of the number of cycles (log(Y)) vs. the logarithm of the problem size (log(N)) (graph of the data given in Table 3.3).                    | 68          |

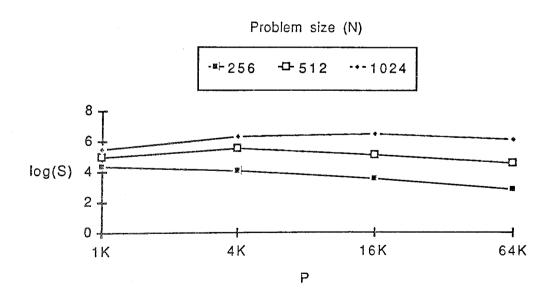

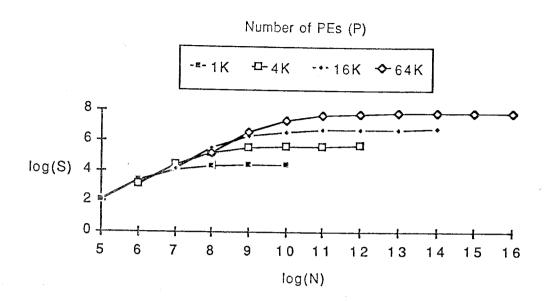

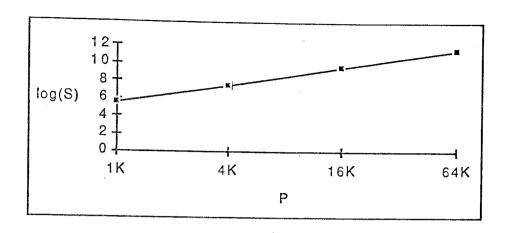

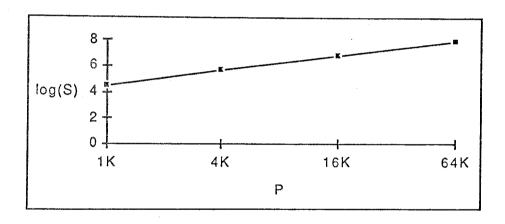

| FIGURE | 3.12     | The logarithm of the speedup (log(S)) vs. the number of PEs (P) for the WMG with different problem sizes (N).                                            | 7 1         |

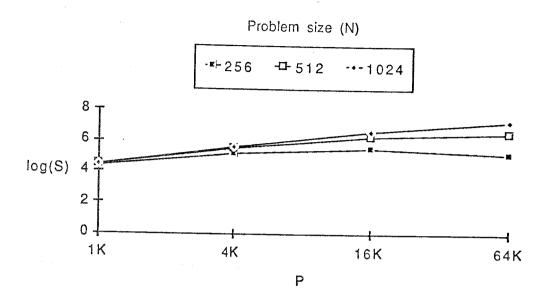

| FIGURE | 3.13     | The logarithm of the speedup (log(S)) vs. the number of PEs (P) for the CM with different problem sizes (N).                                             | 72          |

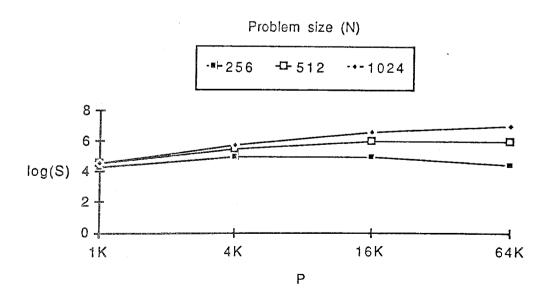

| FIGURE | 3.14     | The logarithm of the speedup (log(S)) vs. the number of PEs (P) for the HOP with different problem sizes (N).                                            | 7 2         |

|                 | •                                                                                                                                                    | <u>Page</u> |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

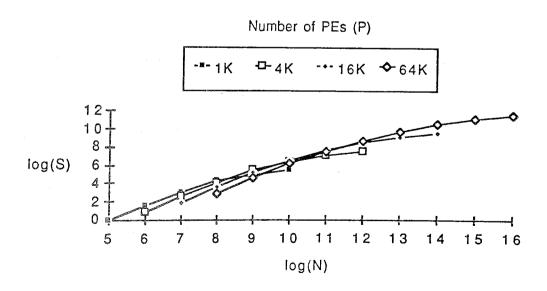

| FIGURE 3.15     | The logarithm of the speedup (log(S)) vs. the logarithm of the problem size (log(N)) for the WMG with different number of processing elements (PEs). | 7 4         |

| FIGURE 3.16     | The logarithm of the speedup (log(S)) vs. the logarithm of the problem size (log(N)) for the CM with different number of processing elements (PEs).  | 7 5         |

| FIGURE 3.17     | The logarithm of the speedup (log(S)) vs. the logarithm of the problem size (log(N)) for the HOP with different number of processing elements (PEs). | 75          |

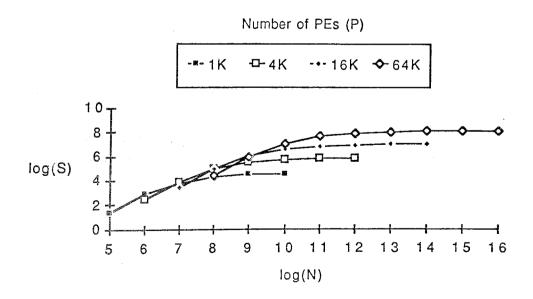

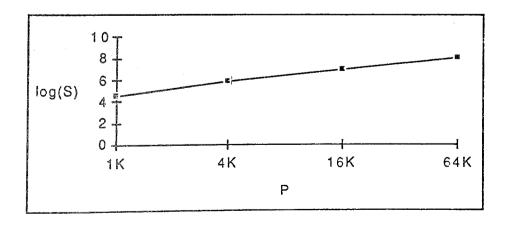

| FIGURE 3.18 (a) | The logarithm of the speedup (log(S)) vs. the number of PEs (P), where the problem size (N) is equal to P (WMG).                                     | 77          |

| FIGURE 3.18 (b) | The logarithm of the speedup (log(S)) vs. the number of PEs (P), where the problem size (N) is equal to P (CM).                                      | 77          |

| FIGURE 3.18 (c) | The logarithm of the speedup (log(S)) vs. the number of PEs (P), where the problem size (N) is equal to P (HOP).                                     | 77          |

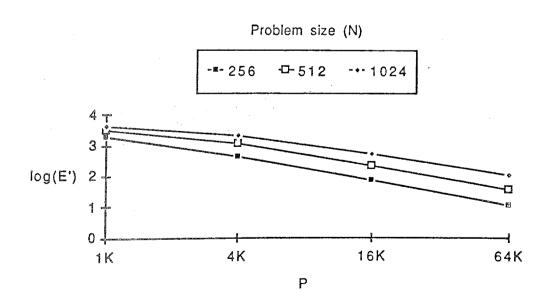

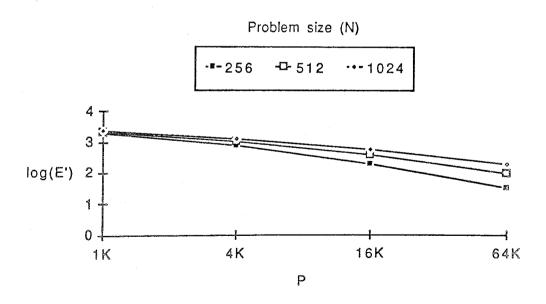

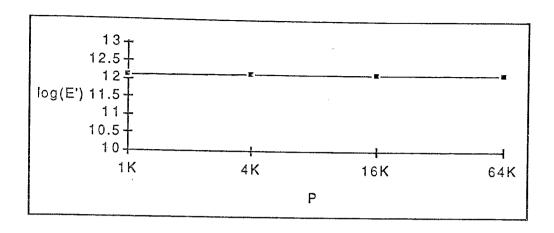

| FIGURE 3.19     | Logarithm of the normalized efficiency (log(E')) vs. the number of PEs (P) for the WMG with different problem sizes (N).                             | 8 1         |

|        |          |                                                                                                                                                      | <u>Page</u> |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| FIGURE | 3.15     | The logarithm of the speedup (log(S)) vs. the logarithm of the problem size (log(N)) for the WMG with different number of processing elements (PEs). | 7 4         |

| FIGURE | 3.16     | The logarithm of the speedup (log(S)) vs. the logarithm of the problem size (log(N)) for the CM with different number of processing elements (PEs).  | 75          |

| FIGURE | 3.17     | The logarithm of the speedup (log(S)) vs. the logarithm of the problem size (log(N)) for the HOP with different number of processing elements (PEs). | 75          |

| FIGURE | 3.18 (a) | The logarithm of the speedup (log(S)) vs. the number of PEs (P), where the problem size (N) is equal to P (WMG).                                     | 77          |

| FIGURE | 3.18 (b) | The logarithm of the speedup (log(S)) vs. the number of PEs (P), where the problem size (N) is equal to P (CM).                                      | 77          |

| FIGURE | 3.18 (c) | The logarithm of the speedup (log(S)) vs. the number of PEs (P), where the problem size (N) is equal to P (HOP).                                     | 77          |

| FIGURE | 3.19     | Logarithm of the normalized efficiency (log(E')) vs. the number of PEs (P) for the WMG with different problem sizes (N).                             | e<br>81     |

|        |          |                                                                                                                                               | Page |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

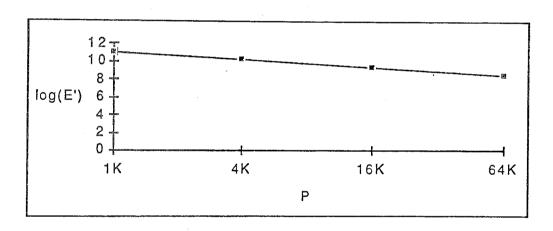

| FIGURE | 3.20     | Logarithm of the normalized efficiency (log(E')) vs. the number of PEs (P) for the CM with different problem sizes (N).                       | 8 2  |

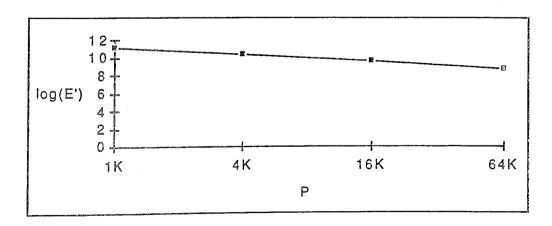

| FIGURE | 3.21     | Logarithm of the normalized efficiency (log(E')) vs. the number of PEs (P) for the HOP with different problem sizes (N).                      | 8 2  |

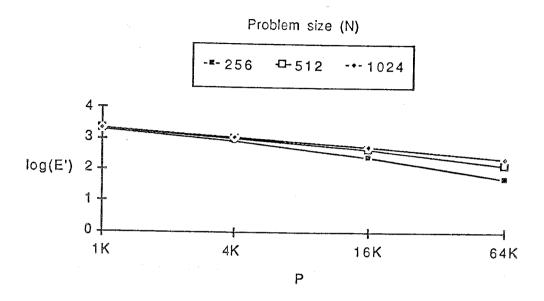

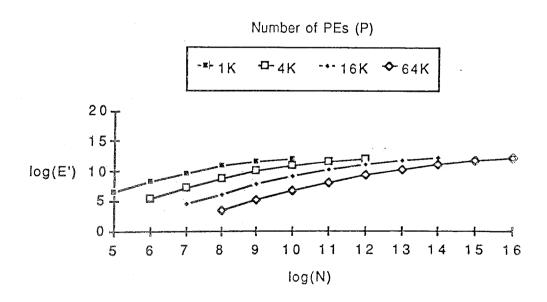

| FIGURE | 3.22     | Logarithm of the normalized efficiency (log(E')) vs. the logarithm of the problem size (log(N)) for the WMG with different number of PEs (P). | 83   |

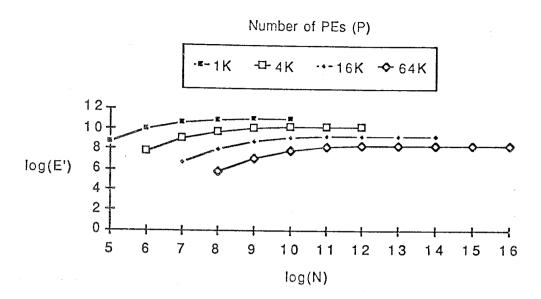

| FIGURE | 3.23     | Logarithm of the normalized efficiency (log(E')) vs. the logarithm of the problem size (log(N)) for the CM with different number of PEs (P).  | 84   |

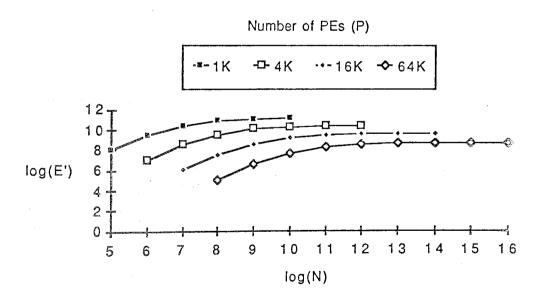

| FIGURE | 3.24     | Logarithm of the normalized efficiency (log(E')) vs. the logarithm of the problem size (log(N)) for the HOP with different number of PEs (P). | 8 4  |

| FIGURE | 3.25 (a) | Logarithm of the normalized efficiency (log(E')) vs. the number of PEs (P) graphs, where the problem size (N) is equal to P (WMG).            | 85   |

| FIGURE | 3.25 (b) | Logarithm of the normalized efficiency (log(E')) vs. the number of PEs (P) graphs , where the problem size (N) is equal to P (CM).            | 8 5  |

|        |          |                                                                                                                                    | Page |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------|------|

| FIGURE | 3.25 (c) | Logarithm of the normalized efficiency (log(E')) vs. the number of PEs (P) graphs, where the problem size (N) is equal to P (HOP). | 8 5  |

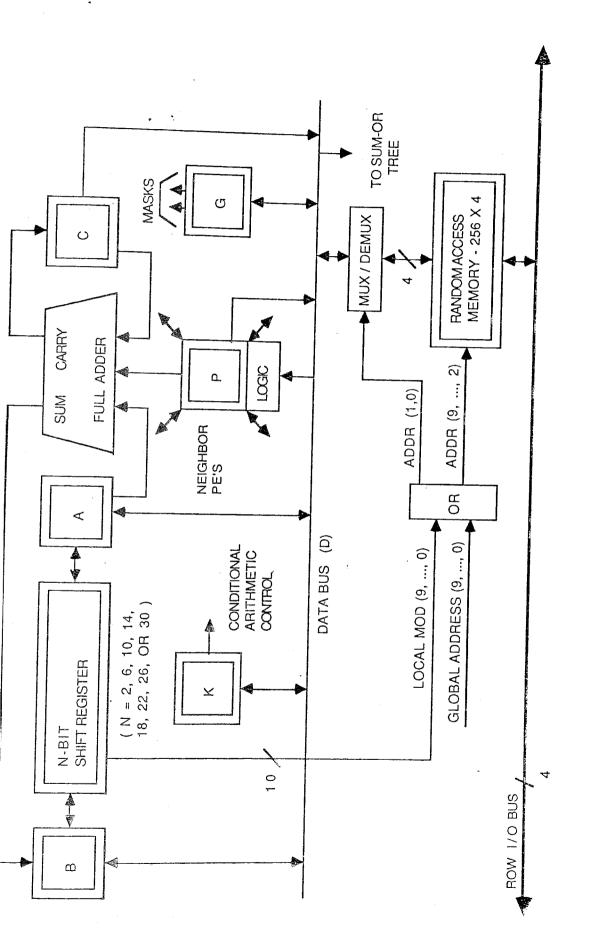

| FIGURE | B.1      | Functional parts of a BMPP processing element.                                                                                     | 96   |

| FIGURE | D.1      | Sample Blitzen code                                                                                                                | 99   |

# LIST OF TABLES

|       |         |                                                                                                       | Page |

|-------|---------|-------------------------------------------------------------------------------------------------------|------|

| TABLE | 2.1     | Vector operations.                                                                                    | 1 2  |

| TABLE | 2.2     | Processing rates in MOPS for different parallel processing systems.                                   | 1 5  |

| TABLE | 2.3     | Develoments in array processors.                                                                      | 1 7  |

| TABLE | 3.1 (a) | The number of processor cycles for the simulations run as returned by the Blitzen simulator 1(K PEs). | 63   |

| TABLE | 3.1 (b) | The number of processor cycles for the simulations run as returned by the Blitzen simulator (4K PEs). | 63   |

| TABLE | 3.2 (a) | The number of processor cycles found using the cycle estimation functions for the BMPP (16K PEs).     | 6 5  |

| TABLE | 3.2 (b) | The number of processor cycles found using the cycle estimation functions for the BMPP (64K PEs).     | 66   |

| TABLE | 3.3     | The number of processor cycles found using the cycle estimation functions for the ISP.                | 67   |

| TABLE | 3.4 (a) | Speedup values obtained (1K PEs).                                                                     | 69   |

| TABLE | 3.4 (b) | Speedup values obtained (4K PEs).                                                                     | 70   |

| TABLE | 3.4 (c) | Speedup values obtained (16K PEs).                                                                    | 70   |

|               |                                    | Page |

|---------------|------------------------------------|------|

| TABLE 3.4 (d) | Speedup values obtained (64K PEs). | 70   |

| TABLE 3.5 (a) | Efficiencies achieved (1K PEs).    | 79   |

| TABLE 3.5 (b) | Efficiencies achieved (4K PEs).    | 80   |

| TABLE 3.5 (c) | Efficiencies achieved (16K PEs).   | 80   |

| TABLE 3.5 (d) | Efficiencies achieved (64K PEs).   | 80   |

#### LIST OF SYMBOLS

C The number of image classes in the Hopfield algorithm.

E<sub>p</sub> Efficiency achieved using P processors.

E' Normalized efficiency  $(E'=10^5*E)$ .

Log(x) Logarithm of x in base 2.

N The problem size in the Hopfield algorithm.

O(x) A complexity function that puts an upper bound in the order of x.

P The number of processors.

R The number of iterations in the Hopfield algorithm.

R The set of real numbers.

Speedup achieved using P processors.

T<sub>p</sub> Time complexity of a parallel algorithm using P processors.

T<sub>s</sub> Time complexity of a sequential algorithm

Y The number of cycles.

#### I INTRODUCTION

## 1.1 A Historical Perspective

Today, many scientific applications benefit from the information processing capabilities of computer technology. As the number of fields using computer technology increase, these fields' dependencies and requirements also increase in various levels. These areas range from structural analysis to socioeconomics or from medical diagnosis to artificial intelligence. However, their basic demand remains the same: A feasible way of computing in reasonable time with increased reliability.

Most computer systems serve this basic demand in the same fashion as described by John von Neumann in 1940's. A control unit fetches an instruction and its operands from the memory, decodes and executes the instruction, then stores the result. To achieve the highest performance possible these tasks can be staged into multiple levels with different hardware realizations, e.g. main memory, central processing unit, I/O system realized as random access memory, cache memory, data and control bus, microprocessor, processing elements (PEs), word and bit level registers and hard disk.

Nearly all of the computers in use today are sequential. That is, they only have a single processing unit. Nevertheless, there is not a clear distinction between sequential and parallel computers because today's 'sequential' computers incorporate many parallelism properties like pipelining and memory interleaving. Actually, the basic mentality behind the parallel processing is the usage of more than one component which is the basic bottleneck in sequential processing. From this point of view if computational demands are I/O bounded, one may use multiple I/O devices or

multiple data buses or a hierarchical memory system, or if demands are processor bounded one can use multiple processors or floating point accelerators or other specially designed processors, and such systems would still be called sequential.

In its broadest meaning parallel processing is the exploitation of concurrency in the computing process using multiple devices of the same or having different devices working simultaneously or in overlapping time spans.

In an ideally sequential system, only a single component can be active at a time and all the others must wait its completion. Thus, parallel processing is a time and cost-effective solution to the parallelizable problems.

Another category is the distributed processing. Though not a precise distinction, parallel processing refers to the exploitation of concurrency by devices in a local area (at most in a room) and distributed processing refers to the information processing within geographically distributed areas. A good example to the latter is data communication networks.

There is neither a purely sequential nor a purely parallel system. The reason for the former is that today's technology allows us to incorporate parallelism properties into any computer in a cost-effective manner and the reason for the latter is that any 'single' process is sequential at somewhere through its algorithm. A sequential (or uniprocessor roughly) system can enjoy parallel properties by the multiplicity of functional units, parallelism and pipelining within the CPU, overlapped CPU and I/O operations, and the use of a hierarchical memory system [1].

For the sequential case even the personal computers of today may have many processors inside; the main processor can continue its execution while the mathematical coprocessor crunches the numbers or the I/O processor manages the storage system or the communication processor handles the communication; the main processor may be designed in components working simultaneously

to implement pipelining; the memory can be designed hierarchically to implement memory caching. A vector processing computer may have a single processor but still can perform operations on multiple numbers.

For the parallel case the solution of partial differential equations requires a computational unit communicate with its neighbors. Matrix operations demand processors to communicate with each other to find the final result. Image processing operations need a processor receive pixel values kept at neighboring processors; finally database operations need a central control unit be aware of the results after each record search. So for any single problem either a central control scheme which will synchronize and control processors or some communications between the processors are required to reach the solution. Nevertheless all the above problems can be divided into parts which are independent of each other up to a certain extent.

In 1958, Steve Unger proposed the first parallel processing computer in a paper. In 1967 a parallel working machine which was used to analyze bubble chamber tracks was implemented in University College London. Some other cornerstones were Illiac IV and Staran built in 1972, the first commercial parallel processor DAP in 1980, Massively Parallel Processor (MPP) delivered to NASA in 1983 [2], and the Connection Machine (CM) series (the latest, CM-2, finished in 1986) of the Thinking Machines Corporation [3].

There are several approaches to the realization of parallel processing computers. These are pipelining computers, vector processors, systolic arrays, array processors, and multiprocessors. A parallel computer may be classified in any of these categories [3].

Processing of images, whether binary, gray code, or color, where one or more of image pixels are assigned to a single processor, was the original and ideal application area of parallel computing This is due to the inherent parallelism in image analysis techniques like feature extraction and segmentation whose spatial structures could easily be decomposed and mapped to the processor

array. These computers, characterized by a large number (1K-64K) of processing elements (PEs), were called massively parallel computers (MPCs) or array processors. The PEs were controlled and synchronized by central control unit and were relatively simpler units with small memories (in orders of hundreds or thousands of bits), a limited instruction set, and a two dimensional mesh topology which enables PEs to communicate with their immediate neighbors.

With the advances in VLSI technology in 1980's, new interconnection topologies like n-D binary cube were developed and more applications were stimulated like information retrieval, computer vision, and artificial intelligence to benefit from the MPCs. Also the scientific computing required the processing of fixed or floating point numbers. Thus MPCs with more complex PEs (Maspar MP-1) or with a floating point accelerator assigned to a group of PEs (CM-2) were developed.

The MPCs of the present generation, both the commercial systems and the research projects, feature advanced processor and interconnection structures much more complex than the single bit mesh connected computers of the early implementations. The winning direction seems to be the combination, at some level, of different kinds of processing elements in such a way to have processing elements suited for any possible operation. Thanks to such a flexibility, MPCs can be considered the most effective parallel computer solution in many of the mentioned application fields [2].

# 1.2 Scope, Purpose, and Outline of This Thesis

Inspired from the nervous system, neural nets display behavioural similarities with human beings while learning. However, artificial simulation of nets suffers from the large computational burden imposed by the iterating training sessions. A training session comprises matrix and vector operations with elements going through nonlinear functions. Especially multilayered nets require a large number of training sessions because of the diminishing effect of error correcting terms on connection weights while backpropagating.

Matrix operations of inner product, matrix-vector product, and matrix-matrix product have computational complexities in orders of N, N<sup>2</sup>, and N<sup>3</sup>, respectively. The sequential machines directly reflect the computational complexity of an algorithm to the time complexity of the algorithm. Though parallel computing leaves NP problems as they are, it offers, for example, speedups in the orders of N<sup>3</sup>/logN in matrix multiplications. With the recent decrease in hardware prices, MPCs (Massively Parallel Computers) can be used more effectively as means to decrease the time complexity of the computational algorithms.

In this study, we will try to simulate an artificial neural network model, called the Hopfield network model, using a software simulator that simulates a massively parallel processor, called the Blitzen massively parallel processor (BMPP).

We will first design the parallel algorithms required for the simulation. Then, we will formulate the parallel implementation of the Hopfield network model using these algorithms. The parallel implementation will also be analyzed for the speed and processor time complexity of the To do this. be derived and compared with the time implementation will complexity of a sequential algorithm. Then, we will simulate the Hopfield network model using code written in the Blitzen simulator's language. Finally, the simulation results will be analyzed and compared with the analytical derivations.

#### II BASICS IN PARALLEL PROCESSING

## 2.1 Parallel Computing Classes

Parallel computing has developed according to the computational needs of applications. The differences between the parallel computing classes are largely based on these needs.

The first class of needs are exemplified by the matrix operations, finite difference, and finite element methods of PDE solutions used in weather forecasting, oceanography and astrophysics, image processing, reservoir modelling, and plasma fusion power studies. The FFT of signal processing, the real-time or off-line searching, matching, merging, and sorting operations on data bases used in documentation retrieval, analysis of text and memory based reasoning (linguistic pattern recognition), air traffic control also have similar needs. Some other elements of the first class are the simulation studies in computer vision, object recognition, neural nets, molecular dynamics, VLSI design, and computer assisted tomography [1,3,4,5].

In the above problems the data processed or the variables manipulated can be divided into multiple streams such that each computational unit handles a stream. Such problems are called data or variable parallel. They can be decomposed along a spatial dimension; a different computational unit can be assigned the task of manipulating the data or variables associated with a small region in space. A system choice for the data parallel problems among the existing systems may lead to a uniprocessor with multiple functional units (a pipelining computer or a vector processor) running in a single-instruction single-data (SISD) fashion. A better choice can be a system comprising a large number of simple processors working together in a single-instruction multiple-data

(SIMD) fashion (systolic arrays or array processors) since the interactions between the processors are local in most of the above problems.

Another class deals with the computation, analysis, simulation and optimization of large scale systems, general system of equations and mathematical programming. These problems can be divided into a smaller number of subtasks, and these subtasks appear to be more complex than the subtasks of a highly data parallelizable problem. Such problems are also called *instruction parallel*, and a system with fewer but more powerful processors under a more complex control mechanism is needed. A multiprocessor system with semi-autonomous and loosely connected processors is a good candidate for such systems [4].

A third class is information acquisition, extraction, and control within geographically distributed systems. This class, named as distributed processing, can be considered as a special case of parallel processing with a loose or no synchronization. Contrary to the other forms of parallel processing, communication and reliability have the utmost importance in distributed processing. Two examples are the sensor and the data communication networks [4].

The above needs lead to the discrimination of parallel processors in the respects of type and number of processors (simple vs. complex and coarse grained vs. fine grained), presence or absence of a central control mechanism (single instruction or multiple instruction), synchronous vs. asynchronous (local vs. distributed processing), and processor interconnection topologies [4].

Only the most popular two of these classification schemes are considered in this study. The first classification is based on the multiplicity of instruction and data streams a computer executes [1]. A sequential computer executes a single instruction stream on a single data stream. A parallel computer can execute single/multiple instruction stream(s) on single/multiple data streams.

The second classification is loosely based on the combined structural properties of a system, e.g., number of processors in the system, tightness of coupling between these processors, how specialized these processors are, etc. The degree of parallelism in the sense of autonomy of individual processors is taken as the degree of complexity. Therefore, a pipelining system is taken as the simplest parallel system and a multiprocessing system is taken as the most complex parallel system because the latter also deals with the problems of the first one, and it also has complex synchronization problems. In this study, we will focus our attention to systems with multiple processors which execute the same instruction simultaneously.

#### 2.1.1 Architecture Based Classification

Any computer must handle data or instructions in a single stream or in multiple streams. The computing model thus chosen determines the architecture of a computer.

The classification of computers based on the multiplicity of streams was first proposed by Michael J. Flynn in 1966. Flynn has used three basic conceptual components in his system models: memory units which keep instructions and data, a processing unit which executes instruction on data, and a control unit which decodes and sends the instructions to the processing unit. Each instruction stream is generated by a single control unit. Data streams flow between processors and memory modules bidirectionally. Computers can be classified into four groups based on the four models given below [1].

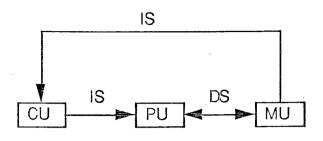

Single Instruction Single Data (SISD) Model: This model has only one of each of the basic system components. It is the basic model for the sequential computers. Most SISD systems have pipelining processors. This model was actually proposed by John von Neumann in 1940's. Fig. 2.1 (a) illustrates the SISD model

(a) The SISD model.

(b) The SIMD model.

(c) The MISD model.

(d) The MIMD model.

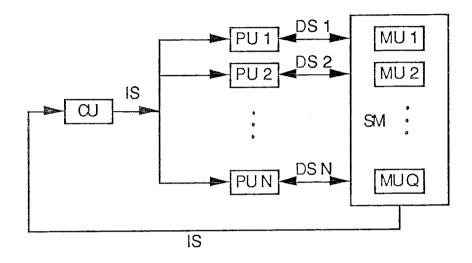

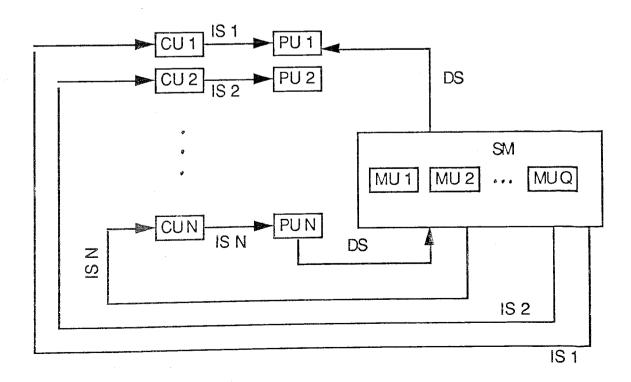

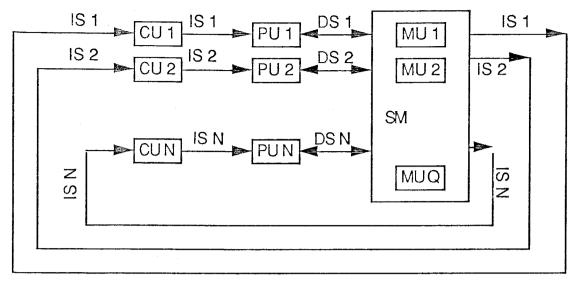

Fig. 2.1 The computational models [1]. CU: control unit, PU: processor unit, MU: Memory unit, SM: shared memory, IS: instruction stream, DS: data stream.

Single Instruction Multiple Data (SIMD) Model: This model is the basic model for array processors. Each processor receives the same instruction from the control unit and executes this instruction on its local data. Processors in a SIMD model are the simplest type of processors in all models. They communicate either through a shared memory or an interconnection network. Fig. 2.1 (b) illustrates the SIMD model.

Multiple Instruction Single Data (MISD) Model: This model nearly has no applications and has been considered as fruitless. But for the sake of completeness it can be mentioned that multiple control units sends decoded instructions to the processors for them to execute these on the same data. Note that, processors of such a system would be more complex than of an SIMD model. Fig. 2.1 (c) illustrates the MISD model.

Multiple Instruction Multiple Data (MIMD) Model: In general, multiprocessor and multicomputer systems are based on this model. Each processor in such a system executes the instruction coming from its control unit on its local data. The processors of such a system are preferred to have certain features to support process

recoverability, efficient context switching, large virtual and physical address spaces, effective synchronization primitives, an interprocessor communication mechanism and an adequate instruction set [1]. Note that if processors do not share a common memory, they would rather be called multiple SISD (MSISD) computers [1]. Fig. 2.1 (d) illustrates the MIMD model.

#### 2.1.2 Structure Based Classification

<u>Pipelining Computers</u>: In general pipelining is a time-effective solution to realize temporal parallelism in digital computers. Similar to the assembly lines in an industrial plant, tasks are divided into a sequence of subtasks which are carried out by different functional units in overlapping time spans. Pipelining computers have overlapping data processing capabilities in the central processor, in the I/O processor, or in the memory hierarchy [1].

Linear pipelining is the design of a pipeline in cascaded processing stages. These stages perform arithmetic and logic operations over the data stream flowing through the pipe. They are separated by high speed interface latches which are fast registers for holding the intermediate results between the stages [1]. Instruction, arithmetic and processor pipelining are common approaches in the processor pipelining [1]. Fig. 2.2 depicts the instruction pipelining.

Fig. 2.2 The instruction pipelining. IF: instruction fetch, ID: instruction decode, OF: operand fetch, EX: instruction execute.

<u>Vector Processing Computers</u>: A vector is an ordered set of elements where an element can be a floating point or a fixed point number, a logical quantity, or a byte. A vector operation has, at least, a vector operand and optionally a scalar or another vector operand. It may

yield either a vector or a scalar. Vector processors are candidates of fast vector/matrix operation performers and are based on high performance floating point processors and vector oriented memory organizations. Pipelining is common to all modern vector processors also [2].

The power of vector processing computers stem from their abilities to manipulate all the variables of a vector operand at a single step. Table 2.1 shows operations which can be found in modern vector processors [1].

| Vector square root Vector sine Vector summation | $B(j) = \sqrt{A(j)}$ $B(j) = \sin(A(j))$ $S = \sum A(j)$ |

|-------------------------------------------------|----------------------------------------------------------|

| Vector sine                                     | $B(j) = \sin(A(j))$                                      |

|                                                 | 1 1277                                                   |

| Vector summation                                | $S = \sum A(i)$                                          |

|                                                 | <del> \</del> \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\        |

| Vector maximum                                  | S = max(A(j))                                            |

| Vector add                                      | C(j) = A(j) + B(j)                                       |

| Vector multiply                                 | C(j) = A(j) * B(j)                                       |

| Vector larger                                   | C(j) = max(A(j),B(j))                                    |

| Vector-scalar add                               | B(j) = S + A(j)                                          |

| Vector-scalar divide                            | B(j) = A(j)/S                                            |

Table 2.1 Vector operations. A,B, and C are N-tupled vectors, and S is a scalar.

The first two examples of vector processors, CDC-Star-100 and TI-ASC, appeared in the 1960's. Cray-1 and Cyber-200 (1970's) series were the second generation machines. Cray X-MP (1983) had dual processors. The next generation of vector processing computers like Cyber-2xx and Cray-2 have very powerful multiple processors [1].

Systolic Arrays: As the hardware costs decline, it has become more feasible to implement parallel algorithms that realize computationally bounded algorithms directly in the hardware using the rapidly advancing VLSI technology. Examples to these computationally bounded algorithms are FFT, L-U decomposition, matrix multiplication, and feature extraction algorithms [1].

(a) A conventional processor

(b) A systolic array.

Fig. 2.3 The concept of systolic array. PE: processing element.

A systolic array can exploit a wide class of computationally bounded algorithms where multiple operations are performed on each data item in a repetitive manner. Once a data item is brought out from the memory it can be used effectively at each cell it passes. Thus, information in a systolic system flows between the cells in a pipelined fashion, and communication with the outside world occurs only at the boundary cells. The memory fetches act similar to the pulses of the heart that pushes data in and out of the systolic array. Fig. 2.3 displays a conventional processor vs. a systolic array.

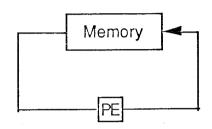

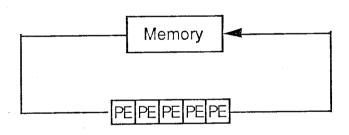

Array Processors (Massively Parallel Computers): A sequential computer's speed can be improved in various ways. Unfortunately, since these improvements must combine the latest technological innovations, such designs tend to be very costly. Array processors offer a feasible way of achieving the desired performance.

Array processors were first proposed in 1958 [2]. Their most distinguishing feature is the huge amount of processing elements they possess in a repetitive structure. This architecture is called *fine grained parallelism* contrary to the architecture of a multiprocessor system, called *coarse grained parallelism* with fewer but more complex processors. Table 2.2 lists estimated speeds for three different massively parallel computers (MPC's).

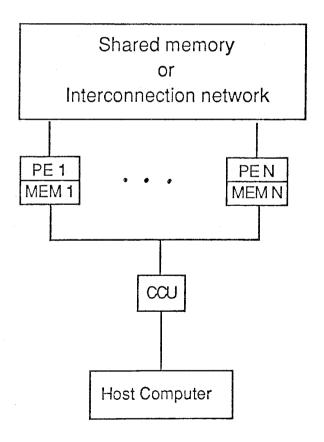

Fig. 2.4 A generalized array processor. A host computer provides the user interface, usually, by a high level programming language. It detects and sends the parallel parts of the code to the central control unit (CCU). The CCU decodes and broadcasts these instructions to the PEs. Every PE has its local memory (MEM) and communicates with each other either by a shared memory or an interconnection network.

Another characteristic of array processors is the way they and execute instruction receive data streams. Though it theoretically possible that an array processor can be organized in MISD or MIMD fashion, the latter has rarely been implemented, and the former has never been implemented. SIMD is the most suitable architectural configuration because of the inherent data parallelism in most of the problems. Instruction parallelism is hard to achieve of the highly complex algorithm threading synchronization issues. The array structure is the most efficient for algorithms which makes every PE execute the same instruction. However, a partitioned MIMD/SIMD approach is also possible as exampled in Connection Machine and Image Understanding Array [6,3]. Fig. 2.4 shows the general layout of the functional parts of an array processor.

| Operation       | MPP  | СМ   | DAP  |

|-----------------|------|------|------|

| Addition        |      |      |      |

| 8-bit fixed     | 6553 | 4000 | -    |

| 32-bit fixed    | 3343 | 3300 | -    |

| 32-bit floating | 470  | 4000 | -    |

| Multiplication  | -    |      |      |

| 8-bit fixed     | 1861 | -    | 1600 |

| 32-bit floating | 291  | 4000 | -    |

Table 2.2 Processing rates in millions of operations per second (MOPS) for different parallel processing systems.

PEs of an array processor are often simple computational units, usually with one bit registers, i.e., serial, and a limited instruction set that may contain no more than a few logical operators. They are simple arithmetic logic units without any instruction decoding capability. Usually, addition is the only mathematical operator, and some other instructions to accomplish communication between the PEs or between the PEs and the main memory are also available. They are also called data processors because they execute microlevel instructions broadcast from the

central control unit (CCU, defined in Fig. 2.4) on their local data [3]. However, bit serial processors are quite slow for word-length operations. Some designers have preferred assigning a floating point accelerator (CM-2) or a coprocessor (Digital Array Processor (DAP)) to a cluster of PEs or using PEs with internal registers of higher bit lengths and internal floating point accelerators (The MasPar family) [2].

In massively parallel processors, PEs communicate with each other via either an interconnection network or a shared memory. Many interconnection topologies ranging from one dimensional to n dimensional networks has been developed. The problem here is to choose the most suitable topology for a specific problem. If the shared memory approach is preferred, one must choose a memory access model to meet the PE memory access demands. Various interconnection schemes for interconnection networks and four memory access models for shared memory communications will be discussed later in this section.

Another class of array processors is associative processors. Associative processors use associative memories (AM) which are content addressable (data accessed by content instead of address contrary to the random-access memory (RAM)). Thus, parallel access to multiple words in memory are allowed. Associative processors are used as text retrieval computers and back-end database machines [1]. Some examples of associative processors are the Goodyear Aerospace STARAN, the Parallel Element Processing Ensemble [1], and the Airborne Associative Processor [7].

The first working processor array, completed at University College London in 1967, had a two dimensional mesh topology with 20 by 20 PEs. It was used to analyze bubble-chamber tracks [2]. Illiac IV with 64 PEs interconnected under a two dimensional mesh was fabricated by Burroughs Corporation and delivered to NASA in 1972. Illiac IV was designed to perform matrix and vector computations [1]. Burroughs Scientific Processor (BSP), by Burroughs Corporation (1979), used a crossbar interconnection network to connect PEs and memory modules (shared memory configuration)

[1]. The processors of the Digital Array Processor, (1981) by the International Computer Limited in England, could be grouped into array sizes ranging from 16 by 16 to 256 by 256. The Massively Parallel Processor (MPP) of Goodyear Aerospace delivered to NASA in 1983 [2] had 16K processors arranged on a two dimensional mesh topology. The MPP was designed for high speed processing of satellite imagery [7]. CM-1 in 1985 and CM-2 in 1987 by the Thinking Machines Corporation provided multiple topologies. CM series were intended for general purpose computing. Some other current array processors are the AIS family from Applied Intelligence Corporation, and the MasPar family from MasPar Computer Corporation [2]. Table 2.3 summarizes the developments in array processors chronologically.

| Computer  | Туре          | Year            |

|-----------|---------------|-----------------|

| Unger     | network       | 1958 (proposed) |

| Illiac-IV | network       | 1972            |

| Staran    | associative   | 1975            |

| BSP       | shared memory | 1979            |

| DAP       | network       | 1981            |

| MPP       | network       | 1983            |

| CM-1      | network       | 1985            |

| CM-2      | network       | 1987            |

Table 2.3 Developments in array processors.

In the following, we describe in more detail the two basic schemes for the interprocessor communications in array processors,

Interconnection Network Communications: In most of the massively parallel computers, PEs communicate with each other by passing data items to each other through links provided by the interconnection network.

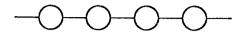

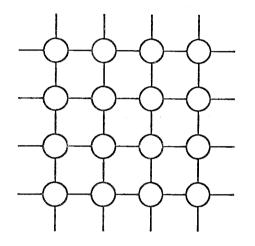

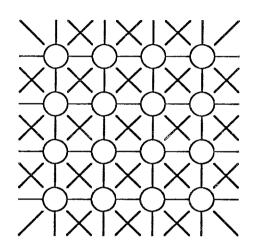

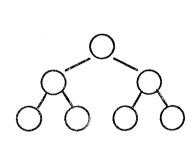

## (a) Linear array.

(b) 2-D mesh.

(c) X-grid.

(d) Tree.

(e) 3-d cube.

Fig. 2.5 PE interconnection schemes.

The most desirable intercommunication scheme is a fully connected one but it is very costly. Thus, instead of a fully connected scheme, other schemes have been proposed and implemented.

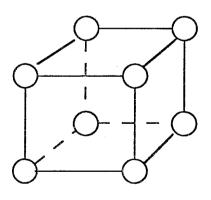

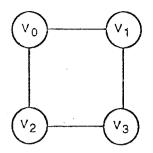

For image processing problems the most popular scheme is the two dimensional mesh since the spatial structure of numerous image processing techniques can be decomposed into a two dimensional array. Some of the other schemes are linear array, X-grid, tree connection, and n-d cube (3-d cube given in Fig. 2.5). These network topologies are illustrated in Fig. 2.5.

Most of the MPC's provide a single interconnection scheme. However, some recent MPC's like the CM series allow multiple interconnection schemes. CM-1 has a mesh topology but also can switch to a tree and a relational graph. CM-2 has a hypercube topology and can switch to a mesh topology [3].

The topology of an MPC is highly important since the communication complexity may become the governing term in the time complexity of a parallel algorithm. This subject will be further discussed in the following sections.

Shared Memory Communications: PEs communicate through a common memory in this configuration. When a PE wants to pass a data item to another PE, it writes this data item to a memory location also accessible by the other PE. Therefore the local memories of PEs become common, i.e,. shared.

There are four models of memory access: exclusive-read and exclusive write (EREW), concurrent-read and exclusive-write (CREW), exclusive-read and conclusive-write (ERCW), and concurrent-read and concurrent-write (CRCW) [8]. Concurrency implies that an operation can be done on a memory location by more than one processor simultaneously; exclusiveness implies that only one processor can accomplish an operation on a memory location at any given time.

While CRCW is the most general model, it is impossible to implement it completely because of apparent write conflicts. Instead, concurrency in writing can be achieved by writing into the memory a certain result derived (like the addition of all or a logical operation between them or the maximum or minimum) from the data items sent by the PEs.

Unfortunately the shared memory configuration is very costly to realize since when one processor needs to gain access to a datum in memory, some circuitry is needed to create a path from that processor to the location in memory holding that datum. The cost of such circuitry is usually expressed as the number of logical gates required to decode the address provided by the processor [8]. For an M locations memory with N processors cost of circuitry is proportional to N\*f(M). This difficulty can be overcome by dividing memory into modules and using an interconnection network between the PEs and the memory modules. Nevertheless, such realizations leads to models even weaker than EREW. As an example to this, Burroughs Scientific Processor (BSP) uses a crossbar switch network as the intercommunication network.

Multiprocessor Computers: The instruction stream of an instruction parallel problem can be divided into multiple streams. Since these streams are usually few and complex, instruction parallel problems can not efficiently utilize fine grained parallelism of array processors.

Processors in a multiprocessing system cooperate semiautonomously with a loose communication between them. They run simultaneously under a single operating system. Multiprocessing systems with pipelining processors, or with pipelining and vector crunching processors, are very suitable for instruction parallel problems.

Multiprocessor systems are characterized by common sets of memory modules, shared peripheral devices, and I/O channels [1]. However, each processor will have its own local memory memory and devices which are completely allocated to it. Multiprocessor systems utilize the MIMD architecture in large.

The interprocessor communication schemes are time shared common bus, crossbar switch network, and multiport memories [1]. The selection and design of components of a multiprocessor system highly depends on its being a loosely or tightly coupled system. Note that a multiprocessor system still refers to a centralized processing scheme whereas a multicomputer system refers to a distributed processing scheme which comprises several autonomous computers.

Some of the commercially available multiprocessor systems are IBM 370 and 3080 series, Univac 1100 series, the Tandem Nonstop system, the HEP, the Cray X-MP, and the Cray-2 [1].

# 2.2 Parallel Algorithms

# 2.2.1 Design Approaches

Two approaches can be followed to design a parallel algorithm (All the discussions below are about the array processor parallel algorithms). These are:

- 1) To use an existing technique as it is. This approach can be divided into two different forms.

- a. To use a sequential algorithm for that technique and, to code as if the program will run on a sequential computer and let the compiler detect parallelizable parts of the code.

- b. To design a parallel algorithm for that technique and to code using a programming language providing special instructions for the utilization of the parallel processor.

- 2) To invent a new technique or to design a new algorithm utilizing a parallel processor heavily.

Usually, the first approach is followed, since designing a new technique will not be easy, and it is doubtful that a new design will be more efficient than the existing one.

Before giving examples for the above approaches, a hypothetical array processor and its pseudo programming language are described.

A Hypothetical Array Processor: The hypothetical array processor (HAP) has an architecture very similar to the array processor used in the software simulations of this study (See Appendix B for more information on the array processor used in this study). The HAP is an SIMD mesh array processor with P processing elements (PEs). All the PEs are controlled by a central control unit. A local RAM acts as a cache memory for the PEs, but being on the same chip with the processors, it is small in size. A large random access memory, called video RAM (VRAM), acts as a buffer between the local memory and the main memory. PEs can not communicate via VRAM because VRAM area accessible by each PE is different.

A PE can accomplish basic logical and mathematical operations. It has certain instructions to move data between its registers, its local memory, and the VRAM. It can send and receive data items from its immediate neighbours in north, east, west, south (NEWS), and four other diagonal directions simultaneously. (These four additional links along with NEWS links is called an X-grid. See Fig. 2.5 in Section 2.1.2 for an X-grid).

The HAP has a pseudo-language similar to the C programming language but also has instructions special to the array processor architecture. When such an instruction is detected during the execution, it is sent to the central control unit by the host computer. Below are some of the instructions from the HAP's pseudo-language.

SendToDirection1ReceiveFromDirection2(x,y): This is an instruction to receive a data item in variable x from the PE in direction Direction1 and to send a data item in variable y to the PE in the opposite direction to the direction Direction1, namely Direction2. Send and receive operations are simultaneous; therefore, if x and y are the same as x, x keeps the received value while the old value of x is sent.

AND: This instruction bitwise ANDs its operands.

OR: This instruction bitwise ORes its operands.

SetRoute(x): This instruction enables a wraparound or grid mode of routing; x can be "torus" or "grid". See Section 3.1.3 for an explanation of routing modes.

Other features of the HAP and its instruction set will be further explained in the subsequent sections if and when necessary.

A noise removal algorithm that removes white pixels from a dark background is a good example to the first of the parallel algorithm design approaches. This algorithm turns a pixel's value to black if all of its immediate NEWS neighbours are black. There are P pixels. The sequential code would be as in Fig. 2.6. In Fig. 2.6, old(i,j) holds the original value of pixel (i,j) and new(i,j) holds the computed value of pixel (i,j).

```

for (i=1 to \sqrt{P}){

for (j=1 to \sqrt{P})}{

new(i,j)=(old(i-1,j) and old(i+1,j) and old(i,j-1))

and old(i,j+1)) or old(i,j);

}

}

```

Fig. 2.6 A sequential noise removal algorithm.

A parallelizing compiler may detect the do loops and produce the executable file accordingly. The same algorithm can be written using the pseudo-parallel language of the HAP as an example to part (b) of the first approach. The parallel algorithm is given in Fig. 2.7

```

FOR ALL PEs (i,j)

SendToSouthReceiveFromNorth(old,north);

SendToWestReceiveFromEast(old,east);

SendToEastReceiveFromWest(old,west);

SendToNorthReceiveFromSouth(old,south);

new=(north and east and west and south)

or old;

```

Fig. 2.7 A parallel noise removal algorithm.

In Fig. 2.7, the variable old holds the original value of a pixel, and the variable new holds the computed value of a pixel. An example to the second approach can be the utilization of a new technique which can exploit the fine grain parallelism of array processors for the specific problem. In fact, such approaches are being developed [9].

There are three important points that must be considered while designing or realizing a parallel algorithm. The first is the computation cost measured, as the number of basic mathematical or logical operations performed; the second is is the number of processors and the network topology, and the third is the communication cost measured as the number of routing operations performed.

The time complexity, which is expressed in units of time, of a parallel algorithm is the addition of the times spent to pay these costs. Note that the communication cost does not exist in sequential algorithms, but can be the dominant term in the time complexity of a parallel algorithm. Therefore, the above mentioned points should be examined carefully for any algorithm.

The ultimate goal in designing a parallel algorithm is to get shorter solution times, hence, speedup with respect to the sequential implementations. To be able to achieve the largest speedup, one needs a methodology to design parallel algorithms. However, formal models are more than needed for the purposes of this study. The next two sections briefly present a method named directed acyclic graphs (DAGs) and how DAGs can be used to represent, design, develope, and analyze parallel algorithms.

At this point an acknowledgement is in place. The book "Parallel and Distributed Algorithms" by D. P. Bertsetekas and J. N. Tsitsiklis is one of the excellent books in its subject. The Sections 2.2.2 to 2.2.5 are largely based on the 1st chapter of this book.

## 2.2.2 Directed Acyclic Graphs

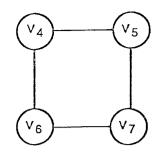

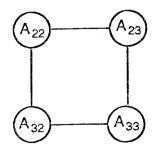

A directed graph (see Appendix B of [4] for more information about graphs) is a finite non-empty set N of nodes  $n_i$  and a collection A of ordered pairs of distinct nodes from this set. Each ordered pair of nodes  $(n_i, n_j)$  in A is called an arc. There is only a single arc between a pair of nodes, but this arc can either be unidirectional or bidirectional.

A path P in a directed graph is a sequence of nodes  $n_1,...,n_k$  for  $k \ge 2$  and a corresponding sequence of k-1 arcs such that the ith arc in the sequence is either  $(n_i,n_{i+1})$  (a forward arc) or  $(n_{i+1},n_i)$  (a backward arc). Nodes  $n_1$  and  $n_k$  are denoted as start and end nodes of P, respectively. A cycle is a path for which the start and the end nodes are the same. A positive cycle is a cycle for which all the arcs are forward.

A directed graph with no positive cycles is a directed acyclic graph (DAG) (see [4] for more information about DAGs). Thus, any path in a DAG graph can pass through a node once, and all the arcs in a path are both unidirectional and in the same direction.

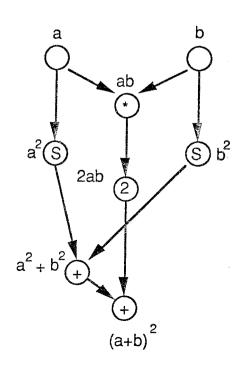

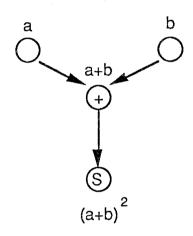

A DAG consists of also a set N of nodes  $\{n_1,...,n_N\}$  and a set A of directed arcs  $(n_i,n_j)$ . Each node  $n_i$  represents an operation and each arc represents a data dependency. An operation can be a boolean operation, an arithmetic operation, or a complicated operation like the execution of a subroutine. As an example, a DAG that represents  $(a+b)^2$  is given in Fig. 2.8.

Fig. 2.8 A DAG for  $(a+b)^2$ .

In a DAG, if  $\{n_i,n_j\} \in N_o$  and  $(n_i,n_j) \in A$ , then  $n_i$  is said to be a predecessor of  $n_j$ . The in-degree of node  $n_i$  is defined as the number of its predecessors and out-degree of node  $n_i$  is defined as the number of processors for which node  $n_i$  is a predecessor. Thus, an input node has an in-degree of zero and, an output node has an out-degree of zero.  $N_o$  is the set of nodes except the input nodes. A positive path is a sequence  $n_0,...,n_K$  of nodes where  $(n_i,n_{i+1}) \in A$  for i=0,...,K-1. K is called the length of a path. The depth D of a DAG is the maximum of the lengths of all the positive paths. D is positive in a DAG because of acyclicity and the positive path yielding D must obviously start at an input node and end at an output node. Note that the depth of the DAG in Fig. 2.8 is 3.

Now, assume that we have a pool of processors. Let each node  $n_i$  is assigned a processor  $P_i$  except the input nodes and, each processor is capable of performing the operation corresponding to that node in unit time. We further assume that communication between the processors is instantaneous.

To be able to represent an algorithm fully by a DAG, one also needs to fix when an operation is performed by which processor. This can be done via a *schedule*.

There are two constraints that must be imposed on a schedule.

- 1. A processor can perform at most one operation at a time. Therefore, if  $n_i, n_j \in N_o$  for  $i \neq j$  and  $t_i = t_j$ , then  $P_i \neq P_j$  where  $t_i$  denotes the time at which the  $i^{th}$  step of a schedule ends. Note that more than one processor can be active at a single step.

- 2. If  $(n_i, n_j) \in A$ , then  $t_j = t_i + 1$  (each operation takes unit time).

Since input nodes are assigned no processors, their completion times,  $t_{\rm i}$ , are zero.

After fixing  $P_i$  and  $t_i$ , a DAG is said to be scheduled, and the set  $\{(n_i, P_i, t_i) \mid n_i \in N_o\}$  is called a schedule S.

#### 2.2.3 Computation Complexity

The computation complexity is the time paid for the computation cost of an algorithm. The following notation will be used throughout the text:

A is a subset of real numbers  $\Re$ . For  $f: A \rightarrow \Re$ ,  $g: A \rightarrow \Re$ ,

- 1. f(x) = O(g(x)) implies, for any  $x \ge x_0$ ,  $f(x) \le cg(x)$ ,

- 2.  $f(x) = \Omega(g(x))$  implies, for any  $x \ge x_0$ ,  $f(x) \ge cg(x)$ ,

- 3.  $f(x) = \Phi(g(x))$  implies, for any  $x \ge x_0$ ,

$$c_1g(x) \ge f(x) \ge c_2g(x)$$

,

4. log(x) is logarithm base 2 of x,

where  $x_0, c, c_1, c_2 \in \Re^+$ .

In the above notation, O(.) puts an upper bound in the order of its argument,  $\Omega(.)$  puts a lower bound in the order of its argument, and  $\Phi(.)$  denotes the order of its argument.

For a DAG G and a schedule S,  $\{(n_i, P_i, t_i) \mid n_i \in N_o\}$ , of P processors, the time spent is  $\max(t_i)$ . The time complexity,  $T_p$ , of an algorithm is defined as the minimum of the times spent by any schedule S that realizes the same algorithm described by G using P processors.

Obviously, a schedule using infinitely many processors yields the minimum time complexity. However, note that for some  $P=P^*$ , where  $P^*$  is a positive finite integer,  $T_{\infty}=T_{p^*}$  (At least think of the case with one processor per each node in  $N_0$ ). Thus, the minimum

time complexity can be achieved with a finite number of processors. Therefore,  $T_{\infty}$  can be defined as

$$T_{\infty} = \min_{p \ge 1} T_p \tag{2.1}$$

Further note that  $T_1$  is the time complexity of a G and S pair simulated by a single processor and is equal to  $|N_0|$ . Therefore,

$$T_1 \ge T_p \ge T_{\infty} \tag{2.2}$$

Another important property of  $T_{\infty}$  is its equality to the depth D of its graph G. This is because a schedule can not be completed without traversing all the positive paths, and no positive path can be longer than the path with a depth D.

Now, let's state some properties of Tp:

1. Assume that there is a single output node and in-degree of each node is at most two. Therefore, for n input nodes

$$T_{\infty} \ge \log(n)$$

.

2. If q = c.p, then  $T_p \le c.T_q$ .

3. If

$$p = \Omega(\frac{T_1}{T_{\infty}})$$

, then  $T_p = O(T_{\infty})$ .

4. If

$$p = O(\frac{T_1}{T_{\infty}})$$

, then  $T_p = \overline{\Phi}(\frac{T_1}{p})$ .

These facts are of fundamental importance. The first puts a lower bound on the time complexity of any algorithm independent of the number of processors. The second states if the number of processors is increased by c, then the speedup would be less than c. The third states if the number of processors are bounded below in the order of  $T_1/T_\infty$ , then the speedup is bounded above in the order

of  $T_1/T_{\infty}$ . The fourth states if the number of processors are bounded above in the order of  $T_1/T_{\infty}$ , then the speedup is in the order of  $T_1/T_{\infty}$ .

The above discussions show us that we can reach  $T_{\infty}$  or  $T_{\infty}$  within a constant factor using a finite number of processors. Thus, it is tactful to develop a DAG and a schedule as if we have infinitely many processors, and then, adapt the algorithm to the available number of processors. Properties three and four also imply that the  $T_1/T_{\infty}$  is a limit point for the processor utilization. Indeed, one might utilize the processors best by choosing P equal to  $T_1/T_{\infty}$ .

Fig. 2.9 Another DAG for  $(a+b)^2$ .

Note that all of the above discussions are about the time complexity of a G and S pair but not the time complexity of the algorithm itself because the time complexity of an algorithm (or rather a technique) is implementation dependent. So anyone designing a parallel algorithm must choose a spatially decomposable technique and must be careful about the optimization of his/her implementation for an optimal time solution. Fig. 2.9 displays this fact by giving another DAG for  $(a+b)^2$  with a smaller depth.

#### 2.2.4 Communication Complexity

The communication complexity is the time paid for the communication cost of an algorithm. It is as important as the computation complexity since it may contribute to the time complexity of an algorithm more than the computation complexity. The communication cost for the array processors is considered under the following assumptions.

- 1. A node can use at most two of its incident links at a time. It can receive a message using one and send another message using the other. Furthermore, all the nodes initiate a communication at the same time, and send and receive simultaneously since the array processor is assumed to be running in SIMD fashion.

- 2. No time is spent to prepare a message or to wait in a queue. All packets are assumed to be of the same length and, always the same time is spent to pass any packet between neighbouring processors at any time.

These assumptions also apply well to the HAP.

An interconnection network can be represented as a graph G=(N,A) or as a topology. The nodes of a graph correspond to processors and the arcs correspond to the links. Interconnection network topologies can be assessed using the following criteria.

- 1. The diameter r of the network is the maximum distance between any pair of nodes and is measured as the number of links. For a network of diameter r, a packet can travel from one node to another in O(r) time.

- 2. Arc and node connectivity of a network is the number of arcs and nodes that must be deleted to make the network disconnected. The connectivity of a network is bounded above by the number of incident links to a node.

- 3. The *flexibility* of a network is defined as the capability of efficiently simulating algorithms designed for other topologies. To relieve the communication penalty, after dividing the main task into subtasks, each subtask must be assigned to a node considering that a node may need a value computed by another node. Such nodes must be chosen as immediate neighbours or be located as close as possible.

- 4. The communication delays (or costs) incurred for common communication problems like the single node and multinode broadcast problems are also important since such problems are encountered frequently in the parallel implementations of many numerical algorithms on array processors. These communication problems are explained below.

Single and multinode broadcast [4]: In the single node broadcast problem the same packet is sent from a single node to every other node. In the multinode broadcast each node broadcasts a packet to every other node.

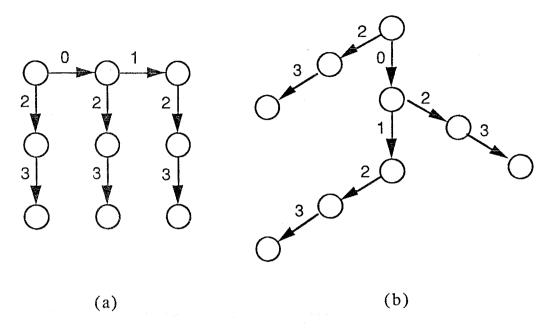

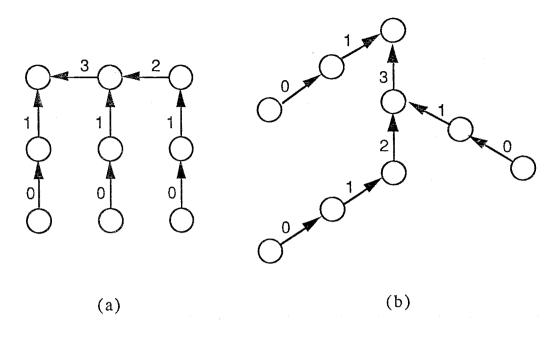

The single node broadcast problem can be solved by constructing a spanning tree at the given node. Choosing an optimal spanning tree, one can broadcast a packet from a single node to every other node in O(r) time (,or since r is the minimum distance between the farthest nodes, a packet between the farthest nodes travels r links at most). Fig. 2.10 (a) shows by simulation how the single node broadcast problem can be solved on a two dimensional three by three mesh, and Fig. 2.10 (b) shows the corresponding spanning tree.

The multinode broadcast problem requires a spanning tree per node. However this may result in timing conflicts since some spanning trees can possess the same links. Therefore, a more complex schedule that synchronizes link possessions must be designed.

Fig. 2.10 (a) A single node broadcast on a two dimensional mesh.

(b) The corresponding spanning tree.

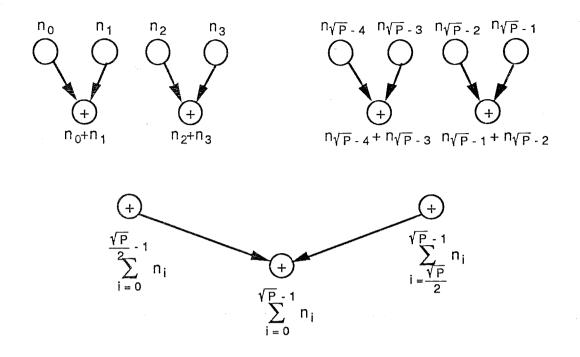

Single and multinode accumulation [4]: In the single node accumulation, a packet from every other node is sent to a single node. These packets are combined, e.g., added, ANDed, ORed, etc., on their way to this single node. Thus, a node on the routing path may receive more than one packet but it combines these packets, and sends a single packet to the next node. A multinode accumulation is a separate single node accumulation for each node.

The single node accumulation problem can be solved by using the optimal spanning tree of the single node broadcast problem. Running the single node broadcast schedule in reverse-time, all the packets can be accumulated at a single node in O(r) time. Thus, the single node accumulation and broadcast are said to be duals of each other. Fig. 2.11 (a) shows the simulation of a solution to the single node accumulation problem, and Fig. 2.11 (b) shows the corresponding spanning tree.

Fig. 2.11 (a) A single node accumulation on a two dimensional mesh.

(b) The corresponding spanning tree.

The multinode accumulation problem can be solved by running the multinode broadcast schedule in reverse-time.

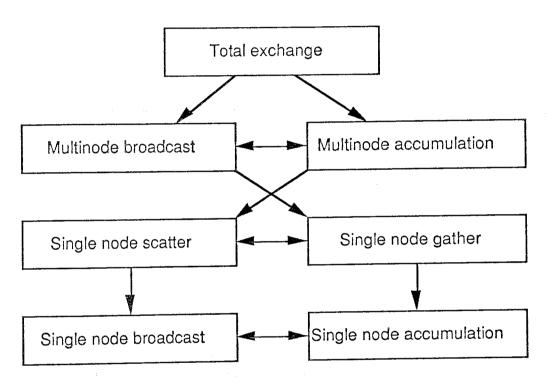

Single node scatter, single node gather, and total exchange [4]: Some algorithms require the sending of a separate packet from a single node to every other node. This is called a single node scatter problem. The dual of this problem is the separate collection of packets from every other node at a given node, and this is called a single node gather problem. Therefore, a solution to one of these is the reverse-time solution to the other. Indeed, an algorithm that schedules packet transmissions on each link and that properly takes queuing time into account is a solution to both of these problems.

In the total exchange problem, every node receives a separate packet from every other node, or, in other words, every node sends a separate packet to every other node. Therefore the the total exchange problem is the multinode version of either of the single node gather and scatter problems.

Note that in a multinode accumulation each node sends a separate packet to every other node, thereby solving the single node scatter problem. Also note that a total exchange is the generalization of a multinode broadcast if every node of the multinode broadcast sends a separate packet to every other node instead of the same packet. All of these relations are summarized in Fig. 2.12

Fig. 2.12 Hierarchical ordering of basic communication problems [4].

In Fig. 2.12 a directed arc from problem x to problem y indicates that an algorithm solving x can also solve y, and the optimal time for solving y is no more than the optimal solution time of x. A bidirectional arc indicates a duality relation.

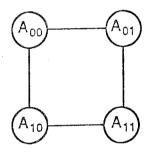

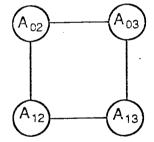

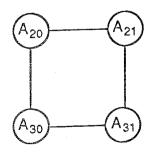

Some of the parallel algorithms described in Section 3.1 utilize a two dimensional n by n mesh array as n linear arrays of n nodes, and these algorithms include a single node accumulation and a single node broadcast.

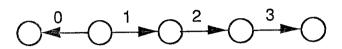

A single node broadcast or a single node accumulation on a linear array takes only (n-1) steps or O(n) time. Fig. 2.13 illustrates a solution by simulation for the single node broadcast problem on a linear array.

Fig. 2.13 A single node broadcast on a linear array.

# 2.2.5 Combined Complexities and Performance Measures