## **VLSI IMPLEMENTATION**

### OF AN

## **M-BAND WAVELET FILTER**

by

K.Yavuz Atabek

B.S. in Electrical and Electronics Option, Naval Academy, 1988

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfilment of the requirements for the degree of

Master of Science

in

Defence Technology Program, Electronics Option

Boğaziçi University

#### ACKNOWLEDGMENTS

I would like to express my deepest appreciation to Turkish Naval Forces and Prof. Dr. Yorgo İstefanopulos for starting such a program, thus allowing me to have an invaluable educational and social opportunity in Boğaziçi University. I would also like to express my gratitude to Prof. Dr. Emin Anarım for his continuous support.

Also, I would like to thank to my thesis supervisor Assoc. Prof. Dr. Sina Balkır and Assist. Prof. Dr. Günhan Dündar for their always being more than a teacher.

I am obliged for Assist. Prof. Dr. Cem Ersoy for his kind interest, great understanding and invaluable guiding.

I am also gratified for the friendship among the department people; especially for their help during my first year. In addition, I am grateful to the people in the ECAD laboratory, particularly, to our leader Prof. Dr. Ömer Cerid and dear friends Hakan Binici, İsmet Bayraktaroğlu and Alper Altınordu, for their patience and support.

Special thanks to Assoc. Prof. Dr. Hakan Çağlar and Prof. Dr. Gülen Aktaş for their kind supports.

I would like to thank my friends; Biltor Uluçay for encouraging me to attend this program and Gürcan Elbek for being a part of me like a family and to all my friends, generating an "EKIP spirit" in our lives.

Finally, I would like to appreciate my family for their invaluable, persistent support for all my life and my wife Zeynep Imre Atabek for being a color of my life and great support especially during this thesis period.

## ABSTRACT

In this thesis, an integrated circuit realizing M-Band wavelet transform and its perfect reconstruction (PR) counter part is designed. Although *M* is taken as 4 in the design, the M-Band Wavelet Transform has all four filters implemented with only one filter by the help of the shuffling property. With this method, it is possible to realize a VLSI design for the M-Band Wavelet Transform.

The circuit is designed to process 8-bit input signals. So, the filter has 8x8 signed multipliers and 16 bit full adders. After synthesis and optimization of the circuit, which was designed in a fully hierarchical manner in VHDL, its schematic diagram is obtained. From the schematic diagram, the chip layout of the circuit is created.

The circuit was designed, synthesized, optimized, simulated and its IC layout was created and prepared for IC processing by using the Mentor Graphics v.8.4.1 tools running on a Sun Sparc2 workstation. In the design, EuroPractice ES2 1  $\mu$ m CMOS target technology is used.

# ÖZET

Bu tez çalışmasında, M-Bantlı dalgacık dönüşümünü ve tam geri çatmasını gerçekleyecek bir tümleşik devre tasarlanmıştır. Tasarımda kullanılan süzgeç sayısı, M=4 olarak alındığından dolayı, 4 adettir. Buna karşın, M-Bantlı Dalgacık Dönüşümünün devrişime uygunluk özelliği ile 4 süzgeç yerine tek bir süzgeç kullanılarak, tümleşik devre olmaya uygun bir yapı elde edilebilmiştir.

Devre 8 bitlik giriş işaretleri için tasarlanmış olup, süzgeç içinde 8X8 işaretli çarpma yapan çarpıcılar ile 16 bitlik toplayıcılar kullanılmıştır. Tamamı hiyerarşik olarak, en basit kapı elemanına kadar VHDL'de tasarlanan devrenin, sentezleme ve eniyileme işlemlerinden sonra şematik görüntüsü ortaya çıkmıştır. Bu şemadan da tümleşik devre serimi (layout) yaratılmıştır.

Tasarımın yazılması, sentezlenmesi, eniyilenmesi, benzetiminin yapılması ve tümleşik devre seriminin çıkarılması için Sun Sparc2 iş istasyonu üzerinde çalışan Mentor Graphics yazılım paketi, sürüm 8.4.1'den yararlanılmıştır. Ayrıca tasarımda EuroPractice ES2 1 µm. CMOS gerçekleme teknolojisi kullanılmıştır.

## TABLE OF CONTENTS

| ACKNOWLEDGMENTS                                                   | iii        |

|-------------------------------------------------------------------|------------|

| ABSTRACT                                                          | iv         |

| ÖZET                                                              | v          |

| LIST OF FIGURES                                                   | <u>vii</u> |

| LIST OF TABLES                                                    | viii       |

| LIST OF ABBREVIATIONS                                             | ix         |

| 1. INTRODUCTION                                                   | 1          |

| 2. BACKGROUND                                                     | 3          |

| 2.1. Wavelets                                                     | 3          |

| 2.2. Image Compression And Encoding Techniques                    | 6          |

| 2.2.1. Image Data Requirements And Algorithm Performance Measures | 6          |

| 2.2.2. Elementary Compression Approaches                          | 7          |

| 2.2.3. Transform Approaches                                       | 7          |

| 2.2.3.1. Block Transform                                          | 7          |

| 2.2.3.2. Karhunen-Loeve Transform                                 | 8          |

| 2.2.3.3. Wavelet Transform                                        | 8          |

| 3. ARCHITECTURE                                                   | 9          |

| 3.1. Coefficients And Quantization                                |            |

| 3.2. Filter Structure                                             |            |

| 3.2.1. Analysis Filter                                            | 16         |

| 3.2.1.1. Switching Circuit                                        |            |

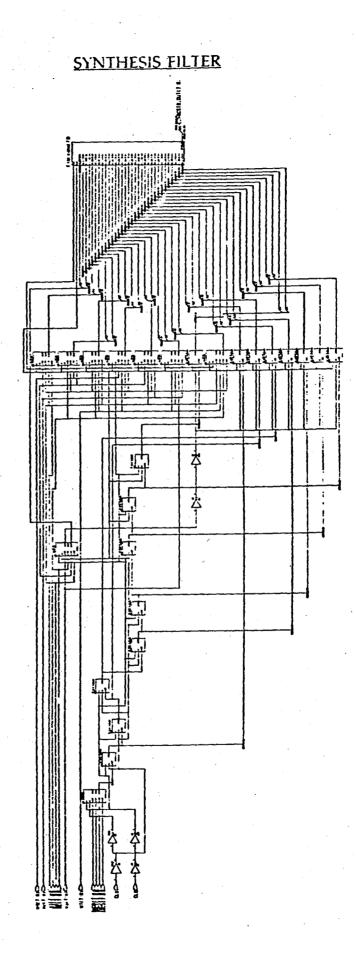

| 3.2.2. Synthesis Filter                                           |            |

| 4. SIMULATION                                                     | 20         |

| 5. CONCLUSION                                                     | 28         |

| REFERENCES                                                        | 29         |

| APPENDIX A VHDL                                                   | 32         |

| APPENDIX B C and Batch Codes                                      | 35         |

| APPENDIX C Schematic Diagrams                                     | 48         |

| LIST OF FIGURES | L | IS | Т | Ο | F | F | 1 | G | U | R | E | S |

|-----------------|---|----|---|---|---|---|---|---|---|---|---|---|

|-----------------|---|----|---|---|---|---|---|---|---|---|---|---|

| FIGURE 3.1.     | M-Band Coder and Decoder Structures     | .9   |

|-----------------|-----------------------------------------|------|

| FIGURE 3.2.     | Frequency Responses of the Filters      | . 10 |

| FIGURE 3.3.     | Hierarchy Listing                       | .11  |

| FIGURE 3.4.     | Quantization Errors                     | . 13 |

| FIGURE 3.5.     | Commonly Used FIR Filter Structure      | 15   |

| FIGURE 3.7.     | FIR Filter Used in This Design          | .15  |

| FIGURE 3.7.     | Architecture With Single Filter         | .16  |

| FIGURE 3.8.     | Switching Circuit                       | .17  |

| FIGURE 3.9.     | Inputs to the Synthesis Part            | 20   |

| FIGURE 4.1a.    | Timing of theAnalysis Filter (Part 1)   | .21  |

| FIGURE 4.1b.    | Timing of the Analysis Filter (Part 2)  | .22  |

| FIGURE 4.2a.    | Timing of the Synthesis Filter (Part 1) | 23   |

| FIGURE 4.2b.    | Timing of the Synthesis Filter (Part 2) | 24   |

| FIGURE 4.2c.    | Timing of the Synthesis Filter (Part 3) | 25   |

| FIGURE 4.3.     | Original Lenna input image              | .26  |

| FIGURE 4.4.     | Reconstructed image                     | 26   |

| FIGURE 4.5.     | Chip Layout of Synthesis Filter         | 27   |

| FIGURE Apx.A.1. | A VHDL Sample (4-Bit Multiplexer)       | .34  |

## LIST OF TABLES

| TABLE 3.1. | Original Analysis Filter Coefficients | 9    |

|------------|---------------------------------------|------|

| TABLE 3.2. | Analysis Filter                       | 14   |

| TABLE 3.3. | Synthesis Filter                      | . 14 |

| TABLE 3.4. | Switching Circuit Logic Table         | 17   |

| TABLE 3.5. | Synthesis Filter (2)                  | . 19 |

## LIST OF ABBREVIATIONS

| PR                  | Perfect Reconstruction                                      |

|---------------------|-------------------------------------------------------------|

| PR-QMF              | Perfect Reconstruction Quadrature Mirror Filter             |

| VHDL                | Very High Speed Integrated Circuit Description Language     |

| fs.                 | Sampling Frequency                                          |

| fc                  | Center Frequency                                            |

| Ь                   | Number of Quantization Bits                                 |

| coef <sub>max</sub> | Maximum Value of the Coefficients                           |

| qntzrnew            | New Quantizer Value used for coefmax                        |

| С                   | Multiplication Constant of the Filters                      |

| clk                 | Clock inputs of the circuits .                              |

| clr                 | Clear signal for Synthesis part, generated in Analysis part |

| clr2                | Clear signal for Analysis part                              |

|                     |                                                             |

## IN ANALYSIS PART (for Figure 4.1a-b)

| MBAND_IN    | Data input                                                 |

|-------------|------------------------------------------------------------|

| S13BUS(7:0) | Coefficient input to the 1 <sup>st</sup> tap of FIR filter |

| S11BUS(7:0) | Coefficient input to the 2nd tap of FIR filter             |

| S9BUS(7:0)  | Coefficient input to the 3 <sup>rd</sup> tap of FIR filter |

| S7BUS(7:0)  | Coefficient input to the 4 <sup>th</sup> tap of FIR filter |

| S5BUS(7:0)  | Coefficient input to the 5 <sup>th</sup> tap of FIR filter |

| S2BUS(7:0)  | Coefficient input to the 6 <sup>th</sup> tap of FIR filter |

| S1BUS(7:0)  | Coefficient input to the 7 <sup>th</sup> tap of FIR filter |

| S14BUS(7:0) | Coefficient input to the 8 <sup>th</sup> tap of FIR filter |

| S8BUS(7:0)  | Data input to the 1 <sup>st</sup> tap of FIR filter        |

| S15BUS(7:0) | Data input to the 2 <sup>nd</sup> tap of FIR filter        |

| S16BUS(7:0) | Data input to the 3 <sup>rd</sup> tap of FIR filter        |

| S10BUS(7:0) | Data input to the 4 <sup>th</sup> tap of FIR filter        |

| S12BUS(7:0) | Data input to the 5 <sup>th</sup> tap of FIR filter        |

| S3BUS(7:0)  | Data input to the 6 <sup>th</sup> tap of FIR filter        |

| S6BUS(7:0)  | Data input to the 7 <sup>th</sup> tap of FIR filter        |

| S0BUS(7:0)  | Data input to the 8 <sup>th</sup> tap of FIR filter        |

| N\$72(15:0) | FIR filter output (16 bit)                                 |

| ING0(7:0)   | Output of the 1 <sup>st</sup> band                         |

| ING1(7:0)   | Output of the 2 <sup>nd</sup> band                         |

|             |                                                            |

ix

| ING2(7:0) | Output of the 3 <sup>rd</sup> band |

|-----------|------------------------------------|

| ING3(7:0) | Output of the 4 <sup>th</sup> band |

#### IN SYNTHESIS PART (for Figure 4.2a-c)

- ING0(7:0) Input of the 1<sup>st</sup> band

- ING1(7:0) Input of the 2<sup>nd</sup> band

- ING2(7:0) Input of the 3<sup>rd</sup> band

- ING3(7:0) Input of the 4<sup>th</sup> band

- X(7:0) Mixed inputs, fed to the FIR filter

Coefficient input to the 1st tap of FIR filter S12BUS(7:0) Coefficient input to the 2nd tap of FIR filter S10BUS(7:0) Coefficient input to the 3<sup>rd</sup> tap of FIR filter S8BUS(7:0) Coefficient input to the 4<sup>th</sup> tap of FIR filter S6BUS(7:0) Coefficient input to the 5<sup>th</sup> tap of FIR filter S4BUS(7:0) Coefficient input to the 6<sup>th</sup> tap of FIR filter S2BUS(7:0) Coefficient input to the 7<sup>th</sup> tap of FIR filter S1BUS(7:0) Coefficient input to the 8<sup>th</sup> tap of FIR filter S14BUS(7:0) Data input to the 1st tap of FIR filter S7BUS(7:0) Data input to the 2nd tap of FIR filter S15BUS(7:0) Data input to the 3rd tap of FIR filter S16BUS(7:0) Data input to the 4<sup>th</sup> tap of FIR filter S9BUS(7:0) Data input to the 5<sup>th</sup> tap of FIR filter S11BUS(7:0) Data input to the 6<sup>th</sup> tap of FIR filter S3BUS(7:0) Data input to the 7<sup>th</sup> tap of FIR filter S5BUS(7:0) Data input to the 8<sup>th</sup> tap of FIR filter S0BUS(7:0) FIR filter output (16 bit) sdout(15:0)

RCSTR\_OUT Reconstructed output

## 1. INTRODUCTION

1

Wavelets are functions, like sines and cosines, that satisfy certain requirements. These functions may be used as basis functions in the representation of an arbitrary function, in a manner similar to Fourier analysis which uses sines and cosines as basis functions. We use this "wavelet transform" to represent certain functions which do not respond well to traditional Fourier analysis. For example, functions having sharp spikes or discontinuities will require a large number of Fourier basis functions if they are to be accurately represented. In contrast, if a wavelet basis is utilized, significantly fewer terms are required. Wavelets, like sinusoids, integrate to zero, but wavelets are localized in both frequency and time, whereas Fourier basis functions are localized only in frequency. This additional localization property of wavelets may be used to the advantage of those who are faced with problems involving large and noisy data sets. Such data sets can be transformed using wavelets so that the data is preserved in the form of the wavelet basis coefficients. Processing may then be carried out on the encoded data sets. The advantage of this approach is that it is much less computationally expensive than Fourier analysis.

In addition to the advantages of wavelets, recently, Perfect Reconstruction Quadrature Mirror Filter's (PR-QMF) have gained popularity in applications that involve multiresolution signal decomposition. Most significant ones have been in subband coding of digitized speech, still images and video signals for a variety of purposes such as encoding, efficient transmission, compression, and detection.

Especially in the last few years, the relationship between subband coders and the wavelet transform has been discovered. Mallat has shown the multiresolution form of the orthonormal wavelet transform is functionally equivalent to the analysis section of a subband coder with PR property [1].

For some applications it is desirable to see the wavelet transform as a signal decomposition onto a set of basis functions. In fact, basis functions called wavelets always underlie the wavelet analysis. They are obtained from a single prototype wavelet by dilations and contractions (scalings) as well as shifts. The prototype wavelet can be thought of as a bandpass filter and constant-Q property of the other bandpass filters (wavelets) follows because they are scaled versions of the prototype [2].

In traditional block coders, lengths of filters are taken to be the same as the length of each block (N=M). From multiresolution point of view, this limitation makes it difficult to achieve good time-frequency localization. An overlapping block transform termed the Lapped Orthogonal Transform (LOT) has been proposed by Cassereau [3]. Blocking effects at low bit rates are reduced through the use of basis functions that overlap in adjacent blocks with N=2M. The existence of PR-QMF solutions for two-band coders was shown by Smith and Barnwell [4]. In two band architectures, there are two types of filters; one is low-pass, the other is high-pass. However, in M-Band, the first filter is low-pass, the last one is high-pass and the others are band-pass filters.

Orthonormal M-channel wavelet bases can be obtained by iterating on the impulse response coefficients of the subband filters. Regularity of the basis functions depends on the locations of zeros in the low-pass branch transfer function and thus affects the design process [1].

Most implementations of M-band coders use Finite Impulse Response (FIR) filters. Although structures utilizing Infinite Impulse Response (IIR) filters have also been proposed for this purpose, stability of these proved to be difficult to achieve.

In this design, only one single FIR filter is used as a replacement for four filters representing the M=4 case by using the shuffling operation. Shuffling operation is performed by a group of switching circuits, which send one of four coefficients to the taps of the FIR filter at each clock, representing each filter for one clock cycle. This kind of shuffling operation results in downsampling by 4 automatically. A similar shuffling operation can make it possible for us to realize the synthesis part with PR property with only one FIR filter instead of four.

These single filter operations are also easy to be represented in C code. After shuffling operations being successful in C with real number filter coefficients, quantization is done for coefficients to be used in digital integer FIR filter.

The design is made via VHDL codes, with a hierarchical bottom-up methodology. After synthesis and optimization of the design, the whole circuit is mapped onto the ES2 (an IC vendor affiliate of the EuroPractice consortium) 1 $\mu$ m CMOS target technology. Therefore, standard cells used in the subcircuits of the design are from the ECPD10, 1 $\mu$ m. CMOS standard cell library of the ES2 foundry.

#### 2. BACKGROUND

This thesis is on the VLSI design of a wavelet transformer. Wavelet transformation is a kind of subband coding. The main goal in subband coding is the compression and is widely used for image or speech data transfer. General information about some special headlines, concerning these subjects will be given in this chapter.

#### 2.1. Wavelets

Fourier series, or expansion of periodic functions in terms of harmonic sines and cosines, date back to the early part of the 19<sup>th</sup> century when Fourier proposed harmonic trigonometric series [5]. The first wavelet (the only example for a long time!) was found by Haar early in this century. However the construction of more general wavelets to form bases for square-integrable functions was investigated in the 1980's, along with efficient algorithms to compute the expansion.

While linear expansions of functions are a classic subject, the recent constructions contain interesting new features. For example, wavelets allow good resolution in time and frequency, and should thus allow one to see "the forest and the trees". This feature is important for non-stationary signal analysis. While Fourier basis functions are given in closed form, many wavelets can only be obtained through a computational procedure (and even then, only at specific rational points). While this might seem to be a drawback, it turns out that if one is interested in implementing a signal expansion on real data, then a computational procedure is better than a closed-form expression!

If we look deeper to this non-stationary signal analysis subject [2]; the aim of the signal analysis is to extract relevant information from a signal by transforming it. Some methods make a priori assumptions on the signal to be analyzed; this may yield sharp results if these assumptions are valid, but is obviously not of general applicability. In this paper, we focus on methods that are applicable to any general signal. In addition, we consider invertible transformations. The analysis thus unambiguously represents the signal, and more involved operations such as parameter estimation, coding and pattern recognition can be performed on the "transform side," where relevant properties may be more evident.

Such transforms have been applied to stationary signals; that is, signals whose properties do not evolve in time. For such signals x(t), the natural "stationary transform" is the well-known Fourier transform.

$$X(f) = x(t) e^{-2j\pi f t} dt$$

(2.1)

The analysis coefficients X(f) define the notion of global frequency f in a signal. As shown in Formula 2.1, they are computed as inner products of the signal with sinewave basis functions of infinite duration. As a result, Fourier analysis works well if x(t) is composed of a few stationary components (e.g. sinewaves). However, any abrupt change in time in a non-stationary signal x(t) is spread out over the whole frequency axis in X(f). Therefore, an analysis adapted to *non-stationary* signals require more than the Fourier Transform.

The usual approach is to introduce time dependency in the Fourier analysis while preserving linearity. The idea is to introduce a "local frequency" parameter (local in time) so that the "local" Fourier Transform looks at the signal through a window over which the signal is approximately stationary. Another equivalent way is to modify the sinewave basis functions which are more concentrated in time (but less concentrated in frequency).

The recent surge of interest in the types of expansions discussed here is due to the convergence of ideas from several different fields, and the recognition that techniques developed independently in these fields could be cast into a common framework.

The name "wavelet" had been used with its current meaning first by J. Goupillaud, J. Morlet and A. Grossman [6]. In the context of geophysical signal processing they investigated an alternative to local Fourier analysis based on a single prototype function, and its scales and shifts. The modulation by complex exponential in the Fourier transform is replaced by a scaling operation, and the notion of scale replaces that of frequency. The simplicity and elegance of the wavelet scheme was appealing and mathematicians started studying wavelet analysis as an alternative to Fourier analysis. This led to the discovery of wavelets which form orthonormal bases for square-integrable and other function spaces by Meyer [7], Daubechies [8], Battle [9], Lemarié [10], and others. A formalization of such constructions by Mallat and Meyer created a framework for wavelet expansions called multiresolution analysis, and established links with methods used in other fields. Also, the wavelet construction by Daubechies [11] is closely connected to filter bank methods used in digital signal processing as we shall see.

Of course, these achievements were preceded by a long-term evolution from the 1910 Haar [12] wavelet (which, of course, was not called a wavelet back then) to work using octave division of the Fourier spectrum (Littlewood-Paley [13]) and results in harmonic analysis (Calderon-Zygmund operators [14]). Other constructions were not recognized as leading to wavelets initially.

Paralleling the advances in pure and applied mathematics were those in signal processing, but in the context of discrete-time signals. Driven by applications such as speed and image compression, a method called subband coding was proposed by Croisier, Esteban, and Galand [15] using a special class of filters called quadrature mirror filters (QMF) in mid 1970's, and by Crochiere, Webber and Flanagan [16]. This led to the study of perfect construction filter banks, a problem solved in the 1980's by several people, including Smith and Barnwell [17], Mintzer [18], Vetterli[19], and Vaidyanathan[20].

In a particular configuration, namely when the filter bank has octave bands, one obtains a discrete-time wavelet series. Such a configuration has been popular in signal processing less for its mathematical properties than because an octave band or logarithmic spectrum is more natural for certain applications such as audio compression since it emulates the hearing process. Such an octave-band filter bank can be used, under certain conditions, to generate wavelet bases, as shown by Daubechies [8].

In computer vision, multiresolution techniques have been used for various problems, ranging from motion estimation to object recognition. Images are successively approximated starting from a coarse version and going to a fineresolution version. In particular, Burt and Adelson proposed such a scheme for image coding in the early 1980's, calling it pyramid coding [21]. The importance of the pyramid algorithm was not immediately recognized. One of the reviewers of the original Burt and Adelson paper said, "I suspect that no one will ever use this algorithm again" [5]. This method turns out to be similar to subband coding. Moreover, the successive approximation view is similar to the multiresolution framework used in the analysis of wavelet schemes. In computer graphics, a method called successive refinement iteratively interpolated curves or surfaces, and the study of such interpolators is related to wavelet constructions from filter banks.

Finally, many computational procedures use the concept of successive approximation, sometimes alternating between fine and coarse resolutions. The multigrid methods used for the solution of partial differential equations are an example.

#### 2.2. Image Compression And Encoding Techniques

Image compression techniques basically involve the processing of the image prior to transmission or archiving [22]. The image data is then transmitted (or stored, in the archival application) and decoded, decompressed, or reconstructed prior to use. The heart of any of the image compression techniques centers on two entities:

1. The development of an image representation that removes a significant amount of the inherent redundancy in the image data. From a statistical viewpoint, we seek a transformation of the image data such that the transformed image consists, ideally, of uncorrelated data.

2. The achievement of a reconstruction scheme that 'undoes' the compression or encoding scheme. Most important, this reconstruction scheme, together with the chosen compression technique, is chosen to minimize subjective distortion in the resulting image.

### 2.2.1. Image Data Requirements And Algorithm Performance Measures

As a preliminary example, consider an image with 512 x 512 pixel spatial resolution and 8 bits (256 levels) intensity resolution. This represents 0.25 Mbyte (1M byte = (1 K byte)2; 1 K = 1024) of image data. At what is sometimes referred to as "real-time" rates (i.e., the R-170 frame rate) this amount of data over time represents a data rate of almost 63 million bits per second. Compression techniques seek to reduce this data rate.

Measures of compression algorithm performance are basically composed of three entities:

1. A quantitative measure of the amount of data reduction expressed in terms of memory bits per image or bits per pixel (e.g., reduced to 1 bit/pixel, etc.).

2. A quantitative or qualitative assessment of the degradation (if any) of the image data.

3. A measure of the algorithm complexity, particularly with respect to compression/expansion processing speed.

#### 2.2.2. Elementary Compression Approaches

An obvious approach for the reduction of image data is to undersample the image. The implicit assumption in subsampling is that adjacent lines or adjacent pixels contain information that is so highly correlated it may be assumed to be replicated and that the replication of this data during the reconstruction phase results in an image that is, subjectively speaking, close to original. Subsampling methods exist in several forms; the most popular is to sample one of the image frame fields and discard the other. Most home videocassette recorders (VCRs) employ this technique.

#### 2.2.3. Transform Approaches

#### 2.2.3.1. Block Transform

If the majority of the image content could be represented using relatively few of (some) transform basis functions, the image could be transmitted or archived in transformed form, with a significant data reduction. This type of approach was considered in Chapter 3. Other approaches partition the image into smaller regions, or blocks, and encode these blocks of local data. Block coding of data usually results in greater success, since the likelihood of a small block containing highly correlated data is probably greater in a local region than over the entire image. [22]

#### 2.2.3.2. Karhunen-Loeve Transform

Another popular transform is known as the Karhunen-Loeve (KL) principal component, or Hotelling transform. In contrast with the deterministic approaches treated previously, the KL transform is based on the statistical characterization of the image data. The KL transformation is based on representation of a sampled image function as a vector and statistical characterization of his vector to determine ("principal") components which represent most of the image intensity variation. [22]

#### 2.2.3.3. Wavelet Transform

Perhaps the biggest potential of wavelets has been claimed for signal compression [2]. Since discrete wavelet transforms are essentially subband coding systems, and since subband coders have been successful in speech and image compression, it is clear that wavelets will find immediate application in compression problems. The only difference with traditional subband coders is the fact that filters are designed to be regular (that is, they have many zeroes at z=0 or z=). Note that although classical subband filters are not regular, they have been designed to have good stopbands and thus are close to being "regular", at least for the first few octaves of subband decomposition.

It is therefore clear that drastic improvements of compression will not be achieved so easily simply because wavelets are used. However, wavelets bring new ideas and insights. In this respect, the use of wavelet decompositions in connection with other techniques (like multiscale edges or vector quantization [23]) are promising compression techniques which make use of the elegant theory of wavelets.

### 3. ARCHITECTURE

Single filter architecture is the only way to make a VLSI design for a wavelet filter. Simple ideas make it possible to design the circuit with one filter, instead of four. Otherwise silicon area will be too large and this will increase the cost considerably. In this chapter, the architecture of the design will be explained in detail.

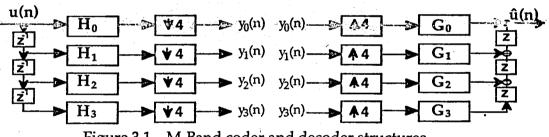

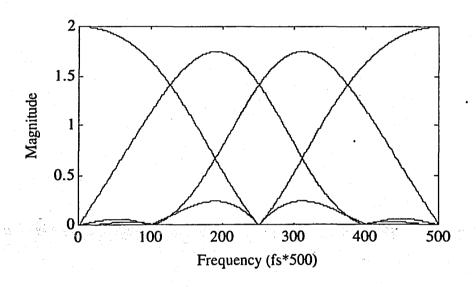

We can separate the architecture into two parts; analysis (coder) part; m-band subband coder structure and synthesis (decoder) part; perfect reconstruction structure. Architectures are basically, the realization of the block diagrams proposed in [24]. As in the Figure 3.1., the structures consist of 4 filters. H0; which stands for  $\Psi_1$  in Table 3.1. is a low pass filter, H1; which stands for  $\Psi_2$ , is a band pass filter with small  $f_c$ , H2; which stands for  $\Psi_3$ , is also a band pass filter but with a higher  $f_c$  and H3; which stands for  $\Psi_4$ , is high pass filter. The frequency responses of the filters are presented in Figure 3.2..

| Figure 3.1. | M-Band | coder and | decoder | structures |

|-------------|--------|-----------|---------|------------|

|             |        |           |         |            |

| n     | Ψ1(ν)              | Ψ2(ν)        | Ψ3(v)        | Ψ4(ν)                                   |

|-------|--------------------|--------------|--------------|-----------------------------------------|

|       |                    |              | 0.00/105/14  | 0.0000000000000000000000000000000000000 |

| 0     | -0,067371764       | -0,094195111 | -0,094195111 | -0,067371764                            |

| 1     | 0,094195111        | 0,067371764  | -0,067371764 | -0,094195111                            |

| 2     | 0,40580489         | 0,56737176   | 0,56737176   | 0,40580489                              |

| -3    | 0,567371 <b>76</b> | 0,40580489   | -0,40580489  | -0,56737176                             |

| 4     | 0,56737176         | -0,40580489  | -0,40580489  | 0,56737176                              |

| 5     | 0,40580489         | -0,56737176  | 0,56737176   | <b>-0,</b> 40580489                     |

| 6     | 0,094195111        | -0,067371764 | -0,067371764 | 0,094195111                             |

| 7     | -0,067371764       | 0,094195111  | -0,094195111 | 0,067371764                             |

| -<br> |                    |              |              |                                         |

In such a sub-band filtering application, filters acting as M-band coders must have certain properties. The analysis filter generates overlapping terms during the coding operation and the synthesis filter must be able to decode these terms. Only by this way, input of the analysis (coder) part u(n) can be obtained at the output of the synthesis (decoder) part as  $\hat{u}(n)$  (Figure 3.1.); PR property. Because of that, the coefficients of the synthesis filter can be derived from the coefficients of the analysis filter [24]. Therefore the structures of the filters used either in the analysis or the synthesis are identical.

Figure 3.2. Frequency Responses of the Filters

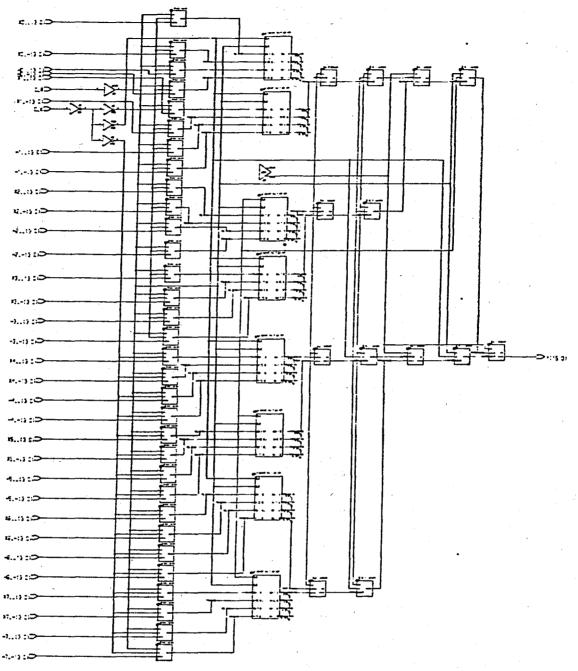

Architecture consists of 37 modules; written in VHDL, synthesized and optimized by Mentor Graphics AutoLogic software package. These modules have a hierarchical order among themselves and hierarchy listing is presented in Figure 3.3.. In design process, we synthesized and optimized modules from very bottom to topmost level one by one. If you happen to optimize the topmost module directly, AutoLogic will optimize a lower level module as much as the number of times it's used in the circuit. Since AutoLogic does not close the optimization file of the lower level module before the optimization of all design is finished, the program needs to open another optimization file for that module during its next usage. For example; after synthesizing an FIR filter, you can face 368 synthesis versions of an AND gate. Certainly this takes a lot more time and a lot more harddisk space. VHDL listings for all of the modules used in the design is represented in Appendix A directory of floppy disk.

11

rcstr(/) / opt\_s eight2\_tap\_signed\_fir(I\$286) / schematic eight\_bit\_signed\_mul(I\$31) / schematic dff\_positive(G108) / opt\_s eight\_bit\_pipelined\_mul(G4) / opt\_s dff\_positive(G25) / opt\_s four\_bit\_cla\_adder(G5) / opt\_s and2(G8) / opt\_s and3(G11) / opt\_s and4(G10) / opt\_s and5(G14) / opt\_s full\_adder\_special(GS\_4) / opt\_s and2(G3) / opt\_s xor2(G1) / opt\_s or2(G6) / opt\_s or3(G9) / opt\_s or4(G13) / opt\_s or5(G18) / opt\_s four\_bit\_positive\_latch(G20) / opt\_s radix16\_cell(G1) / opt\_s four\_bit\_cla\_adder(G1) / opt\_s and2(G8) / opt\_s and3(G11) / opt\_s and4(G10) / opt\_s and5(G14) / opt\_s full\_adder\_special(GS\_4) / opt\_s and2(G3) / opt\_s xor2(G1) / opt\_s or2(G6) / opt\_s or3(G9) / opt\_s or4(G13) / opt\_s or5(G18) / opt\_s four\_bit\_wallace\_mul(G2) / opt\_s and2(G0) / opt\_s full\_adder(G20) / opt\_s and2(G3) / opt\_s or2(G5) / opt\_s xor2(G1) / opt\_s eight\_bit\_twoscomp(G177) / opt\_s dff\_positive(G2) / opt\_s four\_bit\_cla\_adder(G10) / opt\_s and2(G8) / opt\_s and3(G11) / opt\_s and4(G10) / opt\_s and5(G14) / opt\_s full\_adder\_special(GS\_4) / opt\_s and2(G3) / opt\_s xor2(G1) / opt\_s or2(G6) / opt\_s or3(G9) / opt\_s or4(G13) / opt\_s

or5(G18) / opt\_s four\_bit\_positive\_latch(G1) / opt\_s twobyone\_mux(G35) / opt\_2\_s xor2(G6) / opt\_s sixteen\_bit\_twoscomp(G14) / opt\_s sixteen\_bit\_cla\_adder(G18) / opt\_s and2(G8) / opt\_s four\_bit\_cla\_adder(G1) / opt\_s and2(G8) / opt\_s and3(G11) / opt\_s and4(G10) / opt\_s and5(G14)·/ opt\_s full\_adder\_special(GS\_4) / opt\_s and2(G3) / opt\_s xor2(G1) / opt\_s or2(G6) / opt\_s or3(G9) / opt\_s or4(G13) / opt\_s or5(G18) / opt\_s four\_bit\_mux(G15) / opt\_s or2(G11) / opt\_s sixteen\_bit\_positive\_latch(G19) / opt\_s xor2(G11) / opt\_s xor2(I\$34) / opt\_s four\_bit\_positive\_latch(G33) / opt\_s sixteen\_bit\_cla\_adder(G26) / opt\_s and2(G8) / opt\_s four\_bit\_cla\_adder(G1) / opt\_s and2(G8) / opt\_s and3(G11) / opt\_s and4(G10) / opt\_s and5(G14) / opt\_s full\_adder\_special(GS\_4) / opt\_s and2(G3) / opt\_s xor2(G1) / opt\_s or2(G6) / opt\_s or3(G9) / opt\_s or4(G13) / opt\_s or5(G18) / opt\_s four\_bit\_mux(G15) / opt\_s or2(G11) / opt\_s sixteen\_bit\_positive\_latch(G12) / opt\_s eight\_bit\_positive\_latch(G14) / opt\_s m\_band\_switch\_1(I\$1912) / opt\_s eight\_bit\_4in\_or(G7) / opt\_s eight\_bit\_tgate\_2sel(G3) / opt\_s m\_band\_dff\_positive(G1) / opt\_s

Figure 3.3. Hierarchy Listing

#### 3.1. Coefficients and Quantization

As represented in Table 3.1., original filter coefficients consist of the combination of 8 real numbers. To use them in this design, we have to quantize them. Quantization for integer FIR filters is usually done by rounding the number [25] which is calculated by Formula 3.1 where  $coef_{max}$  is the maximum

## $coef_{quant} = ((2^{b-1})-1) * (coef_{orig}) / (coef_{max})$ (3.1)

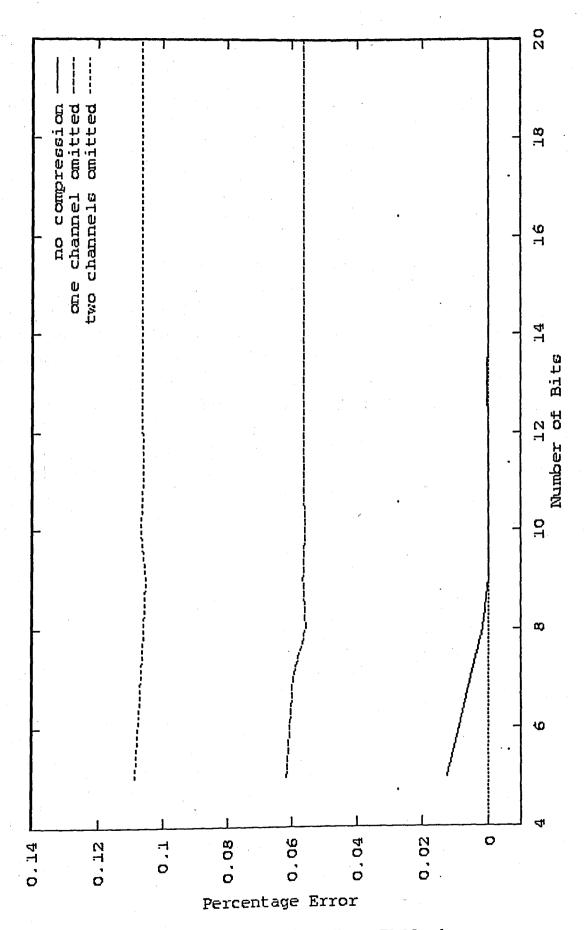

value among the coefficients, *coeforig* is the original coefficient to be quantized, b is the number of bits to quantize and *coefquant* is the resulting quantized coefficient. We wrote a C code for deciding the value of b (Appendix B). In this program, first we quantize both the synthesis and analysis part coefficients and the channel between these parts by the same number of bits. Then analyze the difference between the original input to the analysis part and the output of the synthesis part and calculate the RMS and percentage errors [26]. We repeat this procedure for numbers between 5 and 20. Calculated values are analyzed and represented in Figure 3.4..

In Figure 3.4., the lines represent the percentage errors for the whole design (from analysis part to synthesis part) for different bit numbers of quantization; the solid line, close to the bottom, represents the errors for no compression case. In this case, all four channels are used in the reconstruction. The dashed line, in the middle, represents the percentage error generated when 25% compression is applied (high-pass filter is omitted). And as the last case, 50% compression' is applied (high-pass filter and band-pass filter with higher frequency response are omitted) and the error for this case is represented in small dashed line, at the top.

Figure 3.4. Quantization Errors for Different Bit Numbers

The aim of proper operation with less count of transistors drove us to implement the design with the minimum number of bits. So that, we decided to take b as 8. As it can be seen from the graph in Figure 3.4., at 50% compression in 8 bit case, the percentage error does not exceed the value of 10.5%. This error value is really comparable for such a case.

$$C = (2^{b-1}) - 1 / (coef_{max})$$

(3.2a)

$$C = (2^7) - 1/0.56737176 \tag{3.2b}$$

$$C = 223.839$$

(3.2c)

After quantization, each coefficient is multiplied by a constant number (3.2c). However, the output has to be scaled by this number at the end. If this number is not a power of two, this scaling can be problematic and we cannot get the same input, but a scaled one, after the PR stage. Therefore, the number is chosen as the closest power of two by using the Formula 3.3a-d, so that scaling can be done only by a shift right by 7 operation. The coefficients quantized by this method are represented in Table 3.2. and Table 3.3. and are used in the design.

$$C = (2^{b-1}) - 1 / (qntzr_{new})$$

(3.3a)

$$qntzr_{new} > coef_{max}$$

(3.3b)

for C=256 = 0.49609 (not acceptable) (3.3c) *qntzr<sub>new</sub>* = 0.99218 (acceptable) for C=128 qntzr<sub>new</sub> (3.3d)

| Table 3.2. Analysis Filter           |                                              |                                              |                                              |                                                    | - |                                      | Table 3.                                     | 3. Synth                                     | esis Filte                                   | r                                            |

|--------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------------|---|--------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|

| n                                    | Ψ1(r                                         | ı) Ψ2(v                                      | ') Ψ3(r                                      | ι) Ψ4(v)                                           |   | n                                    | Ψ1(n)                                        | ) Ψ2(v)                                      | Ψ3(n)                                        | Ψ4(ν)                                        |

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | F7<br>0C<br>34<br>49<br>49<br>34<br>0C<br>F7 | F4<br>09<br>49<br>34<br>CC<br>B7<br>F7<br>0C | F4<br>F7<br>49<br>CC<br>CC<br>49<br>F7<br>F4 | F7<br>F4<br>34<br>B7<br>49<br>CC<br>0C<br>0C<br>09 |   | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | F7<br>0C<br>34<br>49<br>49<br>34<br>0C<br>F7 | 0C<br>F7<br>B7<br>CC<br>34<br>49<br>09<br>F4 | F4<br>F7<br>49<br>CC<br>CC<br>49<br>F7<br>F4 | 09<br>0C<br>CC<br>49<br>B7<br>34<br>F4<br>F7 |

#### 3.2. Filter Structure

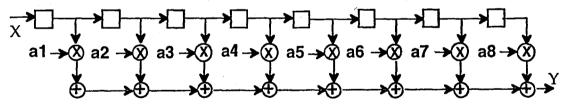

With an FIR filter structure like the one in Figure 3.5., inputs should wait for the output belongs to the previous input. This structure slows down the operation speed of all the system and so FIR filter becomes the bottleneck of the system. In this design, the structure shown in Figure 3.6.; which depicts the pipelining-scheme, is used. In this structure inputs do not need to wait output of the previous input. All operations are being done while the inputs are flowing through the pipeline. The pipeline depth of the filter should be so that it runs properly with clock frequency of the circuit. Therefore, the FIR filter is not the system speed defining element anymore, but the multipliers are.

Since the circuit is designed for 8 bit operation, Radix-2<sup>n</sup> multipliers [27] performing 8x8 signed multiplication are used. Although single clock is used throughout the design, an inverted (with 180° phase shift) clock is used in the multipliers to avoid setup and hold violations at data read times. These multipliers have a pipeline depth of 8 and they are capable of running in excess of 33 MHz.

The adders are 16 bit carry look ahead adders. Finally, eight and sixteen bit D-flip flops with reset are used as delay elements. Both of these elements introduce an additional pipeline depth of one clock pulse to the circuit.

Figure 3.5. Commonly Used FIR Filter Structure

Figure 3.6. FIR Filter Used in this Design

#### 3.2.1. Analysis Filter

According to the actual algorithm, inputs are fed to the filters with a delay sequentially (multiplying by  $Z^{-1}$ ) (Figure 3.1.). After filtering, downsampling by 4 operation is performed for the outputs. This makes the filtering operations useless by 3 in 4 time. Actually, filter rests for 3 cycles in a 4 cycle operation and this situation is valid for all filters (again) with a cycle delay sequentially. This means, at one cycle only one of the filters can have a valid output. Therefore, operation of only that filter can be performed while the others are resting (performing downsampling). This situation is led us to accomplish the whole operation with a single filter, instead of four.

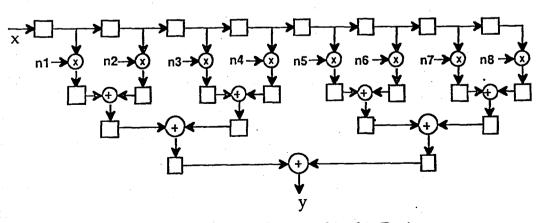

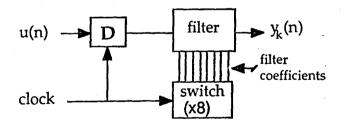

The analysis part is designed with a single FIR filter as in the architecture in Figure 3.7., representing the coder structure in Figure 3.1. [28]. The input signals are fed to the filter, through a D-flip flop which controls the flow of inputs.

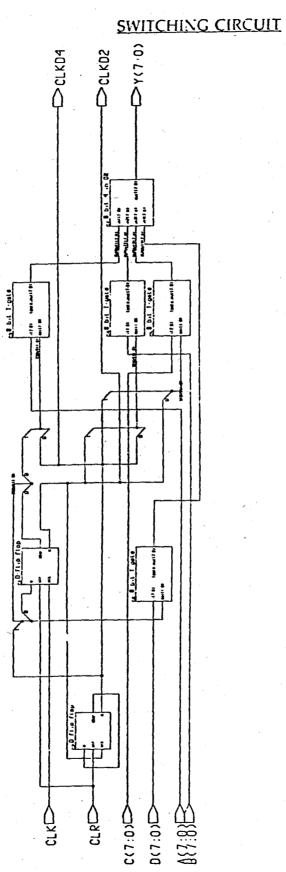

The switching circuit in Figure 3.7., designed with four transmission gates and two D-flip flops as shown in Figure 3.8., sends a different set of coefficients of filters on each clock cycle to make the filter acts as four filters. Consequently, with this technique, the chip area is reduced by a factor of 4. All of these shuffling operations, being done by the switching circuit in Figure 3.7. will be described in detail in the next subsection.

Figure 3.7. Architecture with single filter

The outputs can be separated by knowing that the first output belongs to the first FIR filter and others follow it sequentially. Therefore, we can apply compression by omitting some of the channels before transmission; 25% by omitting the last high pass filter outputs, 50% by omitting the last two channels (high pass and band pass).

#### Switching Circuit

Figure 3.8. Switching Circuit

As it has been introduced before, switching circuit consists of four 8-bit transmission gates and two 8-bit D-flip flops. Actually, the function of this circuit has the greatest importance among all submodules. Switching circuit performs the synchronization of inputs and coefficients to meet each other properly.

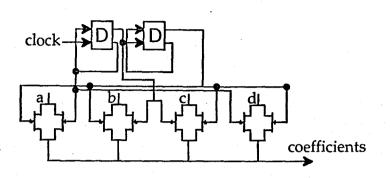

The design has 8 switching circuits (one for each filter tap). Two D-flip flops runs as counter for transmission gates, such that at each clock pulse, one of four coefficients (a, b, c, d) for each band are sent to the FIR filter. Logic table for transmission gate selection is on the following Table 3.4..

| <u>clk</u> | out1 | out1 | out2 | <u>Xgate</u> |

|------------|------|------|------|--------------|

| 1          | 1    | 0    | 1    | a            |

| 0          | 1    | 0    | 1    | а            |

| 1          | 0    | 1    | 1    | b            |

| 0          | 0    | 1    | 1    | b            |

| 1          | 1    | 0    | 0    | C            |

| 0          | 1    | 0    | 0    | с            |

| 1          | 0    | 1    | 0    | d            |

| 0          | 0    | 1    | 0    | d            |

Table 3.4. Switching Circuit Logic Table

#### 3.2.2. Synthesis Filter

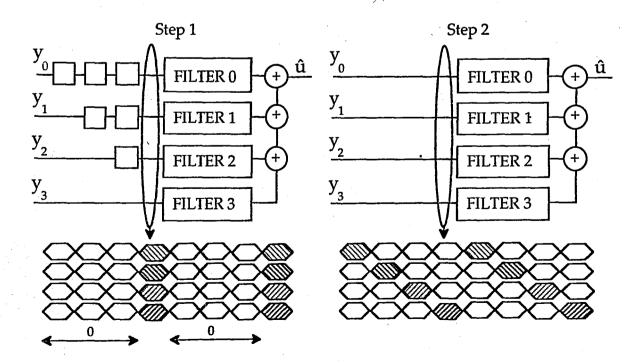

An FIR filter working as the inverse of analysis filter, like in Table 3.3., acts as the synthesis filter. As shown in the decoder part of Figure 3.1., four channel inputs coming from the analysis part are upsampled by 4 since M=4 and fed through the corresponding filters. Then the outputs of the filters are to be added to each other with a time shift backward (multiplying by Z). A similar chip area saving, like in the analysis part can be accomplished here as well; the operation procedure mentioned above, is equivalent to the case where inputs are delayed properly (for 1<sup>st</sup> filter 3 clock cycles, for 2<sup>nd</sup> 2, for 3<sup>rd</sup> 1 and for 4<sup>th</sup> 0) and filter outputs added simultaneously as shown in step 1 of the Figure 3.9.. In this representation, there are four filters.

The inputs will be processed in the filters only at  $1^{st}$ ,  $5^{th}$ ,..., $(4n+1)^{th}$  clock cycles where *n* is the number of the input. During three clock cycle periods, filters will become idle. To overcome this drawback, the delay elements in front of the filters can be neglected and coefficients can be shifted right by that amount (Step 2 of the Figure 3.9.). Now there are four filters with shifted coefficients, but at most two of the coefficients for each filter will be functional while only two of the filter taps are with data. Therefore, those functional ones at one time can be put together and form four different filters (Table 3.5.).

Figure - 9 Inputs to the synthesis part

| n                                    | Ψı(n)                                        | Ψ2(n)                                        | Ψ3(n)                                                             | Ψ4(n)                                                    |

|--------------------------------------|----------------------------------------------|----------------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------|

| 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 09<br>F4<br>OC<br>F7<br>B7<br>CC<br>34<br>49 | 0C<br>F7<br>F7<br>8C<br>34<br>49<br>49<br>34 | CC<br>49<br><b>37</b><br><b>34</b><br>F4<br>F7<br>09<br><b>8C</b> | 49<br>CC<br>CC<br>49<br>F7<br>F4<br>F4<br>F4<br>F4<br>F7 |

Table - 5 Synthesis Filter (2)

1<sup>st</sup> Filter Coeff. 3 <sup>rd</sup>Filter Coeff.

2<sup>nd</sup>Filter Coeff. 4<sup>th</sup>Filter Coeff.

Outputs of the analysis part can be fed through the synthesis part without separating to 4 channels. Initially, synthesis part will not respond for 4 clock cycles, till the first input of the 4<sup>th</sup> filter arrives. After that, the inputs corresponding to the taps of the filter will be held for 4 clock cycles and operated on by all the corresponding filters at each clock cycle sequentially. Here, different from other FIR filter operations, inputs are not flowing through the filter at each clock cycle, but they stay at the corresponding taps for four clock cycles while the coefficients for four different filters are shuffling at the taps of the filter. This coefficient shuffling operation is like inputs have been upsampled by 4 and flowing through the filters related to the ones they had been generated by in the analysis filter. While this process is being executed, the inputs coming from the analysis filter are also fed through the filter without touching the taps. After 4 clock cycles, corresponding inputs will be held at the taps and the similar operation will continue. As a result, upsampling by 4 is being done automatically and all reconstruction operation is being realized with a single filter.

These operations are done by the help of two switching circuits as it's been mentioned in analysis part. One of the switching circuit is in front of the input buses; to keep inputs for 4 clock cycles at the taps of the filter while actual inputs flowing through the circuit. The second one acts as the same of the analysis part switching circuits and like in the analysis part we have 8 this type of switches here as well.

#### 4. SIMULATION

First, a C program (Appendix B and Appendix B directory of floppy disk) is written to simulate the operation of the filters in Figure 3.1. (mb.c and rc.c) with coefficients represented by real numbers. After achieving Perfect Reconstruction with real coefficients, quantization process begins. Again a C program is written to quantize the coefficients (qnt.c) and the channel between analysis and synthesis parts (channel.c) and another to calculate the value of error (calc.c). A couple of batch codes are written to run all these programs automatically for different conditions (comp10, comp11, comp15). Results for these steps are represented in section 3.1.

After C language steps, similar operations representing the originals, as mentioned earlier, are written in VHDL (Appendix A) and simulated to observe that these operations are performed properly. Logic synthesis and optimization are done using the 1µm ES2 target technology from bottom to top. After each resulting schematic circuit a simulation is done to check the functions of the module. And finally two resulting top-level schematics (analysis and synthesis parts) are simulated to verify the proper operation. In all these steps, Mentor Graphics tools (Design Architect, Autologic, Quicksim,...) and a C compiler running on a Sun Sparc2 work station are used. If we overall the steps;

- Writing and running C program

- Writing VHDL codes

- Simulating VHDL codes

- Synthysizing and optimizing VHDL codes

- Simulating resulting schematic circuit

- Creating the chip layout

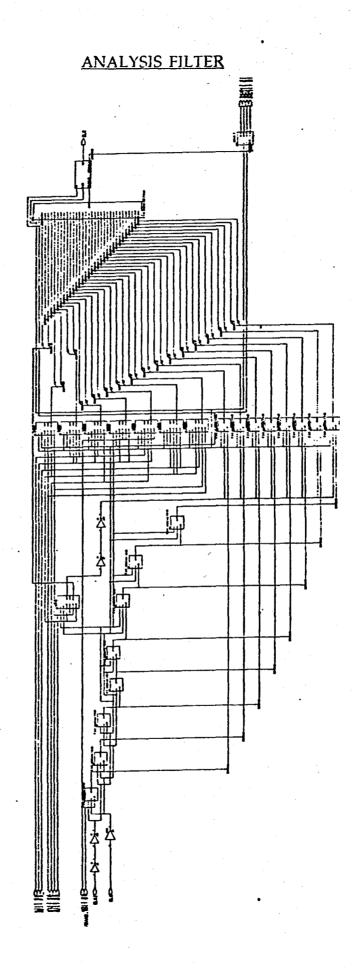

In simulation of the analysis filter, first, a small part of an image is fed through the filter. A clock with 33 MHz frequency is used during the simulations. The analysis circuit gives out four channel separated outputs and a clear signal (Appendix C), just before the first output comes, to activate the synthesis filter (Figure 4.1a-b). This output is in suitable format for the input of the synthesis filter (Appendix C). The inputs and outputs of the synthesis filters are shown in Figure 4.2.a-b-c.

| /CL           | κ, Γ                |          |                | <u> </u>    | []. r           |         | · [ — ]        | اا                      |           | <b>ر</b>                  | <b>[]</b>   |              |

|---------------|---------------------|----------|----------------|-------------|-----------------|---------|----------------|-------------------------|-----------|---------------------------|-------------|--------------|

| /CLR          | 2 + ]               | +        | L]* L<br>+     | _] *[_<br>+ | 」 (±)<br>+      |         | ] +L           | _] [ <u>+</u>           |           | _] + [_                   | _ t         |              |

| ,IBAND_IN(7.0 | ۰ L                 | <br>     | X44 + X42      |             |                 | +<br>   | +<br>56 + \/ 5 | •<br>0 \ <del>6</del> 2 | +<br>     | $\frac{+}{50 + \sqrt{4}}$ | +<br>4 ¥4   | +<br>2 \/46  |

| /S13BUS(7:0   | L                   | _/       | F4 <b>F</b> 4  |             |                 | F4 + F4 | /<br>/F7       |                         |           | <u>~</u> ∧_<br>∕_=_7      |             | ¥F4 + X      |

| /S11BUS(7:0   | )<br>(F4)           |          | 09 <b>F</b> 7  | <br>        |                 | 09 + F7 |                | _/<br>                  | 09 + F7   | /<br>                     | <br>        |              |

| /S9BUS(7:0    | ) {34               | 34 + 1   | 49 49          | Хэ          | X 34 + X        | 49 + 49 |                | <br>                    | 49 + 49   | <br>                      | 34          |              |

| /\$7BU\$(7:0  | ) <del>(</del> 187) | 49 + (   | 34 <b>)</b> CC | AB7         | X49 + X         | 34 + CC | <b>8</b> 7     | 49+                     | (34 +) CC | <b>8</b> 7                | 49          | (34 +)       |

| /S5BUS(7:0    | ) [49]              | 49 +     | cc (cc         | X49         | ¥49 +           | cc + cc | 49             | ¥49+                    | (cc +) cc | <b>4</b> 9                | 49          | )<br>(cc + ) |

| /S2BUS(7:0)   | ) *                 | 34 + X E | 37 49          | Xœ          | X 34 + X        | B7 + 49 | X€C            | 34+                     | B7 + 49   | fcc                       | 34          | (B7 + )      |

| /S1BUS(7:0)   | ) <u> </u>          | 0C + X   | 7              | X oc        | Xoc+ X          | F7 + F7 | Xec            | X00+                    | F7 + F7   | foc                       | <b>X</b> 06 | (F7 +)       |

| /S14BUS(7:0)  | ) - <u>(</u> (0)    | F7 + (0  | F4             | <b>X</b> 09 | <b>F7+</b>      | 0C + F4 | 69             | <b>F7+</b>              | 0C + F4   | <b>4</b> 09               | F7          | Xoc + X      |

| /S8BUS(7:0)   |                     | 50 +     | +              | +           | X54 +           | +       | +              | 50+                     | +         | +                         | X44         | +            |

| /S15BUS(7:0)  | 00                  | +        | +              | +           | X42 +           | +       | +              | 56+                     | +         | +                         | 50          | +            |

| /S16BUS(7:0)  | 00                  | +        | +              | +           | X44 +           | +       | +              | X52+                    | +         | +                         | 48          | +            |

| /\$10BUS(7:0) | 00                  | + .      | +              | +           | <b>48</b> +     | +       | +              | X58+                    | . +       | +                         | X52         | +            |

| /S12BUS(7:0)  | 00                  | +        | +              | +           | X50 +           | +       | +              | X54+                    | +         | +                         | 50          | +            |

| /S3BUS(7:0)   | 00                  | +        | +              | +           | +               | +       | +              | X42+                    | +         | +                         | 56          | +            |

| /S68US(7:0)   | 00                  | +        | +              | +           | +               | +       | +              | X44+                    | + •       | +                         | 52          | +            |

| /S0BUS(7:0)   | 00                  | +        | +              | +           | +               | +       | +              | X48+                    | +         | +                         | 58          | +            |

| /N\$72(15:0)  | 0000                | ) +      | +              | +           | +               | +       | +              | +                       | + FD30    | FC40                      | ) +         | FD30         |

| /ING0(7:0)    | <del>{</del> 00     | +        | +              | +           | +               | +       | +              | +                       | + FD      | <b>X</b> 00               | +           | +            |

| /ING1(7:0)    | 2 00                | +        | . +            | +           | +               | +       | +              | +                       | +         | FC                        | X00+        | +            |

| /ING2(7:0)    | 00                  | +        | +              | +           | +               | +       | + .            | +                       | +         | +                         | XF6         | X00 + X      |

| /ING3(7:0)    | 00                  | +        | +              | +           | +               | +       | +              | +                       | +         | +                         | +           | FD +         |

| /CLR          |                     | +        | +              | +           | +               | +       | +              | +                       | +         | +                         | <b>+</b>    | ŧ            |

|               | 0.0                 |          | 130.0          |             | ີ 260.0<br>Time | :(ns)   | 390.0          |                         | 520.0     |                           | 650.0       |              |

FIGURE 4.1a. Timing of theAnalysis Filter (Part 1)

| /CLK          | ٦    | <b></b>       | <b></b>          | <b>—</b> —   | <b>—</b> | <b></b> | <u> </u>           | _           | <b></b>               |             |                 |                        |                         |             |

|---------------|------|---------------|------------------|--------------|----------|---------|--------------------|-------------|-----------------------|-------------|-----------------|------------------------|-------------------------|-------------|

| /CLR2         | ·    | _ <b>+</b> [_ | +                | [+           |          | _t [    | + +                |             |                       | + [         | _] Ł            |                        | _+ [                    |             |

| 702112        |      | +             | +                | +            |          | +       | +                  | +           | +                     | +           | +               | +                      | +                       | _           |

| 284ND_1N(7:0) | X48  | 3 + \(54      | +\6              | 2 58         | X5       | 3+      | +                  | +           | +                     | +           | +               | +                      | +                       |             |

| /S13BUS(7:0)  | F4   | <b>}</b> F7   | F77              | <b>F</b> 4 + | F4       | +XF7    | <b></b>            | <b>F4+</b>  | F4 + F7               | ¥F7         | F4              | $F4 + \sqrt{F7}$       | F7                      | X           |

| /S11BUS(7:0)  | F7   | F4            | Xoe              | 09 +         | F7       | +XF4    | <b>Sec</b>         | 09+         | F7 + F4               | foc         | <b>1</b> 09     | <b>F7</b> + <b>F</b> 4 | ) oc                    |             |

| /S9BUS(7:0)   | 49   | 34            | Хэ               | 49 +         | 49       | + 34    | 84                 | 49+         | 49 + 34               | +34         | 49              | 49 + 34                | 34                      | X           |

| /S7BUS(7:0)   | cc   | 87            | ¥ <del>9</del> . | 34 +         | CC       | +) B7   | 49                 | 34+         | CC + B7               | ¥49         | 34              | CC + 87                | 49                      | X           |

| /S5BUS(7:0)   | сс   | ¥49           | 40               | CC+          | cc       | +49     | 49                 | Хсо         | CC + 49               | 49          | X ce            | CC + 49                | 49                      | X           |

| /S2BUS(7:0)   | 49   | Xcc           | Хз4              | B7 +         | 49       | +Xcc    | 84                 | <b>87</b> + | 49 + CC               | 434         | ₿₹              | ¥49 + XCC              | 34                      |             |

| /S1BUS(7:0)   | F7   | ¥oc           | Xoc_             | F7 +         | F7       | +Xoc    | Aec .              | <b>F</b> 7+ | (F7 +)(0C             | foc         | F7              | F7 + 0C                | )<br>oc                 |             |

| /S14BUS(7:0)  | F4   | X09           | <b>F</b> F7      | (oc+         | F4       | +(09    | F7                 | XOC+        | F4 + 09               | F7          | X0@             | F4 + 09                | <b>F7</b>               | X           |

| /S8BUS(7:0)   | 44   | +             | X <del>5</del> 4 | +            |          | +       | 53                 | +           | +                     | +           | +               | +                      | +                       |             |

| /S15BUS(7:0)  | 50   | +             | X <b>4</b> 6     | ÷            |          | +       | ₹53                | +           | +                     | +           | .+              | +                      | +                       |             |

| /S16BUS(7:0)  | 48   | +             | X <b>4</b> 6     | +            |          | +       |                    | +           | +                     | 53          | +               | +                      | +                       |             |

| /S10BUS(7:0)  | 52   | +             | X <b>4</b> 2     | +            |          | +       | 62                 | +           | +                     | 53          | +               | +                      | +                       |             |

| /S12BUS(7:0)  | 50   | +             | X <b>4</b> 4     | . +          |          | +       | 54                 | +           | + <                   | <b>)</b> 53 | +               | +                      | +                       |             |

| /S3BUS(7:0)   | 56   | +             | X <del>5</del> 0 | +            |          | +       | 48                 | +           | +                     | <b>)</b> 53 | +               | +                      | +                       | <del></del> |

| /S6BUS(7:0)   | 52   | +             | <b>4</b> 8       | +            |          | +       | 46                 | +           | +                     | <b>×</b> 58 | +               | +                      | 53                      |             |

| /S08US(7:0)   | 58   | +             | X <del>9</del> 2 | +            |          | +       | 42                 | . +         | ÷                     | 62          | +               | +                      | 53                      | ·           |

| /N\$72(15:0)  | 3940 | 1026          | EE42             | 2 OA9C       | 50FC     | + 05A   | 2 <b>(</b> FAB)    | A) OOFC     | 506 <del>0</del> FD48 | B FF2       | 4 <b>(</b> FÐ62 | 4596 FC/               | 6 02B                   | 6           |

| /ING0(7:0)    | 39   | ¥00           | +                | +            | 50       | ¥00     | +                  | +           | 50 + 00               | +           | +               | 45 + 00                | +                       | _           |

| /ING1(7:0)    | 00   | 10            | 00               | +            |          | + 05    | X <del>0</del> 0   | +           | + FD                  | X00         | +               | + / FC                 | X00                     |             |

| /ING2(7:0)    | 00   | +             | EE               | X00 + X      | 00       | +       | <b>FA</b>          | X00+        | +                     | FF          | X00+            | X00 +                  | <b>)</b> 02             | Х           |

| /ING3(7:0)    | 00   | +             | +                | OA+          | 00       | +       | +                  | 00          | +                     | +           | ¥ F0            | X00 +                  | +                       | X           |

| /CLR          |      | <del>.</del>  |                  | +            |          | +       | +                  | +           |                       | +           |                 |                        | - <b>t</b> - <u>.</u> - | <u>.</u>    |

|               | 78   | 30.0          |                  | 910.0        | ·        |         | 1040.0<br>Time(ns) |             | 1170.0                |             | 1300.0          | •                      | 1430.0                  |             |

FIGURE 4.1b. Timing of the Analysis Filter (Part 2)

| <i>I</i> CLR  | ' • <u> </u>                                                   | +          | +     | +           | +                | +                | +                | +      | +            | +             | +      | +     | +     | +             | +       | +                  |

|---------------|----------------------------------------------------------------|------------|-------|-------------|------------------|------------------|------------------|--------|--------------|---------------|--------|-------|-------|---------------|---------|--------------------|

| /CLK          | · •                                                            | •          | +     | +           |                  | $\boxed{+}$      | [+]              | •      | F ]          | F             | ٢٦     | 1     | +     | 1 +           | 1+[     | 7+                 |

| ЛNG0(7:0)     | FD                                                             | +          | +     | +           | + X39            | +                | +                | +      | · χ50        | +             |        | +     | +     | <br>+         | +       | +                  |

| лNG*(7:0)     | FC                                                             | +          | +     | +           | + /10            | +                | +                | +      | + \(05       | •             | +      | +     | · )   | (FD+          | +       | +                  |

| ЛNG2(7 0)     | FC                                                             | +          | + .   | +           | • XEE            | +                | +                | +      | + )/FA       | +             | +      | +     | +     | (FF+          | +       | +                  |

| /ING3(7:0)    | 100                                                            | +          | +     | +           | + XFD            | +                | +                | +      | + X0A        | +             | +      | +     |       | (00+          | +       | +                  |

| /X(7:0)       | (∞                                                             | + FD       | + XFC | + ) FC      | +                | + X 39           | + 10             | + X EI | =+ XX0.      | A+            | (50+ X | 05+   | (FA ) | () oe         | X eo    | (+D                |

| 3:28US(7:0)   | 43                                                             | ()<br>)    | X00   | )<br>  0C   | X+9              | <b>C</b> 9       | Xec              |        | ¥49          | - <b>X</b> 29 | +      | +) CC | + 49  | + ) 09        | + 1/200 | +                  |

| 3:08US(7:0)   | <b>€</b> (cc                                                   | <b>₹</b> + | X F2  | <b>X</b> 40 | Xec              | XF4              | X <del>F</del> 7 | ¥+9    | ¥cc          | • F4          | +) F7  | + 49  | + (cc | + ) F4        | + XF7   |                    |

| \$28US(7-0)   | ₹ <b>X</b> cc                                                  | 00         | X F7  | B7          | Xec.             | Yec              | ¥=7              | ¥87    | Ycc          | -Xoc          | + F7   | +) 87 | + Xcc | + 100         | + )(F7  | ÷ X                |

| /\$88US(7:0)  | 43                                                             | F7+        | 00    | 34          | X 49             | ¥7               | Yec              | ¥34    | 49           | + F7          | -) (oc | + 34  | + 49  | + (F7         | + 100   | +                  |

| /\$48US(7:0)  | <b>1</b>                                                       | 87         | 34    | F4          | Х <del>г</del> т | 87               | Xe4              | F4     | )[<br>)[F7   | + 87          | + 34   | +) F4 | + XF7 | + <b>X</b> B7 | + 134   | • X                |

| /\$2BU5(7:0)  | ₹ <b>(</b> F4)                                                 | CG         | (49   | FF7         | χ <del>μ</del>   | ¥ec              | X-49             | ¥F7    | χ <b>F</b> 4 | + CC          | + 49   | +     | + XF4 | + (cc         | + (49   | ÷ X                |

| /\$1BU5(7:0)  | (F4)                                                           | (34        | (49)  | 39          | ¥#4              | 84               | X-49             | 109    | ¥F4          | + 34          | + 49   | + 09  | + XF4 | + 34          | + 149   | $\overline{+\chi}$ |

| 5148US(7:0)   | (F7)                                                           | (49+       | (34)  |             | (F7              | 49               | X <del>6</del> 4 | ) oc   | ¥F7          | + 49          | + 34   | +) 00 | + (F7 | + 49          | + 1 34  | $\overline{\cdot}$ |

| /\$78U\$(7:0) | <b>{</b> 00                                                    | +          | . +   | +           | +                | XFD              | +                | +      | +            | +X0A          | +      | +     | +     | + X00         | +       | +                  |

| 515BUS(7:0)   | <del>{</del> 00                                                | +          | +     | +           | +                | XFC              | +                | +      | +            | •XEE          | +      | +     | +     | + XFA         | +       | +                  |

| 5:6BUS(7:0)   | <del>(</del> 00                                                | +          | +     | +           | +                | χ <del>f</del> c | +                | +      | +            | + 10          | +      | +     | •     | + (05         | +       | +                  |

| /S98US(7:0)   | <b>4</b> 00                                                    | · +        | +     | +           | +                | (FD              | +                | +      | +            | +) 39         | +      | +     | +     | + \(50)       | +       | +                  |

| 511BUS(7:0)   | <b>{</b> 00                                                    | +          | +     | +           | +                | +                | +                | +      | +            | +XFD          | +      | +     | +     | + X0A         | +       | +                  |

| /S35US(7·0)   | <b>4</b> 00                                                    | +          | +     | +           | +                | +                | +                | +      | +            | +XFC          | +      | +     | +     | + XEE         | +       | +                  |

| S55US(7 C)    | <del>,</del> 00                                                | + .        | +     | +           | +                | +                | +                | +      | +            | →<br>XFC      | +      | +     | +     | + /10         | +       | +                  |

| S08US(7:0)    | <del>1</del><br><del>1</del><br><del>1</del><br><del>2</del> 0 | +          | +     | +           | +                | +                | +                | +      | +            | •XFD          | +      | +     | +     | + \(39)       | +       | +                  |

| /sdout(15:0)  | 2 2000                                                         | ) +        | +     | •           | +                | +                | +                | +      | +            | +             | +      | +     | +     | +             | +       | +                  |

| R_OUT(7:0)    | {}                                                             | +          | +     | +           | +                | +                | •                | +      | +            | +             | +      | +     | +     | •             | +       | +                  |

| ٥             | .0                                                             |            | 95.0  | 1(          | 90.0             | 2                | 85 0             |        | 0.0          |               | 475.0  |       | 570 0 | 6             | 65.0    |                    |

|               |                                                                |            |       |             |                  |                  | Time(ns          | 9      |              |               |        |       |       |               |         |                    |

## FIGURE 4.2a. Timing of the Synthesis Filter (Part 1)

| /CLR        | •      | +                 | +                                             | +             | +           | •          | •                                             | . +                                            | +         | •                     | •         | •         | +              | +           | +                     | +          |

|-------------|--------|-------------------|-----------------------------------------------|---------------|-------------|------------|-----------------------------------------------|------------------------------------------------|-----------|-----------------------|-----------|-----------|----------------|-------------|-----------------------|------------|

| /CLK        | 1.     |                   | <u>⊡•</u>                                     | <u> </u>      | <u> </u>    |            |                                               |                                                |           |                       | •         | <u>ار</u> | F ]            | F           | <u>ل</u> ا            |            |

| /ING0(7.0)  | 50+    | ×45               | +                                             | +             | +           |            |                                               |                                                | <br>      | <br>+ χ <sub>52</sub> |           |           |                | γ           | L<br>                 |            |

| /ING1(7:0)  | FD+    |                   | +                                             | +             | +           |            | +                                             | +                                              | •         | /<br>+ \              | •         | +         | +              | <u>^</u>    | +                     | •          |

| /ING2(7:0)  | FF+    | <br>              | +                                             | +             | +           | /FC        | +                                             | +                                              | +         | \<br>+ \/FF           |           | •         | +              |             | 0 +                   | +          |

| /ING3(7:0)  | 00+    | <br>Дяо           | +                                             | +             | +           | /          | +                                             | +                                              | +         | <u>``</u>             | +         | +         | +              |             | 0 +                   |            |

| /X(7:0)     | - X-FF | = )((FD           | 45                                            | FC            | -1-         | 2 - XFE    | · + ¥5                                        |                                                |           |                       |           |           |                |             | io + )                | (53+       |

| 128US(7:0)  | CO     | X49 +             | X 29 +                                        | Yoc+          | Xco         | /*/*/      | A                                             | <u> </u>                                       | <u>/</u>  | /X\<br>Y43            |           | Yoc       |                | -149        | +) 09                 | •          |

| 10BUS(7:0)  | 49+    | Xcc +             | X F4 +                                        | )<br>(F7+     | X 49+       | Yco        | _л<br>Х F4                                    | _/L                                            | <br>      | <br>Xec               | <br>}     | <br>      | <br>           |             |                       |            |

| 58BUS(7.0)  | B7+    | Xcc +             | X0C+                                          | XF7+          | Х в7+       | <br>Усе    | <br>¥₀€                                       | <br>                                           | <br>      | Yec                   | _A        | _A        |                |             | -X oc                 |            |

| 56BUS(7:0)  | 34+    | X49 +             | X F7 +                                        | Yoc+          | 34+         | ¥49+       | _л<br>У г <del>7</del>                        | <u>_л.                                    </u> | <br>      | <br>                  | <br>      | Yoc       | _/ <u></u><br> |             | -)(F7                 | - <b>x</b> |