# FOR REFERENCE

POT UZE LAKEN FROM THIS ROOM

I40 Mb/s DEQPSK MODEM

IF STAGE

bу

M. Akif Suyabatmaz

B.S. in EE., Boğaziçi University, 1982

Submitted to Institude for Graduate Studies in

Science and Engineering in partial fullfillment of the

requirements for the degree of

Master of Science

'n

Electrical Engineering

Boğaziçi University

1985

#### ACKNOWLEDGEMENTS

I wish to acknowledge my indebteness to the project manager, Mr. Ali Beygu, for his drive and enthusiasm, to Y. Doc.Dr. Ömer Cerid, who consulted and helped me during and before the preparation of this thesis.

I must especially thank to Mr. Hüseyin Kalman, for his endless patience, and to all staff of Scientific and Technical Research Council of Turkey who provided me the proper working conditions for the completion of this thesis.

I also wish to express my deep appreciation to my parents for their consent, support and patience not only for the completion of this thesis, but all through my life.

#### **ABSTRACT**

Recently, as the digital technology progresses, the exploding capacity of digital information nececities fast digital communication systems. Since the congestion prevailing in many regions of radio frequency spectrum has created the need for improved spectrum utilization techniques, the demand for multilevel (M-ary) digital modulation techniques has also increased.

In this thesis, a differentially encoded and differentially decoded quadrature phase shift keyed modem, employing coherent demodulator, was briefly analyzed. System building blocks were investigated and the one, proper to high data rate application, was chosen for system realization.

A working circuit was build as an intermediate frequency (IF) stage, operating at 140 Mbit per second, and realized.

# ÖZETCE

Günümüzde sayısal bilgi iletim sistemine olan ihtiyaç, sayısal verilerin artımına paralel olarak hızla artmaktadır. Veri kapasitesindeki büyüklük hızlı sayısal iletimi gerektirmekte, hızlı sayısal iletim ise güç tasarrufu yapan sayısal modulasyon biçimleri yerine, band tasarrufu yapan çok seviyeli

sayısal modulasyon biçimlerini gerekli kılmaktadır.

Bu tezde farksal kodlayıcı ve farksal kod çözücü birimlerini içeren, eşzamanlı demodulasyon prensibini uygulamaya koyan, dört seviyeli faz kodla-malı (QPSK) modulasyon biçimi kısaca analiz edilmiştir. Sistemi oluşturan birimlerin çeşitli işleme yordamları incelenmiş, hızlı iletim sistemine uygun olanı uygulamaya konalarak 140 Mbit/s veri hızı ile çalışan bir sistem ara-frekans katı olarak gerçekleştirilmiştir.

#### TABLE OF CONTENTS

Acknowledgement

Abstract

Özetce

Table of contents

Table of symbols

Chapter 1: Introduction

Chapter 2: DEQPSK Theory

#### A- Structure

- Serial-to- parallel converter (S/P)

and parallel -to- serial converter (P/S)

- 2. Gray coded differential encoder and decoder

- 3. Multiplier, 90° phase shift network, IF amplifier, power summer and spilitter networks.

- 4. Carrier recovery (CR)

- 5. Symbol timing recovery (STR)

- 6. Demodulator

- B Spectrum and spectral (bandwidth) efficiency

- C Error performance

Chapter 3: Hardware and hardware description of the system

- 1. Serial -to- parallel converter (S/P)

- 2. Parallel -to- serial converter (P/S)

- 3. Gray coded differential encoder and decoder

- 4. Modulator and summer

- 5. IF amplifier

- 6. Demodulator input stage

- 7. Symbol timing recovery (STR)

- 8. Carrier recovery (C.R.)

Chapter 4: Evaluation and Conclusion

References

Appandices: A - 1: Bandpass signals

$\Lambda$  - 2 : Bandpass stationary stochastic process representation

$\Lambda$  - 3 : M-ary PSK signal representation interms of equivalent low-pass form.

$\Lambda$  - 4 : Spectral characteristics of digitally modulated signals.

B - 1: PLL, Brief theory

B - 2: Wide-band phase spilitting networks.

B - 3: Resistive summer and spilitter networks.

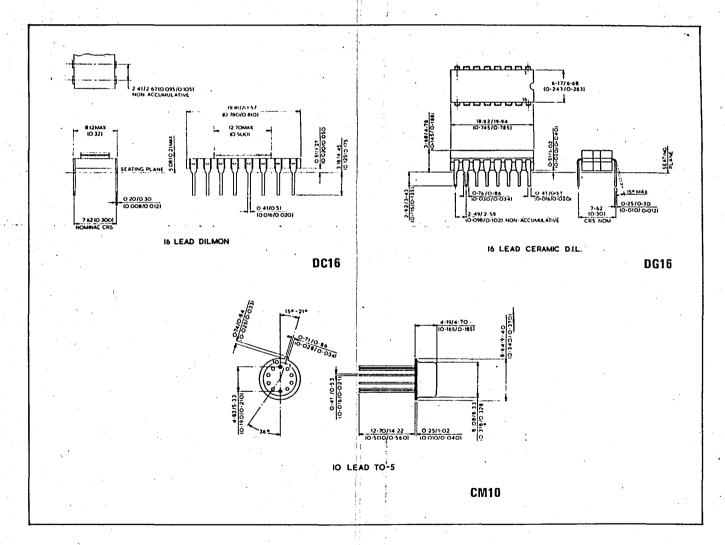

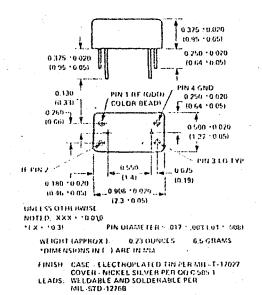

# IC specifications:

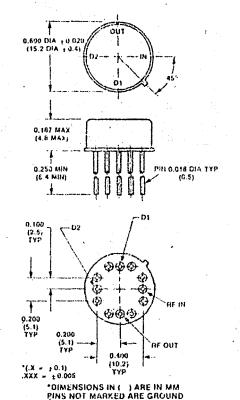

MHF-3P: Double balanced mixer

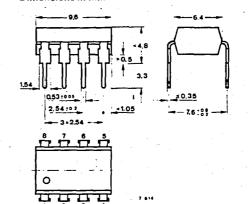

PM 101 : Biphase modulator

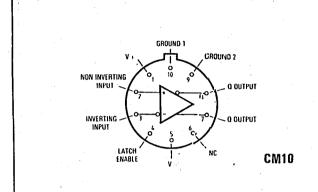

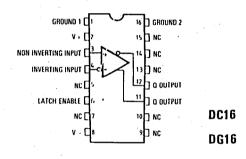

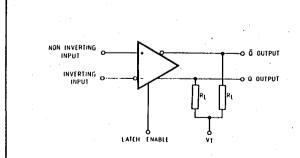

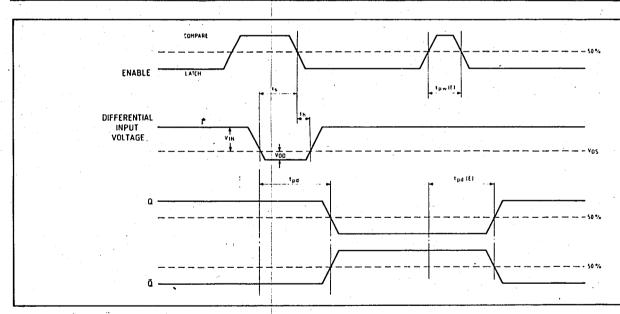

SP 9685: Fast comparator and latch

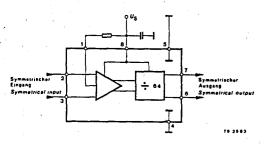

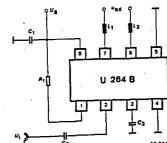

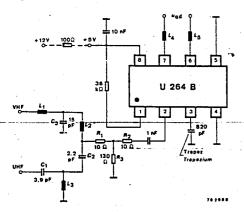

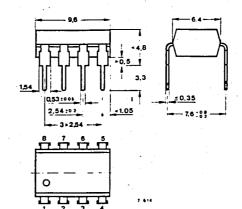

U 264 : 1 GHz, divide by 64, prescaler

#### TABLE OF SYMBOLS

- (an) : Random binary sequence, serial input data stream into the modulator.

- $\{\widehat{a}_n\}$  : Reconstructed random binary sequence, scrial output of the demodulator.

- $r_b$ : Rate of the random binary sequence,  $\{a_n\}$   $r_b=1/T_b$  (bit/sec.)

- $\widehat{r}_b$  : Reconstructed rate of the random binary sequence,  $\left\{\widehat{a}_n\right\}$  .  $\widehat{r}_b$  =1/Tb (bit/sec.)

- -CLs -: Clock signal having rate  $r_b(\text{or } \hat{r}_b)$ .

- $\{I_n\} \stackrel{\triangle}{=} \{I_{1n}I_{0n}\}$ : 4-level symbol sequence, output of the serial to parallel converte

- $\{\hat{\mathbf{I}}_n\} \stackrel{\Delta}{=} \{\hat{\mathbf{I}}_{\text{in}}\hat{\mathbf{I}}_{\text{on}}\}$ : Reconstructed 4-level symbol sequence, parallel data steram into the parallel to serial converter.

- $r_s$ : rate of the symbol sequence,  $\{I_n\}$ .  $r_s = 1/T_s$  (dibits/sec.).

- $\hat{r}_s$ : Reconstructed rate of the symbol sequence,  $\{\hat{l}_n\}$ .  $\hat{r}_s$  = 1/T<sub>s</sub>(dibits/sec).

- CL<sub>p</sub>: Clock signal having rate r<sub>s</sub> (or r<sub>s</sub>).

- $\{E_n\} \stackrel{\Delta}{=} \{E_{1n}E_{0n}\}$ : 4-level symbol sequence, output of the gray coded differential encoder circuit.

- $\{\mathring{R}_n\} \stackrel{\Delta}{=} \{\mathring{R}_{1n}\mathring{R}_{on}\}$ : 4 level symbol sequence; clocked symbol sequence,  $\{\mathring{R}_n\}$ .

- $\{P_n\} \stackrel{\Delta}{=} \{R_{n-1}\}$  : 4 level symbol sequence; single symbol time  $(T_s)$  delayed version of the sequence,  $\{R_n\}$ .

### I. INTRODUCTION

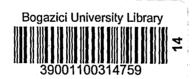

Quadriphase modems, having theoretical 2 bits/sec/Nz spectral efficiency are used in system application were 1 b/s Nz theoretical spectral efficiency of binary phase shift keyed (BPSK) systems are not sufficient, for a given bandwidth. However, the price paid for using such a bandwidth efficient system, is to increase the signal to noise ratio (SNR) for a given probability of error, and increased circuit copmlexity. Figure -1, being the general structure of a quadriphase modem, can be used to obtain the block diagrams of various quadriphase modulation schemes by apropriately deleting some modules. The most known types of quadriphase modems can be listed as:

Quadrature phase shift keyed (QPSK) modem: QPSK modem is the minumum structure quadriphase modem. Its block diagram is obtained by deleting the differential encoder and quadrature (Q) arm delay element in the modulator; and the differential decoder and inphase (I) arm delay element in the modulator, of figure-1. However, this modem suffers from phase ambiguity at the receiver, and, when the modulator output is filtered, the modulated signal has large time domain amplitude fluctuations (theoretically infinite dB) as the phases of the I am Q arms change simultaneously.

Offset keyed QPSK (OKQPSK) modem: Deleting the differential encoder

and decoder pair of figure-1, we obtain the OKQPSK modem block diagram. Off-seting one arm with respect to the other by an amount equal to incoming serial bit duration ,Tb, is used to solve the dramatic envelope variation of the filtered QPSK modulated signal. The phase transitions at the I and Q arms of the filtered OKQPSK modulated signal are not instantaneous as in filtered QPSK modulated signal. However the phase transitions can not occur simultaneously ,so, only one channel envelope amplitude can be momentarily zero at a time, limiting the envelope variation of the filtered QKQPSK modulated signal to atmost 3 dB.

Differential QPSK (DQPSK) and Differentially encoded QPSK (DEQPSK) modems:

The DEQPSK is a coherent detection scheme while DQPSK in not. The former is

totally a different story and is skipped. |1,2,3|. DEQPSK modem structure is

obtained by deleting the offset delay elements only, and differential encoder

decoder pair is left to solve the phase ambiguity problem of the QPSK modem, at

the cost of (3dB) error performance.

Differentially encoded, offset keyed QPSK (DEOKQPSK) modem: DEOKQPSK modem has the most complete structure, with the block diagram shown in figure-1, and solves the two problems of the Q'SK modem. Infact, the differential encoder-decoder pair happenes to be simpler than DEQPSK's one |2|

We have started the DEQPSK modem realization as a first step ,so, the following chapters will deal with this structure only. However some topics of chapter-2 will deal with QPSK signal, rather than DEQPSK signal, to get some reasonable results concerning the operations of the related blocks. To clarify the reason, suppose that, the sequence of information symbols,  $\{I_n\}$ , is wide sense stationary (wss) and information symbols are mutually uncorrelated. If this sequence is applied to a differential encoder, the output sequence,  $\{E_n\}$ ,

system has a first order memory. When the above properties of the differential encoder do not let the problem to yield a simple result, the differential encoder-decoder pair is assumed not exit in the overall system.

In chapter-2 we have explained the operations and internal organizations of the blocks appearing in the system structure; and chapter-3, deals with the realizations and respective problems of those blocks. Appendix-A is prepared in order to get familiar with the analytical structure of the DEQPSK modem and band pass signals in additive white Gaussian noise (AWGN), while appendix-B is organized to clarify the operations of basic system elements and to give design the hints.

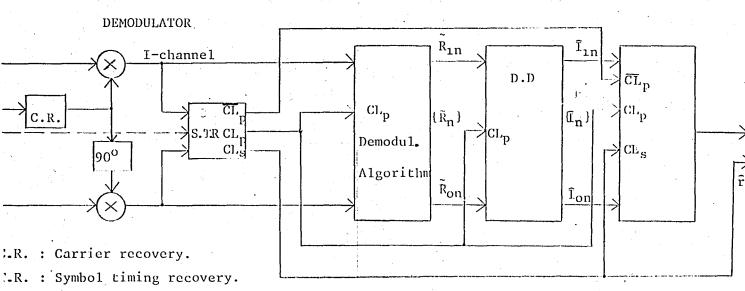

Figure - 1 : General block diagram of a quadriphase modem.

rb : Serial symbol timing

# II. DEQPSK THEORY

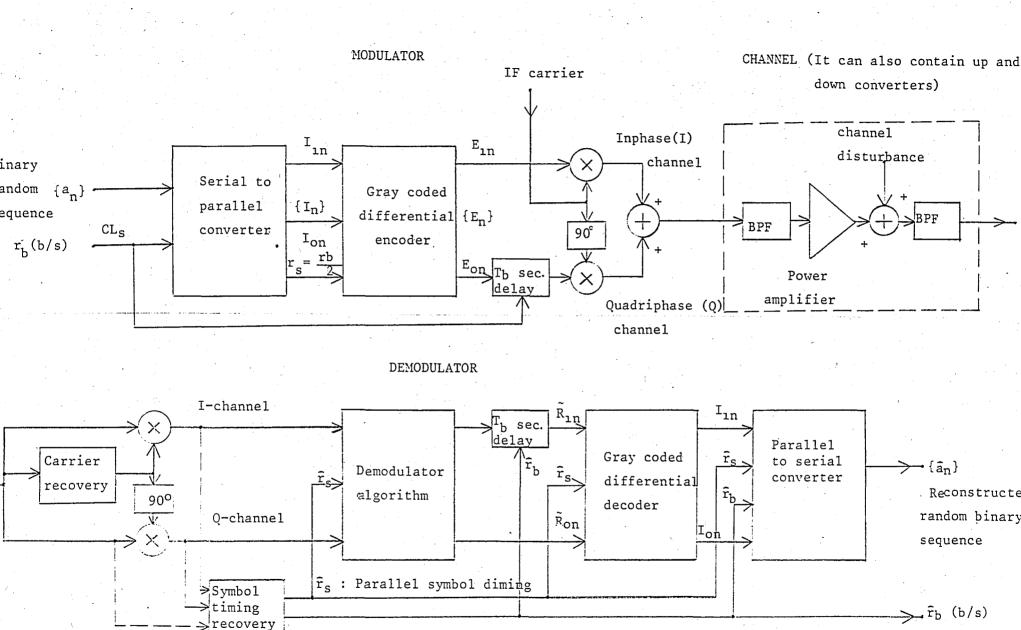

In this chapter we will review the block of the DEQPSK modem in more detail, then, DEOPSK spectrum and finally its performance.

S/P : Serial to parallel converter

D.E.: Differential encoder

'/S : Parallel to serial converter

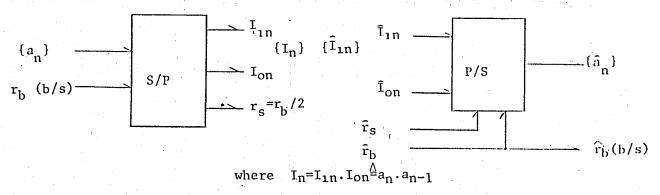

Figure - 2 : DEQPSK modem block diagram.

2-A.1 Serial to parallel converter (s/p) and parallel to serial converter (p/s).

Figure -3 : S/p data flow diagrams.

The binary digits (bits),  $\{a_n\}$ , from the random binary sequence generator, having the bit rate rb, are mapped uniquely into four dibits (composed of two adjacent pairs of bits) to form information symbols  $\{I_n\}$ , having symbol rate,  $r_s = r_b/2$ . The parallel to serial converter is just the reverse of that operation and both circuits have been explained in chapter-3.

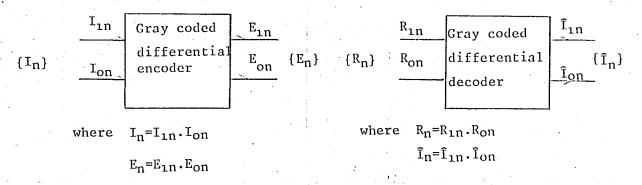

# 2-A.2 Gray Caded differential encoder and decoder.

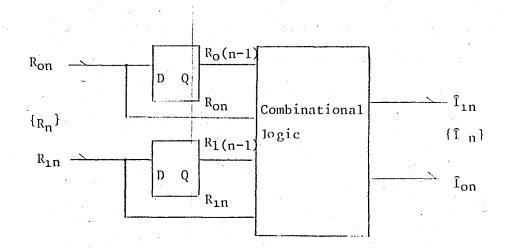

Figure-4: Gray coded differential encoder and decoder data flow diagrams.

When the absolute phase of the modulator is transmitted as the source information, carrier recovery circuit (such as quadrupter) usually can not extract the correct reference phase, causing phase ambiguity at the demodulator. To overcome this problem differential encoder reassignes the phase transitions as the source information. Denoting four input symbols and four output symbols as

$$I_{n0} = \overline{I}_{1n} \cdot \overline{I}_{0n} = 00$$

$$I_{n2} = I_{1n} \cdot \overline{I}_{0n} = 10$$

$$I_{n3} = I_{1n} \cdot I_{0n} = 11$$

$$E_{n0} = \overline{E}_{1n} \cdot \overline{E}_{0n}$$

$$E_{n2} = E_{1n} \cdot \overline{E}_{0n}$$

$$E_{n3} = E_{1n} \cdot E_{0n}$$

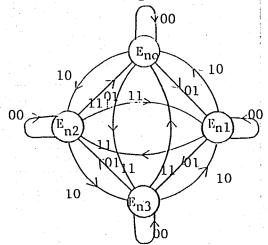

and using the gray coding property (adjacent symbols differ in only one bit) for the output sequence,  $\{E_n\}$ , we get the assignment rule for the gray coded differential encoder as follows\*

- If input symbol is 00, then make no phase jump, transmit the same phase,

- If input symbol is 01, then make a 90° phase jump,

- If input symbol is 11, then make a 180° phase jump,

- If input symbol is 10, then make a 270° phase jump

<sup>\*</sup> This assignment rule is not unique. Since there are four different input symbols,  $I_n$ , there are also  $\frac{4!}{(4-4)!}$  = 24 different assignment rules.

Hence the state diagram and state table is given as

| Symbol | Description |    |    |            |  |

|--------|-------------|----|----|------------|--|

| 0      | 0           | to | 1  | transition |  |

| α      | 0           | to | 1  | transition |  |

| β      | 1           | to | 0  | transition |  |

| 1 .    | 1           | to | 1. | transition |  |

|        |             |    |    |            |  |

|       |                 | <del></del> |                                 |                                 |       |                    |  |

|-------|-----------------|-------------|---------------------------------|---------------------------------|-------|--------------------|--|

| Input |                 | put         | Present<br>state                | state Next state                |       | Short cut method   |  |

|       | I <sub>in</sub> | Ion         | E <sub>1n</sub> E <sub>on</sub> | E <sub>in</sub> E <sub>on</sub> |       |                    |  |

|       | 0               | 0           | 0 0                             | 0 0                             | .0 0  |                    |  |

|       | 0               | 0           | 0 1                             | 0 1                             | 0 1   |                    |  |

|       | 0               | 0           | 1 0                             | 1 0                             | 1 0   | No change          |  |

| _     | 0               | 0           | 1 1                             | 1 1                             | 1 1   |                    |  |

|       | 0               | 1.          | 0 0                             | 0 1                             | 0 α   |                    |  |

|       | 0               | 1           | 0 1                             | 1 1                             | α 1   | Count by 1 in gray |  |

|       | 0               | 1           | 1 0                             | 0 0                             | β 0   | sequence           |  |

|       | 0               | 1           | 1 1                             | 1 0                             | . 1 β |                    |  |

|       | 1               | 0           | 0 0                             | 1 0                             | α 0   |                    |  |

|       | 1               | 0           | 0 1                             | 0 0                             | 0 β   | Count by 3 in gray |  |

|       | 1               | 0           | 1 0                             | 1 1                             | 1 α   | sequence           |  |

| _     | 1               | 0           | 1 1                             | 0 1                             | β 1   |                    |  |

|       | 1               | 1           | 0 0                             | 1 1                             | αα    |                    |  |

|       | 1               | 1           | 0 1                             | 1 0                             | αβ    | Count by 2 in gray |  |

|       | 1               | 1           | 1 0                             | 0 1                             | βα    | sequence           |  |

| _     | 1               | 1           | 1 1                             | 0 0                             | ββ    |                    |  |

|                | E <sub>in</sub> E <sub>on</sub> |    |    |    |    |  |  |  |

|----------------|---------------------------------|----|----|----|----|--|--|--|

|                | Eın                             | 00 | 01 | 11 | 10 |  |  |  |

| I <sub>n</sub> | on  <br>00                      | 0  | 0  | 1  | 1  |  |  |  |

|                | 01                              | 0  | α  | 1  | β  |  |  |  |

|                | 11                              | α  | α  | ß  | ß  |  |  |  |

|                | 10                              | α  | 0  | β  | 1  |  |  |  |

|                                       | in"on |    |    |      |

|---------------------------------------|-------|----|----|------|

| Eon                                   | 00    | 01 | 11 | 10 . |

| 1 <sub>11</sub> 1 <sub>01</sub> 00 01 | 0     | 1  | 1. | 0    |

| and the second second                 | α     | 1  | β  | 0    |

| 11                                    | α     | β  | ß  | α    |

| 10                                    | 0     | ß  | 1  | α    |

Flip-flop excitation table

| Behavior                                 | D | J | K |

|------------------------------------------|---|---|---|

| 0                                        | 0 | 0 | Х |

| α                                        | 1 | 1 | X |

| β                                        | 0 | х | 1 |

| t la | 1 | х | 0 |

| x                                        | X | х | X |

The J-K flip-flop realization yields (we drop the subcript 'n' for simplicity)

$$J_{EO} = I_o \cdot \overline{E}_1 + I_1$$

$J_{E1} = I_1 \cdot \overline{E}_o + I_o \cdot E_o$

$K_{EO} = I_1 \cdot \overline{E}_1 + I_o E_1$

$K_{E1} = I_1 \cdot \overline{E}_o + I_o \cdot \overline{E}_o$

D flip-flop realization yields

$$\mathbf{D}_{\mathrm{EO}} = \mathbf{I}_{\mathrm{o}} \cdot \overline{\mathbf{E}}_{1} \cdot \overline{\mathbf{E}}_{\mathrm{o}} + \overline{\mathbf{I}}_{\mathrm{o}} \cdot \mathbf{E}_{1} \cdot \mathbf{E}_{\mathrm{o}} + \mathbf{I}_{1} \cdot \mathbf{E}_{1} \cdot \overline{\mathbf{E}}_{\mathrm{o}} + \overline{\mathbf{I}}_{1} \cdot \overline{\mathbf{E}}_{1} \cdot \mathbf{E}_{\mathrm{o}}$$

$$D_{E1} = I_o.\overline{E}_1.E_o + \overline{I}_o.E_1.\overline{E}_o + I_1.\overline{E}_1.\overline{E}_o + \overline{I}_1.E_1.\overline{E}_o$$

The differential encoder does just the reverse operation. But if we assume that present received information symbol,  $R_n = \{R_{1n}, R_{0n}\}$ , and the previous one,  $R_{n-1} = \{R_{1(n-1)}, R_{0(n-1)}\}$ , are available at the input of the decoder, it is no more a sequential but a combinational logic. So with the help of gray coded differential encoding rules, we get the gray coded differential decoding rules as follows

- If the previous symbol and the present symbol are equal, then assign 00 to the output pair,

- If the previous symbol and the present symbol make a gray count by 1, then assign of to the oupput pair,

- If the previous symbol and the present symbol make a gray count by 2, then assign 11 to the output pair,

- If the previous symbol and the present symbol make a gray count by 3, then assign 10 to the output pair.

Dropping the subscript n, and defining the previous symbol and received symbol as  $R_{n-1} \stackrel{\Delta}{=} P$ ,  $R_n = R$ ; we get the truth table and output expression given as

| Îon      | P <sub>1</sub> P <sub>o</sub> |   |    | 11  |

|----------|-------------------------------|---|----|-----|

| $R_1R_0$ | 0                             | 0 | 1  | 1   |

|          | 1                             | 0 | .0 | 1 · |

|          | 1                             | 1 | 0  | 0   |

| •        | 0                             | 1 | 1  | 0   |

| Î.on     | $P_1P_0$ | ·. |   |   |

|----------|----------|----|---|---|

| $R_1R_0$ | 0        | 1  | 1 | 0 |

|          | 0        | 0  | 1 | 1 |

|          | 1        | 0  | 0 | 1 |

|          | 1        | 1  | 0 | 0 |

| Preser | nt symbol         | Previou             | s symbol     | output          | symbol |

|--------|-------------------|---------------------|--------------|-----------------|--------|

| Rln    | R <sub>on</sub> * | R <sub>1(n-1)</sub> | $R_{o(n-1)}$ | Î <sub>ln</sub> | Îon    |

| 0      | 0                 | 0                   | 0            | 0               | 0      |

| 0      | 0                 | 0                   | 1            | 1               | 0      |

| 0      | 0                 | .1                  | 0            | 0               | 1      |

| 0      | 0                 | 1                   | 1            | 1               | 1      |

| 0      | 1                 | 0                   | 0            | 0               | 1      |

| 0      | 1                 | 0                   | 1            | 0               | 0      |

| 0      | 1                 | 1                   | 0 ;          | 1               | 1      |

| 0      | 1                 | 1                   |              | 1               | 0      |

| 1      | 0                 | 0                   | 0            | 1               | 0      |

| 1.     | 0                 | 0                   | · (1. )      | 1.              | 1      |

| 1      | 0                 | 1                   | 0 (          | 0               | 0      |

| 1      | 0                 | 1                   | 1            | 0               | 1      |

| 1      | 1                 | 0                   | 0            | 1               | 1      |

| 1      | 1                 | 0                   | 1            | 0               | 1      |

| 1      | 1                 | 1                   | 0            | 1               | 0      |

| 1      | . 1               | 1                   | 1            | 0               | 0      |

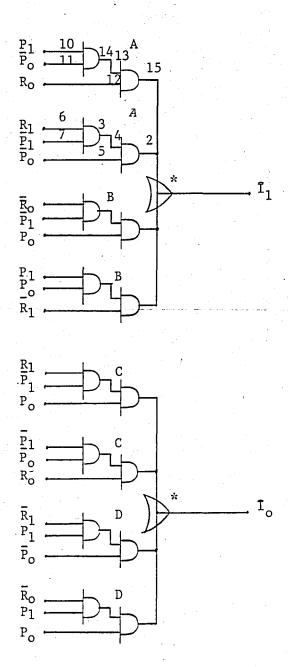

$$\widehat{\mathbf{I}}_{on} = \mathbf{R}_{o} \overline{\mathbf{P}}_{1} \overline{\mathbf{P}}_{o} + \overline{\mathbf{R}}_{o} \mathbf{P}_{1} \mathbf{P}_{o} + \mathbf{R}_{1} \overline{\mathbf{P}}_{1} \mathbf{P}_{o} + \overline{\mathbf{R}}_{1} \mathbf{P}_{1} \overline{\mathbf{P}}_{o}$$

$$\bar{\mathbf{I}}_{1n} = \mathbf{R}_{o} \mathbf{P}_{1} \overline{\mathbf{P}}_{o} + \overline{\mathbf{R}}_{o} \overline{\mathbf{P}}_{1} \mathbf{P}_{o} + \mathbf{R}_{1} \overline{\mathbf{P}}_{1} \overline{\mathbf{P}}_{o} + \overline{\mathbf{R}}_{1} \mathbf{P}_{1} \mathbf{P}_{o}$$

It is certain that in the case of noise free environment  $\{\hat{I}_n\}$  should equal to  $\{I_n\}$ , and this is checked analytically.

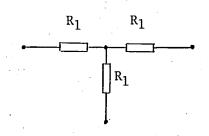

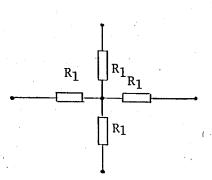

2 - A.3. Multiplier, 90° phase shift circuit, IF amplifier, power summer and spilitter networks.

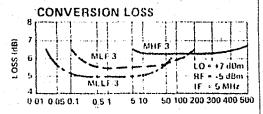

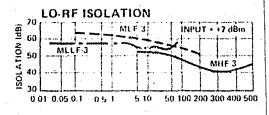

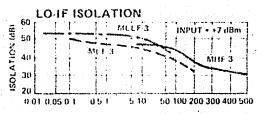

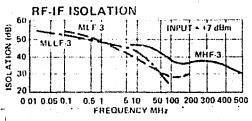

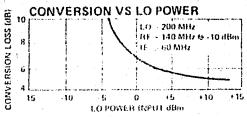

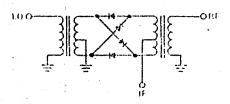

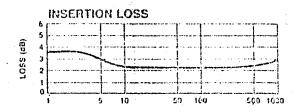

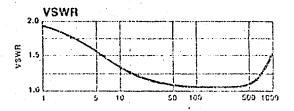

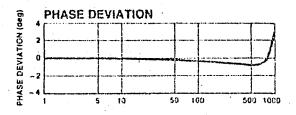

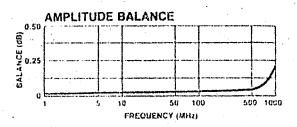

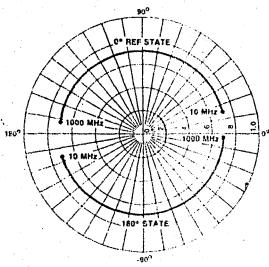

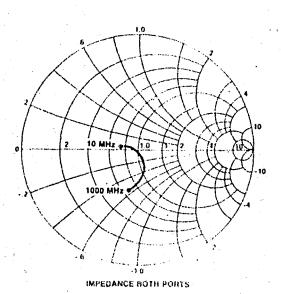

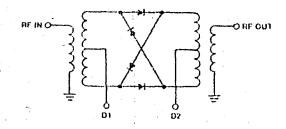

MHz) at the IF frequency (140 MHz) with as little as possible PM-AM conversion. The balanced mixer has extremely wide bandwidth compared with monolithic integrated circuit multipliers, however, due to unbalance, it may have pure isolation amoung its ports. With proper choise of signal levels, the mixer feedthrough and highorder intermodulation products are minimized. The biphase modulator used at the modulator side, is nothing but a balanced mixer except for improved amplitude and phase match between the two states. (For technical data refer to I.C. specifications section.)

This modem is designed to be an IF stage, so, in the operating system modulator and demodulator are connected with an IF amplifier only, there is no RF stage in between them. The amplifier is left to Chapter-3, and the rest of this section can be found from the related appendices.

It is certain that the heart of the coherent demodulator is the carrier synchronization and this subject has been extensively analyzed in the literature. To proceed with the investigation of various CR schemes, the target value of rms phase jitter (var  $\sqrt{\phi}$ ) or the tolerated circuit complexity has to be known priori. The rms phase jitter depends severely on the bandwidth efficiency of the modulation scheme, and can be found either graphically ( $P_e$  versus rms phase jitter), or analytically from the previous works. The types of carrier recovery schemes can be listed as follows.

- Maximum a posteriori probability (MAP) and maximum likelihood (ML) estimators of carrier phase. |2,17|

- 2. Costas loop of carrier phase recovery |1,2,15,16|

- 3. Demod-remod carried phase recovery. |2,18,19|

- 4. Joint recovery of carrier phase and symbol timing recovery. |2|

- 5. nth order power law carrier phase recovery [1,2]

- 6. Decision feedback PLL. |1|.

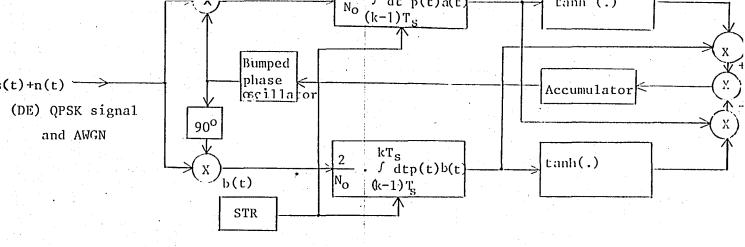

Maximum likelihood estimator is employed when the estimated parameter (carrier phase) is unknown but not random. However, if estimated parameter is a random variable MAP estimator comes into use, and in this case when the random parameter (carrier phase) has a uniform distribution, ML and MAP estimators are equivalent. |2|. In the MAP estimator strategy the observation of the incoming PSK signal, s(t), corrupted by additive channel noise, n(t) (narrowband bandpass process), on the interval  $[0,T_S]$  with the pre-knowledge of signal pulse shape (p(t)), carrier frequency and precise symbol timing, are

used to estimate the carrier phase, 0(t)=0 (assumed constant in the interral  $[0,T_s]$ ), which maximizes the conditional probability p(0(t)|s(t)+n(t)). (Figure-5). However it leads to closed loop implementation with active arm filters, mached to the signal pulse shape, p(t), and requires the symbol synchronization pulses to drive the matched filter, all of which make this strategy difficult to implement.

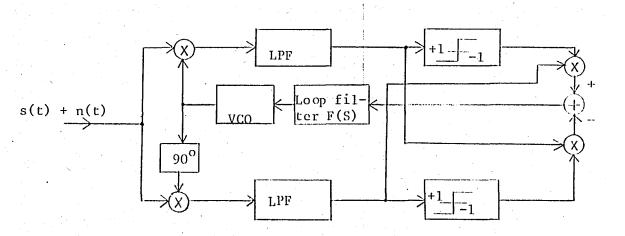

When the active arm filters are replaced by passive low pass filters, accumulator by analog loop filter, bumped phase oscillator by voltage controlled oscillator (VCO) and hyperbolic tangent (tanh) nonlinearity by

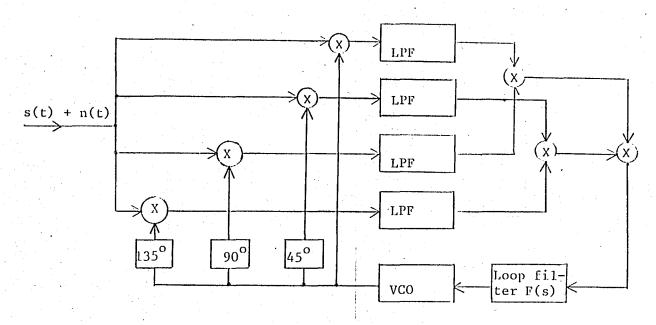

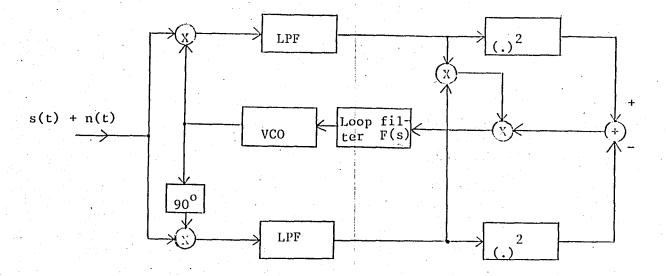

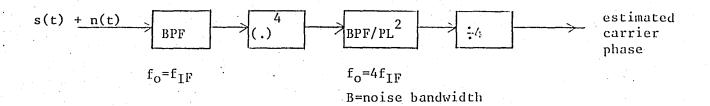

then, one obtains the conventional Costas loop and polarity type Costas loop respectively. |17|. (Figures-7.8) In this case, for a given rate and SNR one can find the optimum filter bandwidth in the sense of minimizing the square rms phase jitter, even, when the symbol synchronization is known, an integrate and dump filter placed on the arms, can still improve the carrier to noise ratio about 4-6 dB depending on data rate. |15| On the otherhand conventional quadriphase Costas loop (Figure -6) and small SNR practical realization of MAP estimator loop (figure -11) are equivalent stochastically. |17| So we conclude that conventional quadriphase Costas loop and its previously shown equivalent |17|, the fourth power loop (figure-9), are low SNR practical realizations of the MAP estimate loop, for QPSK.

The demod-remod tracking loop, joint recovery of carrier phase and

signal timing, and decision feedback PLL are left to references listed previously.

The fourt power loop, when excited by QPSK signal, has the phase error variance (square phase jitter) of |2|:

$$Var\phi = B.T_{s} \cdot \left[ 0.1125 + 1.4625 \frac{1}{\chi_{b}} + 24.469 \frac{1}{\chi_{b}^{2}} + 21094 \frac{1}{\chi_{b}^{3}} + 2.531 \frac{1}{\chi_{b}^{4}} \right]$$

B = nosie equivalent bandwidth of the bandpass filter (or PLL) located at 4 time IF carrier frequency ( $f_{IF}$ ): (in IIz)

$T_s = symbol duration$

${\rm N}_{\rm O}$  = double sided noise spectral density at the input of the CR loop.

$$\delta_b = \frac{A^2 T_s}{2N_o}$$

= QPSK signal, SNR : (see Chapter -2.B.)

Where it is assumed that Nyquist base band pulse shaping is used, p(t) = A sinc  $(t/T_s)$ , and  $B \ll \frac{1}{T_s}$ . Clearly the steady state rms phase jitter can be made as small as possible, by reducing the loop bandwidth, almost independently from the SNR. However small bandwidth means; inability to track instabilities in the transmitted carrier, prolonged acquisition time for phase recovery, and in the case of passive band pass filter, unsymetry of band pass filter due to mistuning, which degrades the performance of the CR circuit.

Fig -5: MAP estimation loop for carrier phase (QPSK)

Fig-6 : Conventional quadriphase Costas loop (QPSK)

Fig -7; Large SNR practical realization of MAP estimator loop with passive arm filters (QPSK)

Fig - 8 : Small SNR practical realization of MAP estimator loop with passive arm filters (QPSK)

Fig - 9 : Fourth power law carrier phase recovery (QPSK)

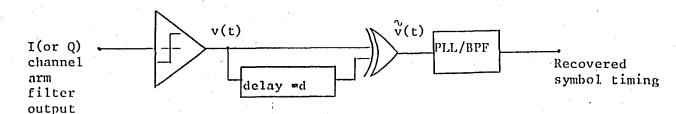

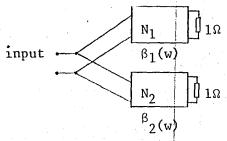

The symbol timing extraction, for QPSK signal, can be done basically in two ways, directly on the QPSK modulated signal, parallel symbol timing recovery (PSTR); |13|, or at the baseband, serial symbol timing recovery (SSTR): |14|. But both STR techniques employ nonlinear signal processing elements analog (balanced mixer) or discrete (exclusive-OR gate) type, which generate the discrete prectral components at the multiples of symbol rate, r<sub>s</sub>. The nonlinear element may be implemented by a differentiator, a full wave rectifier, a threshold crossing circuit, a half bit delay detector, a squarer, a fourth power circuit, exclusive-OR gate, a delay and multiply circuit. However the last two are superior over the rest, in the performance, complexity and cost |14|.

The delay and multiply PSTR scheme is faster in aquisition and when the delay element is perfectly calibrated, has 3dB higher performance compared to exclusive -OR gate SSTR scheme, however the former is more simpler to implement.

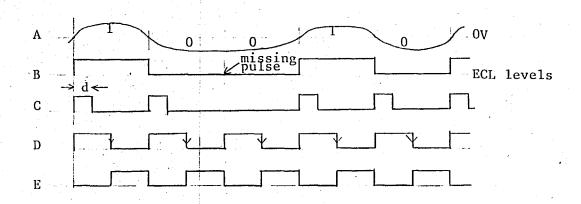

#### Exclusive -OR gate SSTR

Figure -10 : Exclusive -OR gate SSTR.

The symbol timing clock is recovered from either channel arm filter output of the demodulator, which contains filtered, non-retun-zero (NRZ) binary random sequence, corrupted by channel noise. We assume that this

equence is WSS, having mutually uncorrelated equiprobable symbols. The output of the hard limiter resembles a return-zero (RZ) random binary sequence, but it contains transition jitter, due to channel noise and intersymbol-interference (ISI), caused by arm filter. However an experimental evidence is given by the author |14| that, the undesired power of v(t), due to transition jitter, is negligible as compared to that of RZ continuous spectral components close to symbol rate frequency. So the jitter free power spectral density of the signal, at the output of hard limiter, having states  $(0,\Lambda)$  is given from appendix. A-4 as:

$$G_{VV(f)} = \frac{\Lambda^2}{4} \cdot T_S \sin^2 f T_S + \frac{\Lambda^2}{4} \cdot u_0(f)$$

Where  $T_S$  is the symbol duration, as before, and  $u_O(f)$  is the unit impulse function. It is clear that  $G_{VV}(f)$  has no spectral components at the symbol rate frequency. The power spectral density at the output of exclusive-OR gate is given as |14|.

$$G_{\widetilde{V}\widetilde{V}(f)} = \frac{2\Lambda^2 d^2}{T_S} \quad \operatorname{sinc}^2(f.d) + \frac{\Lambda^2.d^2}{T_S^2} \left[ u_O(f) + 2 \sum_{\Sigma \text{ sinc}}^{\infty} \sin^2(\frac{md}{T_S}) \right]$$

$$\cdot u_O(f - \frac{m}{T_S})$$

$$= C(f) + D(f)$$

where 'A' is the output high level of the hand limiter, as defined above and

<sup>\*</sup> It is advisable to employ both arms (I,Q) of the demodulator to extract the symbol timing. This is accomplished simply, by performing the operation of figure -10 (up to the band-pass filter) on both arms, independently and then (wire OR'ing the two paths before they enter to the band pass filter.

'd' is shown in Figure -10. It is obvious that it does contain line spectra, D(f), at the multiples of symbol rate frequency,  $\frac{1}{T_0}$ .

The value which determines the best operating point, is the ratio of discrete to residual continuous spectral power (defined as SNR), since it is this ratio which causes clock timing jitter at the output of the bandpass filter. If the bandpass filter is narrow enough (B  $\ll$  1/T<sub>S</sub>), the continuous spectrum of the signal within that bandwidth can be assumed flat, so the continuous spectral power at the output of the bandpass filter is:

$$C(1/T_s) = B. \frac{2\Lambda^2 d^2}{T_s} \cdot sinc^2 (d/T_s)$$

and the line spectral at the symbol rate frequency is :

$$D(1/T_s) = \frac{2\Lambda^2 d^2}{T_s^2} \cdot sinc^2 (d/T_s)$$

Therefore the signal to noise ratio, as defined previously, is:

(SNR) =

$$\frac{D(1/T_S)}{C(1/T_S)} = \frac{1}{B.T_S} = \frac{f_o}{B}$$

Where Q and  $f_{O}$  are the quality factor and center frequency of the bandpass filter, respectively.

From the last equation, we conclude that, the delay element, having delay d,  $0 < d < T_{\rm S}$ , has no effect on the performance, and high Q filter can reduce the clock timing jitter, at the expense of prolanged acquisition

time and inability to track the instabilities of the transmitted clock timing signal.

#### REMARK:

When bandpass filter is implemented by PLL with phase frequency detector, the phase frequency detector is misdirected by the random signal where some transitions are missing. (see timing diagram of Chapter -3.7.) The LC prefilter with high Q can introduce many transitions, of almost correct phase, each time it is driven by the data transitions of different phase, hence, improves the operation of phase detector.

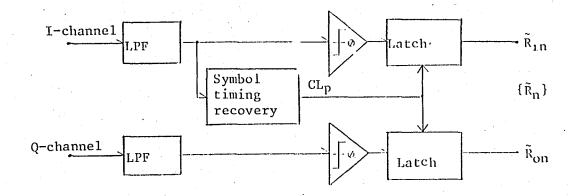

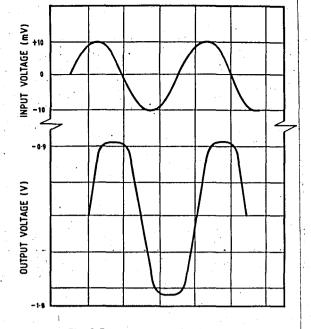

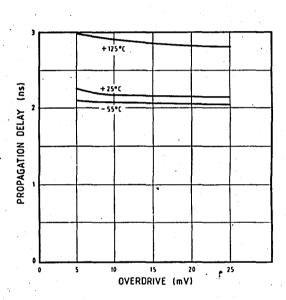

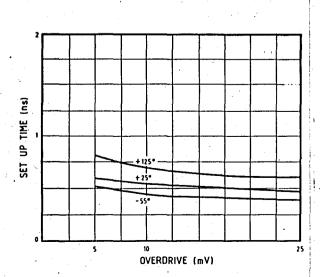

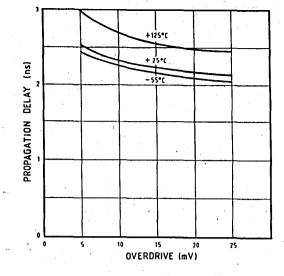

#### 2 - A.6 Demodulator

Figure -11 : Demodulator structure.

Demodulation is performed by passive lowpass filters (2 nd order Burtterworth) followed by zero voltage threshold comparators and latches, driven by STR module; due to high data rate and zero mean bipolar input signals. The disadvantage of passive lowpass filter is that, it introduces ISI, if it doesn't have sufficient bandwidth, however large bandwidth means

more noise power injected at the entry of the decision circuit.

The error performance degradation due to the passive filter and filter caused ISI becomes very complex even for the simple RC filter case, and this subject is not analyzed, but filter bandwidth is chosen equal to symbol data rate. |3|

# 2 - B. SPECTRUM and SPECTRAL EFFICIENCY

In appendix A.4 the spectral characteristics of digitially modulated signals (when the information source is WSS) are given. If we also assume that, rectangular baseband pulse shaping is employed and complex symbols are mutually uncorrelated having zero mean,  $m_{\rm I}$  = 0, and unity variance,  $\sigma_{\rm I}^2$  = 1, we get

$$p(t) = \begin{cases} A & 0 \le t \le T_S \\ 0 & else \end{cases}$$

$$|P(f)|^2 = A^2.T_S^2. \operatorname{sinc}^2(f.T_S)$$

So, equivalent lowpass power spectral density of the quadriphase modulated signal is:

$$G_{uu(f)} = \frac{\sigma_{I}^{2}}{T_{s}} \cdot |P(f)|^{2} + \frac{|m_{I}|^{2}}{T_{s}^{2}} |P(0)|^{2} \cdot u_{o}(f) = A^{2} \cdot T_{s} \operatorname{sinc}^{2}(f \cdot T_{s})$$

\* H. Stark and F.Z. Tuteur, "Modern Electrical Communications," Prentice-Hall, 1979.

and the modulated power density spectrum :

$$G_{ss}(f) = \frac{1}{2} \left[ G_{uu}(f-f_c) + G_{uu}(-f-f_c) \right]$$

On the other hand, the well known ISI free theoretical minumum bandwidth (Nyquist bandwidth) of a baseband information sequence, having a rate,  $r_s$  is:

$$B_{min} \ge r_s/2$$

where equality holds with a very special pulse shape, sinc pulse. However when the signal is double sideband modulated, it occupies the twice bandwidth at the RF channel, calling this bandwidth transmission bandwidth,  $B_{\mathrm{T}}$ , we get :

$$B_T = 2B_{\min} \ge r_s = \frac{r_b}{2}$$

So the bandwidth efficiency, BWEFF, is:

BWEFF =

$$\frac{r_b}{B_T} \le 2 \text{ bits/sec/Hz.}$$

Again equalitity holds only for sinc baseband pulse shaping and it is an upper bound. When  $\alpha$  roll of rised cosine pulse shaping is used, we get

$$B_T = (1+\alpha) r_S$$

BWEFF =

$$\frac{2}{1+\alpha}$$

b/s/H<sub>z</sub>

as a typical achivable efficiency.  $(\alpha \neq 0)$

# 2 - C. ERROR PERFORMANCE

The direct error performance calculation of DEQPSK modem is very complex |1,pp.161,164|, |2,pp.155|, and it is usually given graphically due to non-clementary functions. However binary phase shift keyed (BPSK) modem performance is extensively analyzed and can be adopted to DEQPSK case, giving considerable design insight.

IF the BPSK signal is corrupted by additive white Gaussian noise (AWGN) and demodulated by a matched filter receiver (or its error performance equivalent Nyquist channel receiver), the bit error probability of this system |1,2| becomes

$$P_b = \frac{1}{2}$$

erfc  $\sqrt{\delta b}$

where  $\delta b = \frac{\varepsilon}{N_0}$  = received SNR per bit,

$\varepsilon$  = Received energy in a single bit time,

$N_O$  = Double sided noise spectral density, erfc(X) = complementary error function.

If the BPSK signal has a rectangular baseband pulse shaping, and has a peak amplitude of 'A' at the input of receiver, from appendix-A.1 we have;

$$u(t) = \begin{cases} A & 0 \le t \le Tb \\ 0 & \end{cases}$$

$$\varepsilon = \frac{A^2 Tb}{2}$$

When there exists neither crosstalk nor interference between the signals on the I and Q arms of the QPSK demodulator (perfect coherent demodulation), the bit error probability of this modem is identical to bit error probability of BPSK modem |1|

$$P_{b,QPSK} = \frac{1}{2}$$

erfc  $\sqrt{\delta b}$

Since the differential decoding is performed after the signal regeneration, error multiplication by a factor of two can occur during decoding. So ideally we have:

$$P_{b,DEQPSK} = erfc \sqrt{\delta_b}$$

# III. HARDWARE AND HARDWARE DESCRIPTION OF THE SYSTEM

This section includes the circuit realizations and their operational descriptions of the blocks described in chapter -2; and some recommendations concerned with the operations and calibrations of those circuits. However, before proceeding to this chapter, we have some remarks to bear in mind.

First, the analog parts of the system were designed and calibrated (such as 50  $\Omega$  matched transistor RF amplifier) with the help NP.'s RF equipment set. So, the RF techniques used, for both analog |4,5| and digital |6| circuits, have not mensioned in this thesis.

Second, the system is realized in a modular way, enabling the operation of each module to be tested independently. However, this modular structure has introduced some redundancy for some digital circuits. So, in this chapter, we introduced and described two networks, (only for those reduntant circuits) one being the implemented circuit, and the other, called basic circuit, being the recommended circuit if modulator and demodulator had been conctructed on single cards, respectively.

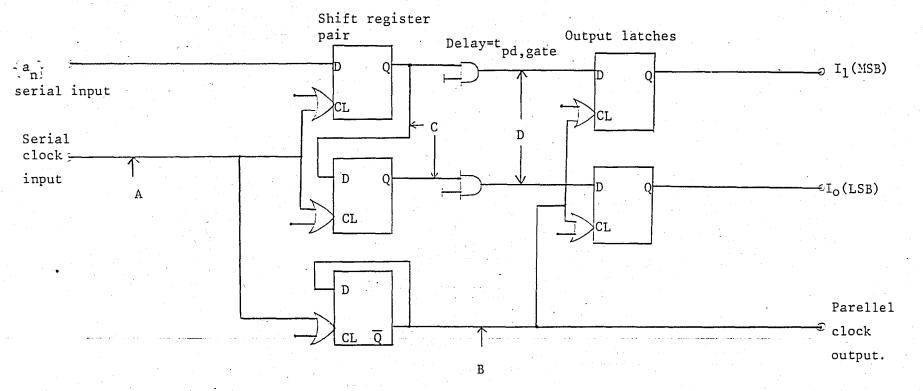

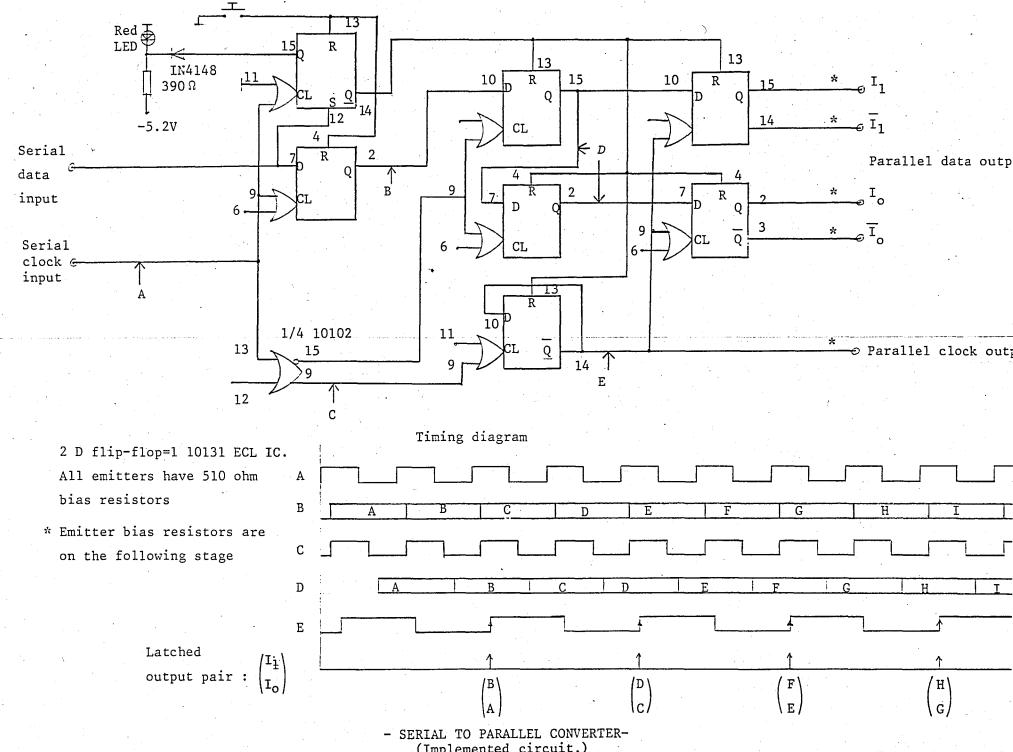

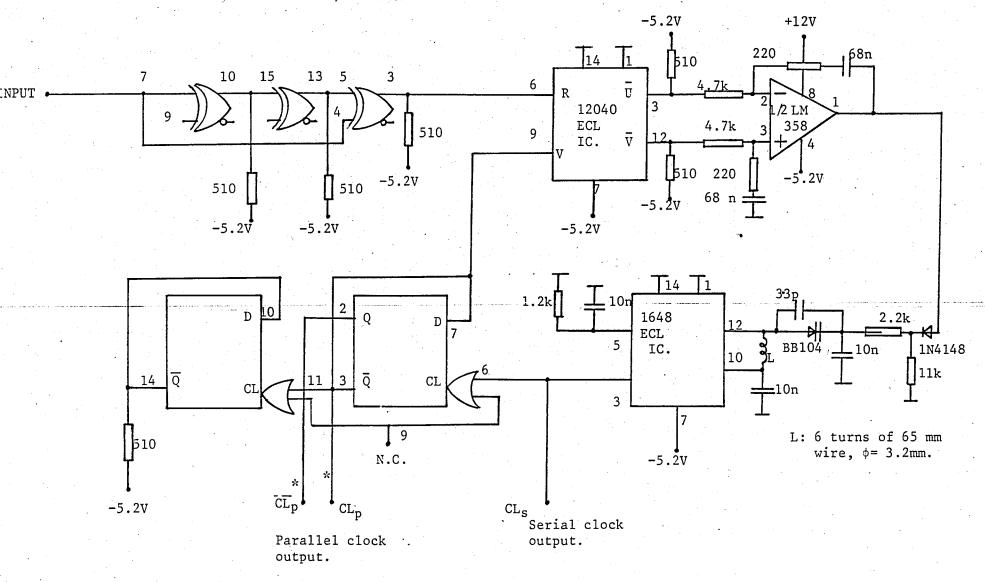

# 3.1- SERIAL TO PARALLEL CONVERTER

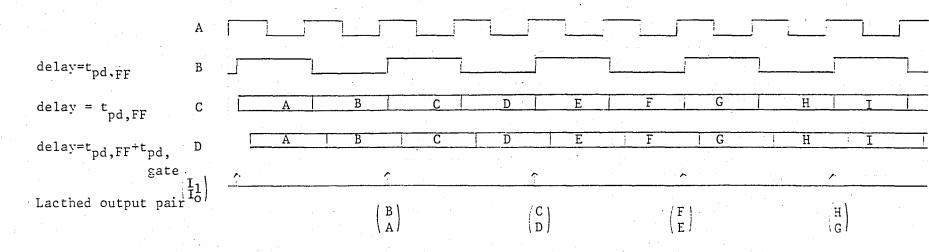

Basic circuit: The serial input stream is passed through a two bit shift register, and serial clock is divided by two, to form the parallel clock. However, due to finite delay of this divider, shift register outputs have to be delayed appropriately, before they are latched by output flip-flops, via parallel clock. Assume that, input data stream has a form

where  $^{\dagger}\Lambda^{\dagger}$  is the very first data bit sent, then, the output symbol sequence is formed as

$$\begin{pmatrix} I_1 \\ I_0 \end{pmatrix} = \begin{pmatrix} B \\ A \end{pmatrix}, \begin{pmatrix} D \\ C \end{pmatrix} , \cdots$$

which will be useful when converting to serial again, at the demodulator.

Implemented circuit: The implemented circuit differs somewhat. First the serial input sequence and the serial clock are buffered; and the shift register pair is clocked with the falling edge of the serial clock. So, Tb/2

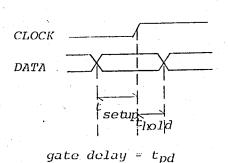

# \* 10131 ECL D flip-flop requirements :

Data should be stable  $t_{set,up}(1 \text{ ns})$  seconds before and  $t_{hold}$  (0.75 ns) seconds after the rising edge of the clock pulse. So, making use of the timing diagram of the basic circuit, we get

secods delay is generated in between the shift register pair and output lacthes. (See timing diagram.) There is still a third difference, the reset circuit, added for the check of circuit operation during test. The very first high state of data will enable the operation of the serial to parallel converter and acts as a kind of synchronizer. The basic circuit should not include this reset circuit.

- SERIAL TO PARALLEL CONVERTER (Basic circuit)

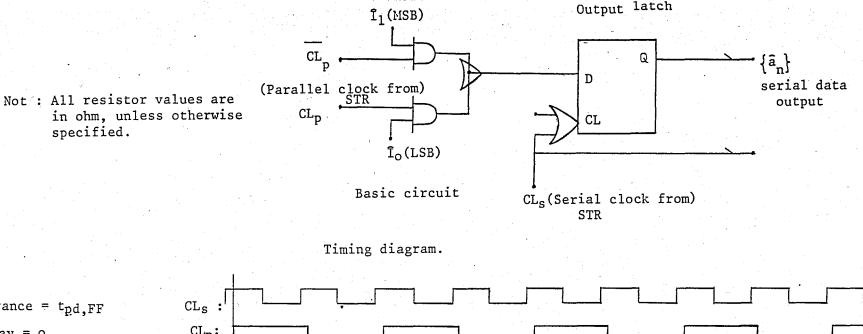

The basic circuit is very simple in this case. The parallel data outputs ( $\hat{\mathbf{I}}_1$ ,  $\hat{\mathbf{I}}_0$ ) are sampled and latched by the serial clock,  $CL_s$ , twice in a single symbol time,  $T_s$ . Each time as the symbol clock (also called parallel clock),  $CL_s$ , makes a positive transition, a new symbol appears at the inputs of the parallel to serial converter, and this symbol has a form

$$\begin{pmatrix} \widehat{\mathbf{I}}_1 \\ \widehat{\mathbf{I}}_0 \end{pmatrix} = \begin{pmatrix} \widehat{\mathbf{B}} \\ \widehat{\mathbf{A}} \end{pmatrix} , \begin{pmatrix} \widehat{\mathbf{D}} \\ \widehat{\mathbf{C}} \end{pmatrix} , \dots$$

So, at the high state of the parallel clock, least significant bit of the symbol,  $\hat{I}_0$ , is enabled and latched first, then, at the low state, most significant bit,  $\hat{I}_1$ , is enabled and latched. Therefore, the output sequence is reconstructed as the original one, as

$$(\ldots, \hat{D}, \hat{C}, \hat{B}, \hat{A})$$

In the implemented circuit, the divide by two flip-flop, just after the VCO of the STR card, is also copied in this card, which is in the same phase as the original one, and rest is totally the same.

<sup>\*</sup> See serial to parallel converter section (3-1.).

specified.

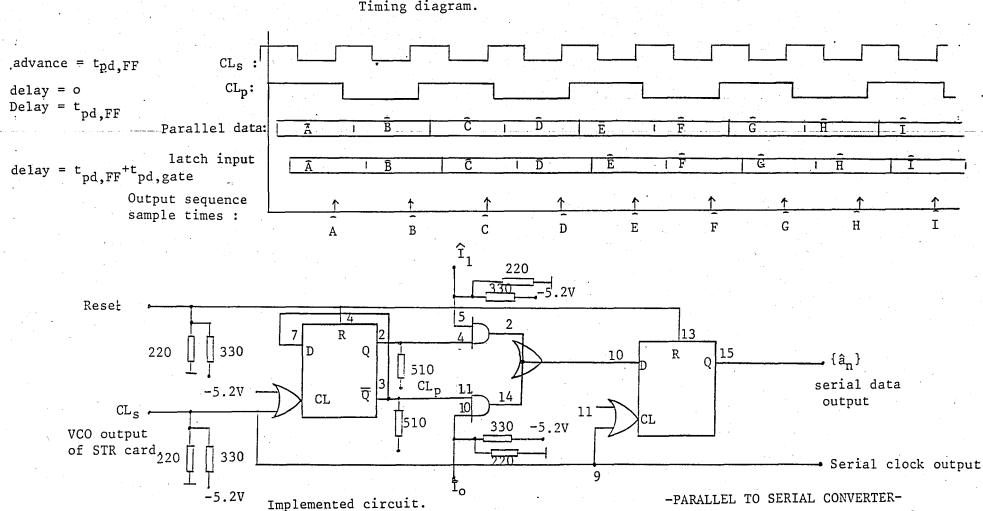

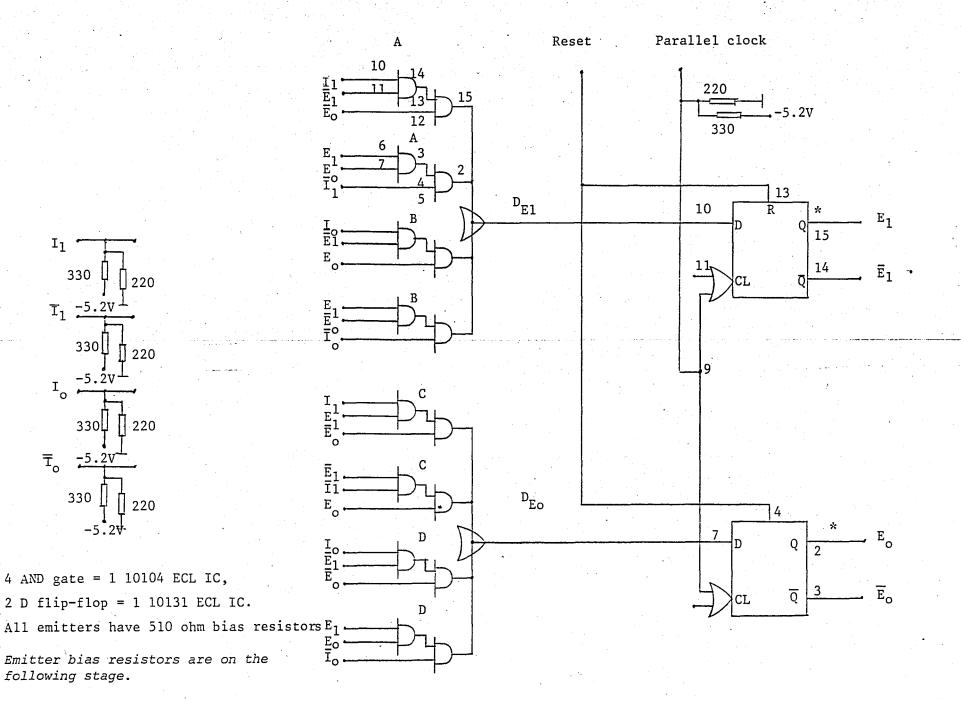

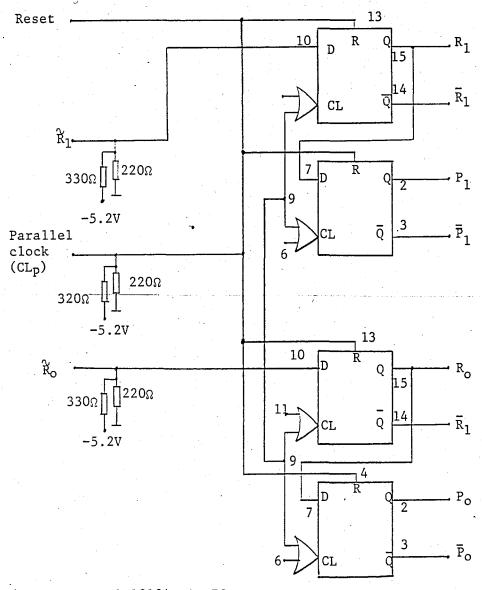

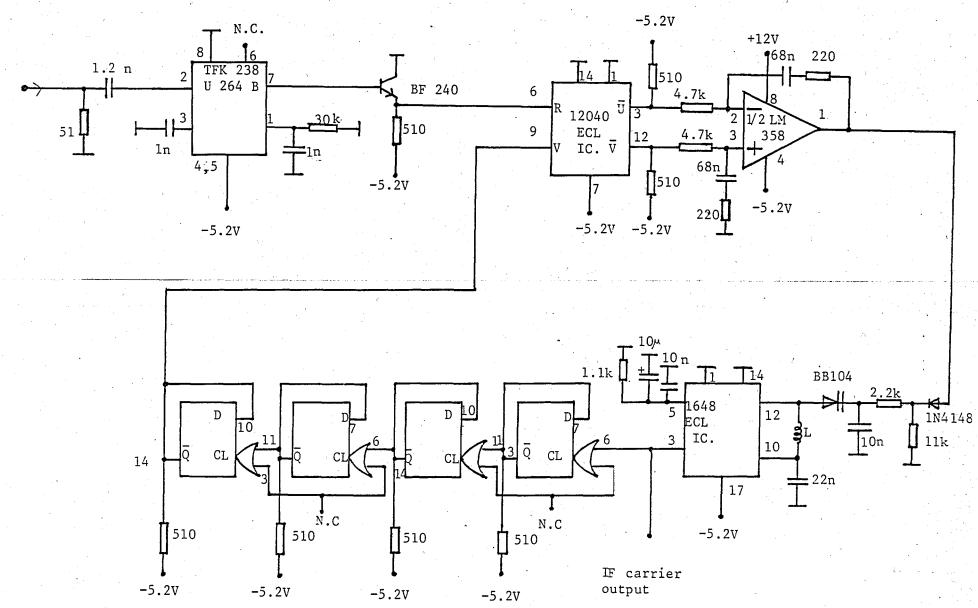

Referring to differential decoder circuit, the symbol sequence,  $\{\tilde{R}_1\tilde{R}_0\}$ , being the outputs of the decision circuits, has not a proper form to operate the differential decoder circuit, since it has state transitions just on the middle of succesive falling edges of the symbol clock,  $CL_p^*$ . The first D flip-flops convert this sequence into a proper form,  $\{R_1, R_0\}$ , and the second D flip-flops serve as delay elements. The rest of this circuit and the differential encoder circuit perform the respective Boolen function operations, as described in chapter -2.

However, due to simplicity, it is advisable to use J-K flip-flop realization in the encoder circuit.

<sup>\*</sup> See also chapters 3-6, and 3-7.

4 AND gate = 1 10104 ECL IC, 2 D flip-flop=1 10131 ECL IC. All emitters have  $510\Omega$  bias resistors

-GRAY CODED DIFFERENTIAL DECODED-

<sup>\*</sup> Emitter bias resistors are on the following stage.

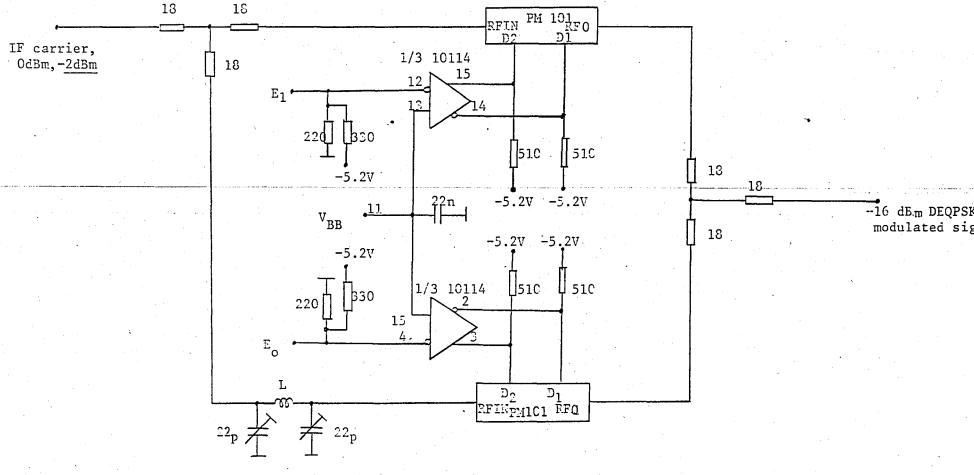

The modulator is builded around biphase modulator IC, PM 101, whose electrical characteristics are given in IC specifications section. PM 101 modulators are driven by the line receiver IC, with 10 mA drive current in either state. The IF oscillator (140 MHz external oscillator) is spilled into two, to drive the inphase (I) and quadriphase (Q) channel phase modulators. The Q channel oscillator is 90° phase shifted prior to the entry into the modulator. The most significant bit of the symbol, I1, is fed into the I channel and least significant bit, I0, into the Q channel modulators, respectively, which must be remembered when constructing the demodulator. Finally outputs of I and Q channel modulators are resistively summed, to form the composite DEQPSK modulated IF signal.

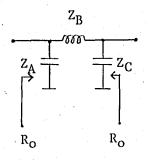

The phase shift circuit is a lossless impedance matching network with prescribed phase shift.

So it is a minimum 3 element network. The formulas for 'T' network are

$$z_A = z_C = -j R_O \left( \frac{\sin \beta}{1 - \cos \beta} \right)$$

$$Z_B = j R_O sin\beta$$

If we define  $\beta$  = +  $\pi/2$  we obtain one inductor only and we get

$$X_L = X_C = R_O$$

.

L: 4 turns of 0.65 mm wire,  $\phi = 2.2$  mm.

-MODULATOR AND SUMMER STAGE-

Not: Resistor values are in ohm, unless otherwise specified.

L = 5 turns of 65 mm wire, = 3.0 mm

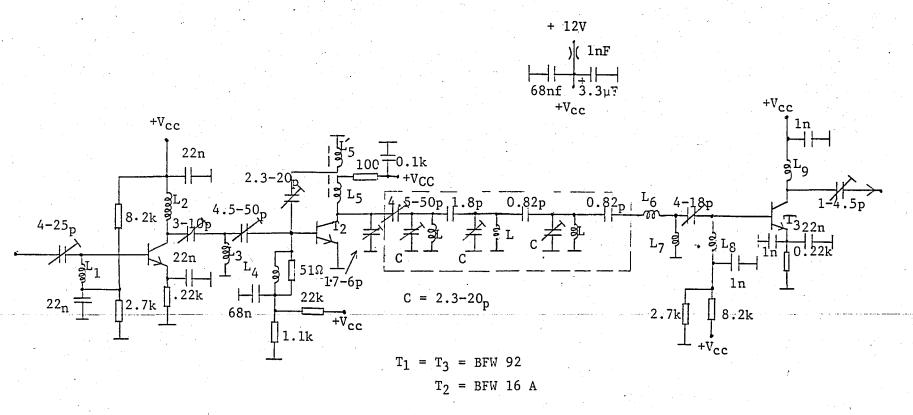

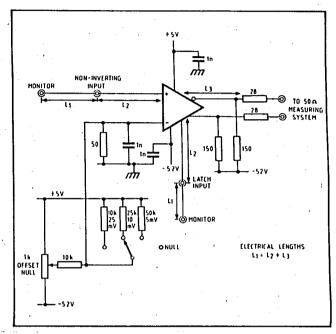

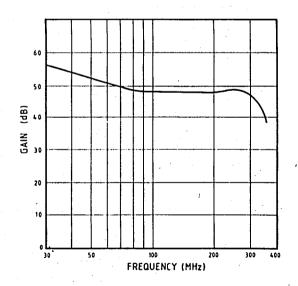

Gain: 27 dB

Freq. - band : 40-860 MHz

Input/output impedance: 750

T<sub>1</sub>, T<sub>2</sub> : BFW 92 T<sub>3</sub> : BFW 16 A

Not: Resistor values are in ohm, unless otherwise specified.

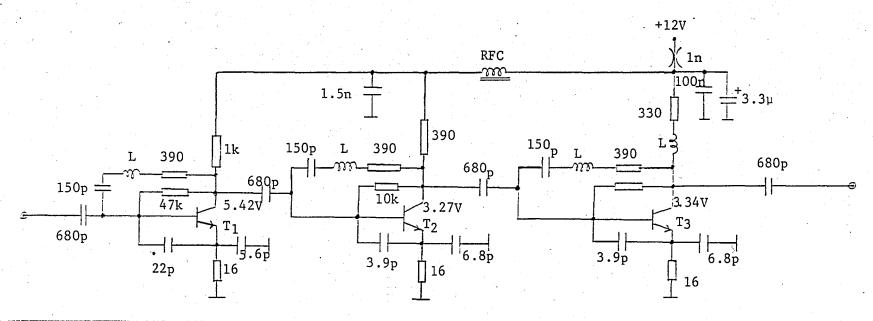

## 3-5 . IF AMPLIFIER STAGE

This network was already available at the laboratory and duplicated for this modem.

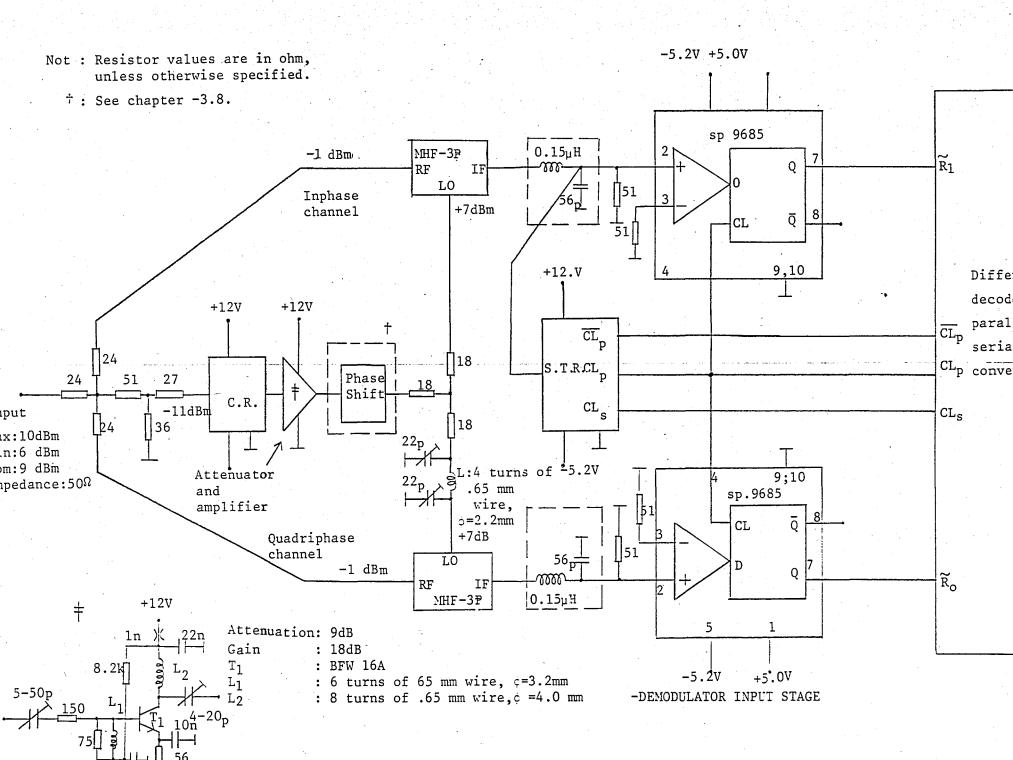

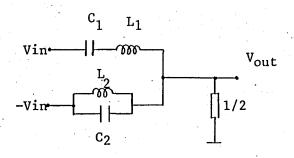

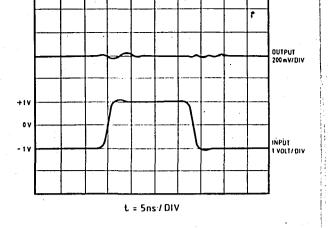

The received DEQPSK modulated signal is divided into three paths (where power division ratios are shown on the circuit diagram), two into RF channel of the double balanced mixers and one into the carrier recovery (CR) circuit. The output of CR circuit is an ECL gate and is insufficient to drive the two LO inputs of the mixers. So, it is fed to the attenuator followed by single amplifier circuit. The attenuator is a 96 dB 'L' section attenuator, having 180  $\Omega$  and 50  $\Omega$  impedances at the gate and transistor sides respectively, in order to minimize the loading on the gate. The transistor amplifier output is divided into two, one directly driving the LO input of the inphase (I) channel mixer, and the other, driving the LO input of the quadrature (0) channel mixer, after it is passed through a 90° phase shift network. Outputs of mixers are lowpass filtered, with second order Butterworth filters (called arm filters), having 70 MHz 3 dB bandwidths. The I channel filter output is applied to the symbol timing recovery (STR) circuit, which extracts the symbol timing signal, CLp. Arm filter outputs are also applied to the decision comparators, an these comparators are enabled by the STR circuit, with the symbol timing signal,  $CL_p$ , to form the digital  $I(\tilde{R}_1)$ and Q ( $\tilde{R}_{O}$ ) signals.

<sup>\*</sup> See footnote of chapter 3-4.

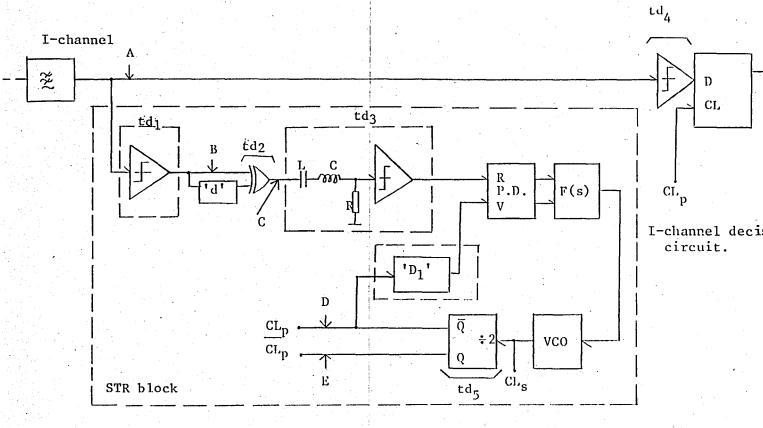

This circuit extracts the data synchronization signal of the modulator input data stream, and requires fine calibration due to high data rate.

The delay element,'d', is implemented simply by cascaded exclusive -OR ECL gates. The LC prefilter and the following comparator is not included in the circuit card, but, in connection with chapter -2 and the timing diagram below, it is advisable to involve this circuit, in order to improve the operation of the phase detector.

The output of the VCO, being t<sub>d5</sub> seconds ahead of the parallel clock (CL<sub>p</sub>), is tuned to 140 MHz and is used as a serial clock, CL<sub>s</sub>, to drive the parallel to serial converter circuit and all the circuits external to the DEQPSK demodulator. The outputs of the divide by two flip-flop, CL<sub>p</sub>, and its complement,  $\overline{\text{CL}}_p$ , are the basic reference synchronization signals extracted at the demodulator. Since the CL<sub>p</sub> signal enables the decision circuit (see timing diagram), it requires fine calibration, in order for the system performance not to degrade. This is accomplished simply, by inserting a digital delay element, 'D1', in between the output of divide by two flip-flop and 'V' input of phase detector, which effectively removes the signal path length differences of STR circuit and decision circuits.

<sup>\*</sup> This circuit is not complete yet, so it is not inserted into the system.

Figure-12: Serial symbol timing recovery scheme, extended block diagram.

Notes

- 1) Framed elements are not included in the implemented circuit (see text).

- 2)  $D_1 \stackrel{\triangle}{=} td_1 + td_2 + td_3 td_4$

Timing diagram: Ideal elements and jitter free input signal case

Note: the arrow of the 'D' waveform designates the optimum sampl

times for decision circuits.

Not: Resistor values are in ohm, unless otherwise specified.

- \* Emitter bias resistors are on the stages drived by this unit.

- 2 D flip-flop = 1 10131 ECL IC.

- 3 exclusive-OR gate = 3/4 10113 ECL IC.

-SYMBOL TIMING RECOVERY STAGE-

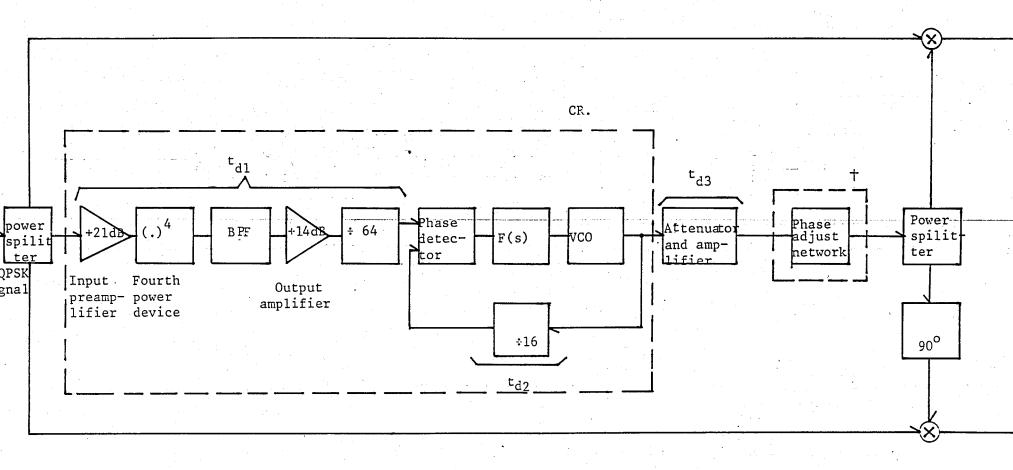

This circuit extracts the IF carrier (being DEQPSK modulated) of the modulator and requires fine calibration in order for overall performance not to degrade. (See remark.)

The input preamplifier is used for both isolation and gain purpose before driving the fourth power device. 'L' section impedance matching is performed on both input and output, with HP impedance matching set. The fourth power device is a single transistor biased to the cut off region. The output of this transistor is tuned (parallel tank) to 560 MHz, while input is matched ('T' network) at 140 MHz with large signal parameters. For proper operation in the wide frequency range (110 MHz - 170 MHz) it is also neutralized. Output of this stage feeds a bandpass filter located at 560 MHz. (This filter was already available at the laboratory). Finally, an output amplifier is used to bring the signal to a sufficient level (+10 dBm, +8 dBm) to drive the prescaler. It is again a transistor amplifier and its input and output are matched at 560 MHz, with two 'L' sections. The PLL section (whose card was also available) sees a divide by 64 prescaler, operating on the reference signal path, and divide by 16 circuit, operating at the feedback signal path. Therefore, the VCO output is locked to one fourth of the reference signal, i.e. IF frequency (140 MHz) is extracted at the output of loop VCO. The maximum VCO frequency is set to 145 MHz, since otherwise feedback divide loop does not operate properly, due to speed limitations of those IC's.

Remark: Due to finite delay of the elements in the CR circuit signal

path, the LO inputs of arm mixers do not have 0° phase IF carrier signal. This delay, called D2, is infact small, but still cause large phase errors due to high IF carrier signal. (Phase error = 2Nf<sub>IF</sub>D<sub>2</sub>) So, it is recommended to put a phase shift circuit (see figure -13) in order to compensate this phase error. The calibration operation can be done best experimentally, in a very simple way, as follows. Send If carrier signal (140 MHz) to the demodulator input. Observe the output of I channel arm mixer and adjust the phase shift, such that the mixer output contains twice of IF carrier frequency and a DC component only.

Figure - 13 : CR extended block diagram.

$$D_2 = t_{d1} - t_{d2} + t_{d3}$$

: See text.

|                                                                      | diameter<br>(mm)                       | turns                 | wire<br>diameter<br>mm          | •                                                                                                           | : 10 dBm : 8 dBm              |

|----------------------------------------------------------------------|----------------------------------------|-----------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------|-------------------------------|

| L <sub>1</sub><br>L <sub>2</sub><br>L <sub>3</sub><br>L <sub>4</sub> | 3.2<br>4.0<br>3.3<br>3.0<br>2.0        | 6<br>8<br>8<br>4<br>2 | .65<br>.65<br>.65<br>.65        | $Nom:-11 dBm$ Nom Impedance: $50\Omega$ Impedance Nominal Nominal Input output Frequency: 140 MHz Frequency | : 9 dBm<br>: 50Ω<br>: 560 MHz |

| L5<br>L6<br>L7<br>L8<br>L9                                           | 2.0<br>2.4<br>1.4<br>1.5<br>1.2<br>4.0 | 2<br>4<br>4<br>3<br>3 | .90<br>.75<br>.65<br>.65<br>.65 | - CARRIER RECOVERY INPUT STAGE-                                                                             |                               |

Not: Resistor values are in ohm unless otherwise specified.

2 D flip flop = 1 10131 ECL IC.

L = 6 turns of .65 mm wire,  $\phi$ =3.2 mm

## IV. EVALUATION AND CONCLUSION

We have taken the very first step in the establishment and improvement of a quadriphase modem. The system structure was selected to be DEQPSK and realized in a modular way. All of the modules, except the STR module, have been tested and put together to form the DEQPSK modem.

The calibration of the modulator has been done, and the whole modulator has been made ready to operate on a single card, with the recommendations of chapter -3. But the 90° phase shift network, on the IF oscillator path, is better to be redesigned with the help of appendix B-2, or, if available, a qudrature (90°) hybid can still improve the operation of the modulator.

The same recommendation, for the  $90^{\circ}$  phase shift network, also applies to the demodulator's quadrature arm  $90^{\circ}$  phase shift network. Having supplied the data synchronization signals ( $CL_p$ ,  $\overline{CL}_p$ ,  $CL_s$ ) from the modulator card, the whole system had been tested only at 8 Mb/s data rate, due to nonavailability of proper data source, at that time.

The next step to be performed, is to put the STR circuit into operation in conform to the other parts of the demodulator. By this way, once fixing the structure of the demodulator, it is advisable to combine the demodulator,

but mainly the analog portions of it, in a single card, since otherwise neither fine system calibration, nor full data rate of operation is possible to manage. After all, when both modulator and demodulator being implemented on single cards, the system will become to ready undergo performance test and to use.

## APPENDICES

## A - 1 : BANDPASS SIGNALS

1. A real valued narrow band-pass signal s(t) in the vicinity of a frequency  $\mathbf{f}_{\text{C}}$  can be expressed as :

$$s(t) = a(t) \cos (2\pi f_c t + \theta(t))$$

$$= x(t) \cos w_c t - y(t) \sin w_c t$$

$$= R_e \{ u(t)_e^{j2\pi f_c t} \}$$

where a(t): envelope of s(t)

f<sub>c</sub>: carrier of s(t)

x(t), y(t): quadrature components of s(t)

u(t): complex envelope of s'(t)

$\Theta(t)$ : phase of  $\xi(t)$

and

$$x(t) = a(t) \cos \theta(t)$$

$y(t) = a(t) \sin \theta(t)$

$$u(t) = a(t) e^{j\theta(t)} = x(t) + jy(t)$$

These components are called the low-pass signals since the frequency contents of them are concentrated at low frequencies with respect to  $\,{\rm f}_{\rm c}\,$  due

to narrow band nature of s(t). It is simple to show that

F.T.

$$\{ s(t) \} = S(f) = \frac{1}{2} \left[ U(f - f_c) + U^*(-f - f_c) \right]$$

$\{ \text{Energy of the signal } \} = \epsilon = \langle s^2(t) \rangle = \int_{-\infty}^{+\infty} dt \ s^2(t) = \frac{1}{2} \int_{-\infty}^{+\infty} |u(t)|^2 dt + \frac{1}{2}$

$$\int_{-\infty}^{+\infty} dt |u(t)|^2 \cos(4\pi f_c t + \theta(t))$$

$$\varepsilon \cong \frac{1}{2} \int_{-\infty}^{+\infty} dt |u(t)|^2 = \frac{1}{2} \cdot \int_{-\infty}^{+\infty} dt \ a^2(t)$$

2. Real time response band-pass filter h(t) (or H(f)) can be expressed interms of equivalent complex low-pass filter component, c(t), (or C(f)) as follows;

where 2 is arbitrary since we could define  $C(f-f_c) = \frac{1}{2} H(f) u_1(f)$

3. Response of band-pass system to band-pass signal:

Let:

$$s(t) = Re \{ u(t) e^{j2\pi f_{c}t} \}$$

$$h(t) = 2Re \{ c(t) e^{j2\pi f_{c}t} \}$$

then

$$R(f) = S(f) \cdot H(f) = \frac{1}{2} \left[ U(f - f_c) + U^*(-f - f_c) \right] \cdot \left[ C(f - f_c) + C^*(-f - f_c) \right]$$

$R(f) = \frac{1}{2} \left[ U(f - f_c) \cdot C(f - f_c) + U^*(-f - f_c) C^*(-f - f_c) \right]$

since crossterms vanishes due to narrow band nature.

$$R(f) \stackrel{\triangle}{=} \frac{1}{2} \cdot \left[ V(f-f_c) + V^*(f-f_c) \right]$$

where

$$V(f) = U(f) \cdot C(f)$$

Rewriting

$$v(t) = u(t) * c(t) ; V(f) = U(f) . C(f) and r(t) = Re { v(t) e^{j2\pi f_{ct}}}$$

Bandpass and Lowpass Representations

$$s(t) \qquad h(t) \qquad r(t)$$

$$u(t) \qquad c(t) \qquad v(t)$$

So that transformation from band-pass to low-pass (or vice versa) can be done at any point on the block diagram and the rest can be analyzed with that representation.

# A - 2 : BANDPASS STATIONARY STOCHASTIC PROCESS REPRESENTATION

Suppose s(t) is a sample function of aw.S.S. stochastic process with power spectral density (p.s.d) of  $G_{ss}(f)$  located in the vinicity of  $f_c$ . The stochastic process s(t) is said to be narrow band band-pass process if the width of  $G_{ss}(f)$  is much smaller than the carrier  $f_c$ . In that case, the sample function s(t) has equivalent low-pass representation given in app. A-1. The autocorrelation (AC) function of s(t) is:

$$R_{SS}(t,\zeta) = E \{ s^{*}(t) \ s(t+\zeta) \}$$

$$= E \{ [x(t) \cos 2\pi f_{c}t - y(t) \sin 2\pi f_{c}t] . [x(t+\zeta) \cos 2\pi f_{c}(t+\zeta) - y(t+\zeta) \sin 2\pi f_{c}(t+\zeta) ] \}$$

expending and remembering that s(t) is W.S.S.

$$R_{SS}(t+\zeta,t) = R_{SS}(\zeta)$$

and setting the time dependent coefficients to zero we get  $R_{\rm SS}(\zeta)$  and some relations ;

$$R_{xx}(\zeta) = R_{xx}(\zeta) \cdot \cos 2\pi f_{c} \zeta - R_{yx}(\zeta) \cdot \sin 2\pi f_{c} \zeta$$

$$R_{xx}(\zeta) = R_{yy}(\zeta)$$

$$R_{xy}(\zeta) = - R_{yx}(\zeta)$$

indicating that AC functions of quadruture components are interrelated. Now we can define AC function of equivalent low-pass process as follows

$$u(t) = x(t) + iy(t)$$

$$R_{uu}(\zeta) = \frac{1}{2} \cdot E \{ u^*(t) u(t+\zeta) \}$$

So that, using above interelation we get:

$$R_{UU}(\zeta) = R_{XX}(\zeta) + j R_{YX}(\zeta)$$

hence:  $R_{ss}(\zeta) = Re \{ R_{uu}(\zeta) e^{j2\pi f} c^{\xi} \}$

informing that the AC function of band-pass stochastic process is completely determined from the AC function of equivalent low-pass process, u(t). Finally taking the Fourier transform and noting that for any stationary complex process,  $G_{uu}(f)$  is real function of frequency (since  $R_{uu}(\zeta) = R_{uu}(-\zeta)$ )

$$G_{ss}(f) = \frac{1}{2} \left[ G_{uu} (f-f_c) + G_{uu} (-f-f_c) \right]$$

A - 3: M-ARY PSK SIGNAL REPRESENTATION IN TERMS OF EQUIVALENT LOW PASS FORM.

Digital phase modulation of a carrier results, when the binary digits from the information sequence,  $\{a_n^{-1}\}$ , are mapped into a set of discrete phases of the carrier. An M-ary PSK signal is generated by mapping blocks of k=log<sub>2</sub>M binary digits of the sequence, $\{a_n\}$ , into one of M corresponding phases:

$$\theta_{\rm m} = 2\pi ({\rm m}-1)/{\rm M} \qquad {\rm m} = 1, {\rm M}.$$

Resulting equivalent low pass signal:

$$u(t) = \sum_{n} I_{n} p(t - \frac{n}{r_{s}})$$

where

$$r_s = \text{symbol rate} = \frac{1}{T_s}$$

p(t) = baseband pulse shape defined in the interval  $[0,T_s]$   $I_n = e^{j\theta}n$

So,QPSK or DEQPSK modulated signal can be represented in terms of equivalent lowpass from as:

$$u(t) = \sum_{n} I_{n} p \left(t - \frac{r}{r}\right)$$

\* The statistics of  $\{I_n\}$  are modified by the differential encoder, which inturn, modifies the power spectrum density of the DEQPSK modulated signal.

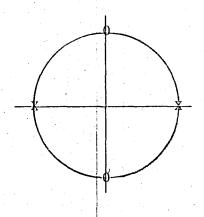

and  $I_n$  takes one of four possible values, say  $(\pm \frac{1}{\sqrt{2}} \pm i \frac{1}{\sqrt{2}})$  or  $(\pm 1, \pm i)$ .

Equivalent low pass form of (DE)QPSK signal, u(t), can also be expressed in a form close to quadrature amplitude modulation (QAM) scheme as follows

$$u(t) = \sum_{n} I_{n} p(t - \frac{n}{r_{s}}) = \sum_{n} (I_{nr} + j I_{nq}) p(t - \frac{n}{r_{s}})$$

$$s(t) = \sum_{n} I_{nr} p(t-n/r_s) \cos 2\pi f_c t - \sum_{n} I_{nq} p(t-n/r_s) \sin 2\pi f_c t$$

where  $\{I_{nr}\}$  and  $\{I_{nq}\}$  are both complex binary sequences having the property

$$\left|\mathbf{I_{nr}}\right|^2 = \left|\mathbf{I_{nq}}\right|^2$$

Thus, (DE)QPSK modulated signal can be regarded as two BPSK modulated signals operating in quadrature, if  $\{I_{n_r}\} = \{\pm 1\}$  is a real and  $\{I_{n_q}\} = \{\pm j\}$  is an imaginary binary sequences respectively.

I<sub>n</sub> domain

$X : elements of \{I_{nr}\}$

0 : elements of  $\{I_{nq}\}$

## A - 4: SPECTRAL CHARACTERISTICS OF DIGITALY MODULATED SIGNALS

Remembering appendix  $\Lambda$  - 2, it is sufficient to the determine the autocorrelation (AC) function and power spectum density (p.s.d.) function of the equivalent low-rass process, u(t), in order to determine the AC function of the sample function, s(t), as defined in app.  $\Lambda$ -1. Starting with

$$u(t) = \sum_{n} I_{n} P(t-nT_{S}) ; T_{S} = \frac{1}{r_{S}}$$

$\mathbf{I}_n$  ; is the  $n\underline{t}\underline{h}$  real or complex valued information symbol

p(t); is the baseband pulse shape, real or complex valued, defined in the interval  $\left[0,T_{S}\right]$ .

We assume that the sequence of information symbols  $\{1_n\}$  is W.S.S with

$$E \{I_n\} = m_T$$

$$\frac{1}{2} E\{I_n^* I_{n+m}\} = R_{II}(m)$$

so that with the help of app. A.2

$$R_{uu}^{--}(t+\zeta,t) = \frac{1}{2} E \{ u^{*}(t) u(t+\zeta) \} = \frac{1}{2} \sum_{n,m} E \{ I_{n}^{*}I_{m} \} p^{*}(t-nT_{S})p(t-mT_{S}+\zeta)$$

$$= \sum_{m,n} R_{II}(m-n) p^{*}(t-nT_{S})p(t+\zeta-mT_{S})$$

=

$$\sum_{m} R_{II}(m) \sum_{n} p^{*}(t-nT_{S}) \cdot p(t+\zeta-nT_{S}-mT_{S})$$

The inner summation is periodic in t variable, with period  $T_{s,so}$  is  $R_{uu}(t+\zeta,t)$

$$R_{uu}(t+\zeta+T_s; t+T_s) R_{uu}(t+\zeta, b)$$

Also  $E\{u(t)\}=m_I$ .  $\Sigma$   $p(t-nT_S)$  is too periodic with period  $T_S$ . Therefore u(t) is a cyclostationary process. The AC function of a cyclostationary process is found by time averaging  $R_{uu}$   $(t+\zeta,t)$  in order to eliminate t variable:

$$R_{uu}(\zeta) = \frac{1}{T_{s}} \int_{-T_{s}/2}^{T_{s}/2} dt \ R_{uu}(t+\zeta,t) = \sum_{s} R_{II}(s) \cdot \frac{1}{T_{s}} \int_{-T_{s}/2-nT_{s}}^{T_{s}/2-nT_{s}} dt \cdot p(t) p(t+\zeta-mT_{s})$$

$$= \Sigma R_{II}(m) \frac{1}{T_g} \int_{-\infty}^{+\infty} dt p^{*}(t) .p(t+\zeta-mT_g)$$

Since p(t) is a deterministic energy signal (0 <  $\int_{\infty}^{\infty} |p(t)|^2 dt < \infty$ ) its AC function given as:

$$R_{pp}(\zeta) = \langle p(t), p(t+\zeta) \rangle = \int_{-\infty}^{+\infty} dt p^{*}(t)p(t+\zeta)$$

Hence

$$R_{uu}(z) = \frac{1}{T_s} \sum_{m} R_{II}(m) \cdot R_{pp}(\zeta - mT_s)$$

Finally the average p.s.d. function is:

$$G_{uu}(f) = \frac{1}{T_s} \int_{-\infty}^{+\infty} d\zeta \left[ \sum_{m} R_{II}(m) R_{pp}(\zeta-mT_s) \cdot e^{-j2\pi f\zeta} \right]$$

$$= \frac{1}{T_s} \sum_{m}^{\Sigma} R_{II}(m) \int_{-\infty}^{+\infty} d\zeta R_{pp}(\zeta - mT_s) e^{-j 2^{\pi} f \zeta}$$

$$= \frac{1}{T_{s}} \cdot \sum_{m} R_{II}(m) e^{-j2\pi f m} T_{s} \int_{-\infty}^{-\infty} d\zeta R_{pp}(\zeta) e^{j2\pi f \zeta}$$

So:

$$G_{uu}(f) = \frac{1}{T_S} |P(f)|^2 G_{II}(f)$$

where P(f) = F.T. { p(t) } ,

$$G_{II}(f) \stackrel{\Delta}{=} \sum_{m} R_{II}(m) e^{-j2\pi f m T_s}$$

.

It is interesting to note that  $G_{II}(f)$  is the exponential Fourier (extention) series with the  $R_{II}(m)$  as  $\pi$  Fourier coefficients. Hence

$$R_{II}(m) = T_s \int_{-\frac{1}{2}T_s}^{\frac{1}{2}T_s} df G_{II}(f) e^{\frac{j}{2}\pi fmT_s}$$

Let us consider the case, for which the information symbols in the sequence are complex and mutually uncorrelated. Therefore

$$E \{I_n\} = m_I$$

;  $E \{I_n^*\} = m_I^*$

$$\sigma_{T}^{2} = E \{ | I_{n} - E\{I_{n}\}|^{2} \} = E \{ |I_{n}|^{2} \} - |m_{I}|^{2} \}$$

$$E \{I_{n}^{*}I_{n+m}\} = \begin{cases} E \{|I_{n}|^{2}\}\} & m = 0 \\ E \{I_{n}^{*}\}_{n}E \{I_{n+m}\} & m \neq 0 \end{cases}$$

$$R_{II}(m) = E \{ I_n^* I_{n+m} \} = \begin{cases} \sigma_I^2 + |m_I|^2 & m = 0 \\ |m_I|^2 & m \neq 0 \end{cases}$$

So

$$G_{II}(f) = \sigma_I^2 + |m_I|^2 = \sum_{m} e^{-j2\pi f m T_S}$$

$$= \sigma_{\rm I}^2 + \frac{|{\rm m_I}|^2}{{\rm T_s}} \sum_{\rm m} u_{\rm O} ({\rm f} - \frac{{\rm m}}{{\rm T_s}}) ; u_{\rm O}({\rm f}) \text{ is the unit impulse function}.$$

$$G_{uu}(f) = \frac{\sigma_{I}^{2}}{T_{s}} \cdot |P(f)|^{2} + \frac{|m_{I}|^{2}}{T_{s}^{2}} \sum_{m} |P(f)|^{2} \cdot \eta_{s} (f - \frac{m}{T_{s}})$$

## B - I. PLL, BRIEF THEORY.

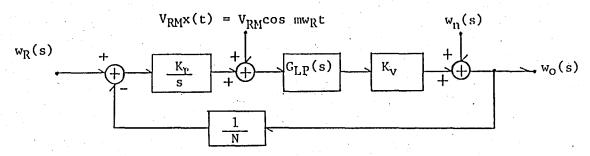

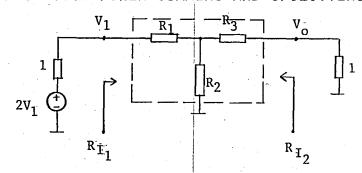

We shall consider the operation of the PLL in its linear range, so that, signals have small perturbations around the nominal values, loop parameters may be considered constant and simple s-domain (or z-domain) analysis can lead to simple but powerful design equations. Let us start with the block diagram, shown.

Where,  $G_{\rm LP}(s)$  is the loop filter (active or passive),  $K_{\rm V}({\rm rad/sec/volts})$  is the voltage controlled oscillator (VCO) frequency gain,  $W_{\rm R}(s)$  VCO noise in the vicinity of nominal VCO output frequency ( $f_{\rm O}$ ), and  $K_{\rm V}$  (volts/radian) is the phase detector gain. Phase detector is modelled as to pass only the low frequency error signal spectrum (spectrum around DC component of the error signal), so, the rest of the error signal spectrum (around all possible harmonics of the reference frequency), which constitute the undesired portion, is included externally as

$$V_{RM} x(t) = V_{RM} \cos mw_{Rt}$$

where m is used to designate the dominating harmonic.

The undesired portion of the error signal should be small enough for good spectral purity. Because, they narrow band frequency modulate (NBFM) the nominal output frequency, fo, to produce sidebands at the multiples

of the reference frequency, in the vicinity of fo. (see figure B-1.1)

$$V_{RM}$$

cos  $mw_{Rt}$   $V_{CO}$   $V_{O}$  cos  $\{w_{O}t + \theta(t)\}$   $V_{O}$  = output peak amplitude of  $V_{CO}$ .  $\theta(t) = \beta_{m} \sin mw_{R} t$   $\beta_{M} = \frac{f_{d}}{mf_{R}}$  ;  $f_{C}d = K_{V}$ .  $V_{RM}$

a) VCO signal flow

$$v_{RM} \longrightarrow f_d$$

b) VCO model to the reference harmonics

$$\frac{\frac{V_{o}}{2} J_{-1}(\beta m)}{f_{o}} \xrightarrow{\frac{V_{o}}{2} J_{o}(\beta m)} \frac{V_{o}}{\frac{V_{o}}{2} J_{1}(\beta m)} \xrightarrow{f_{o}+mf_{R}} f$$

$$f_{o} = \frac{1}{2^{n} n!} X^{n}; X << 1$$

c) Single sided frequency spectrum.

Figure B-1.1.

The input voltage,  $V_{\text{RM}}$ , into the VCO, sets the frequency deviation,  $f_{\text{d}}$ , according to the formula

$$f_d = K_v \cdot V_{RM}$$

Considering only the first sideband (NBFM approximation) the sideband amplitude to the center frequency amplitude ratio (in dB usually) is a design parameter given by

m th reference harmonic first sideband amplitude

$$\frac{\text{(V}_{\text{O}}/2) \text{ J}_{1}(\beta m)}{\text{m th reference harmonic center frequency amplitude}} = \frac{(\text{V}_{\text{O}}/2) \text{ J}_{1}(\beta m)}{(\text{V}_{\text{O}}/2) \text{ J}_{1}(\beta m)} = \frac{1}{2} \cdot \frac{\beta m}{m f_{R}}$$

Ideally, for balanced mixer and exclusive -OR gate types of phase detectors, error signal has no component around the first harmonic of the reference frequency. |8,pp.106| The strongest component of the undesired portion of the error signal is concentrated around the second harmonic of the reference frequency. However, for D flip-flop type of phase detectors, the strongest component is concentrated around the first harmonic, and the maximum amplitude of this component,  $V_{R1}$ , is simply the Fourier extension fundamental coefficient

Phase frequency detector is also a D flip-flop type phase detector, having fast acquisition aiding logic and larger input phase range (-360° to + 360). |8|

of a square wave, when its duty cycle is  $\zeta = T_0/2$ , |8,pp.106|.

$$V_{R1} = (V_{DD} - V_{SS}) \left(\frac{2}{\pi}\right) \text{ volts}$$

where (VDD-VSS) is the peak to peak output swing of the phase detector.

Now, let's drive the transfer functions with respect to inputs,  $\mathbf{w}_R(s)$   $\mathbf{v}_{RM}.\mathbf{X}(s)$  and  $\mathbf{w}_n(s)$ .

Loop gain = GH(s) =

$$\frac{K_{\gamma}.K_{v}}{N.s}$$

$G_{LP}(s)$

Closed loop gain =

$$\frac{\text{forward gain}}{1 + \text{loop gain}} = \frac{1}{\text{feedback gain}} \cdot \frac{1 \text{oop gain}}{1 + \text{loop gain}} = \frac{1}{\text{H}_{i}(s)}$$

GH(s)

Closed loop gain to the reference frequency input:

1 + GH(s)

$$\frac{w_{O}(s)}{w_{R}(s)} = N. \left(\frac{GH(s)}{1 + GH(s)}\right)$$

Closed loop gain to the VCO noise:

$$\frac{w_0(s)}{w_n(s)} = \frac{1}{1 + GH(s)} = 1 - \frac{GH(s)}{1 + GH(s)}$$

Closed loop gain to the undesired portion of the error signal generated by the

phase detector:

$$\frac{w_{O}(s)}{X(s)} = V_{RM}. K_{V} G_{LP}(s). \frac{1}{1 + GH(s)} \stackrel{?}{=} V_{RM}. K_{V} G_{LP}(s)$$

$$= V_{RM}. \frac{N.s}{K_{V}} \cdot \frac{GH(s)}{1 + GH(s)}$$

The transfer function,  $\operatorname{CH}(s)/1 + \operatorname{GH}(s)$ , is the basic design parameter to be optimized, with respect to wide pull in and hold in range, fast setling time and narrow bardwidth. The second equation, which relates the output frequency to the VCO noise, is made as small as possible with a low noise oscillator and sufficient loop bandwidth, such that, the VCO noise (in the vicinity of  $f_0$ ) falls into the loop bandwidth. (See the equation above, when  $\operatorname{CH}(s)/[1 + \operatorname{CH}(s)] \cong 1$ ) The last equation informs us that, spectral purity is achived only with  $\operatorname{GLP}(s)$ , since, at the reference frequency harmonics of the error signal high pass behavior of the  $1/[1 + \operatorname{CH}(s)]$  term does not introduce any attenuation. However, those frequencies fall into the cut off band of the loop filter,  $\operatorname{CLP}(s)$ . Numerically, assuming  $[1 + \operatorname{CH}(jmw_R)] \cong 1$ , and employing a D flip-flop type of phase detector, we get the expression for the required sideband suppression as follows:

Using phasor representation:

we get

$$V_{R1}.cosw_R t$$

$V_{R1}$   $\underline{0^o}$ ;  $X(jw_R) = 1$   $\underline{0^o}$

$$|w_o(jw_R)| \stackrel{\triangle}{=} w_d = V_{R1}.K_v |G_{LP}(jw_R)| \text{ rad/sec}$$

But

$$\frac{\text{sideband amplitude}}{\text{center frequency amplitude}} = \frac{\beta_1}{2} = \frac{w_d}{2w_R}$$

is a given quantity. So we get the necessary condition required by the loop filter for a given sideband suppression,  $\beta 1/2$ , as

$$|G_{LP}(jw_R)| \le \frac{w_d}{v_{R1}.K_v} = \frac{2w_R. (^{\beta_1/2})}{(v_{DD}-v_{SS})(\frac{2}{\pi}-).K_v}$$

where  $V_{R1} = (V_{DD} - V_{SS})(\frac{2}{\pi})$  and  $w_d$  is the frequency deviation of NBFM, as both defined previously. It is clear that required attenuation of the filter increases proportionally to the VCO gain. For instance, voltage controlled crystal oscillator having a very low gain  $(K_{\mathbf{V}})$ , has also very pure output at the cost of small tuning range.

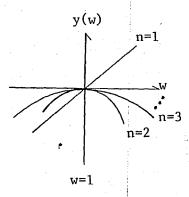

The type of the system is defined as the multiplicity of a pole at the origin, namely 'n' in the general expression of the loop gain function, given as

$$GH(s) = G_o. \frac{\prod_{k} (T_k \ s+1)}{s^n \prod_{i} (T_i \ s+1)}$$

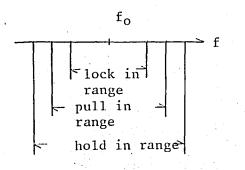

Also, the order of the system is defined as the highest power in the denominator of GH(s). Type-1 systems have been extensively analyzed in the past, and it is shown that |8|, the lock in range, pull in range and hold in range

Suppose, the loop VCO is mistuned (for example, in the absence of reference signal) prior to locking operation. The loop may skip many cycles, then ceases cycle skipping and pulls into lock, if the VCO mistuning frequency remains in the pull in (also called the frequency acquisition) range. Otherwise, if the VCO mistuning frequency is beyond the pull in range, the loop may skip cycles indefinitelly. However, if the VCO mistuning frequency remains in the lock in (also called seize frequency) range, the loop pulls into lock exponentially, without any cycle skipping |8|

In the definitions above, 'may' is used to indicate the worst case conditions of the initial phase. all depend proportionally on the velocity constant, Ky where

$$K_V = \lim s.GH(s)$$

$s \rightarrow 0$

Hence, all these 3 quantities must also be included in the PLL design, since  $K_{\rm V}$  assumes a finite value for type-1 systems. Since for type-2 or higher order system, the velocity constant becomes infinite, these 3 quantities also become infinite (actually they are limited by the unsymmetry of the phase detector, offset voltage of the phase detector and active components in the loop, tuning range of VCO, etc), so, they need not be considered in the PLL design.

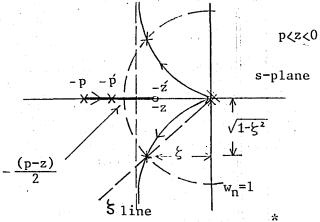

The type-2 third order organization is the most used one. However, if the reference frequency is close to the loop bandwidth, then extra atenuation is supplied by another pole, when type-2 fourth order organization is employed. The type-2 second order system however, has no reference filtering at all, but simple and extensively analyzed. Now we will give the normalized root locus plots and brief analysis of the most commonly used PLL systems; third order and fourth order type-2 systems.

The closed loop transfer function involves a second order factor, of the form  $w_n^2/(s^2+2\xi w_n s+w_n^2)$ , which, by the design, dominates over the system behavior, hence sets approximately the loop bandwidth, setting time and damping coefficient. So, the transfer functions are normalized with respect to the  $w_n$ , to simplify the design

Third order type-2 system:

Loop gain, GH(s), and  $\frac{GH(s)}{1 + GH(s)} = G_f(s)$  are defined as

$$GH(s) = K \frac{(s + z)}{s^2(s + p)}$$

$$G_f(s) = \frac{GH(s)}{1 + GH(s)} = \frac{\cancel{K}}{(s^2 + 2\xi s + 1)(s + \cancel{p})}$$

where primed symbols denote the closed loop parameters. If we choose p' and z' very close to each other, their individual effects, on the closed loop transfer function,  $G_f(s)$ , cancel out, and closed loop system behaves like a second order system having a transfer function

$$G_f(s) = \frac{K}{(s^2 + 2\zeta s + 1)}$$

So, in this case, loop behavior is readly found from the well known theory of the second order systems, and the problem turns out to be the determination of the value of the open loop parameters from a given closed loop transfer function. We can find the values of the open loop parameters,

simply, by the coefficient matching technique and can get one design algorithm as follows

- 1. Choose (p'/z') ratio. By design, closed loop (p') and zero (z') are made as close as possible, such as : (p'/z') = 102

- 2. Choose any two of undamped natural frequency  $(w_n)$ , damping factor  $(\xi)$  or settling time  $(t_s)$ .

- 3. Find the third parameter from the equation :

$$w_n \cdot t_s \cdot s = \begin{cases} 4 & \text{for } \% \text{ 2 final value error} \\ 3 & \text{for } \% \text{ 5 final value error} \end{cases}$$

4. Use the equations below, to find the values of the open loop paremeters (p,z,K)

a).

$$K = K' = (p'/z')$$

b).

$$p' = \frac{K'-1}{2\xi}$$

c).

$$z = z' = (p'/K')$$

d).

$$p = 2\xi + p'$$

5. Denormalize the open loop transfer function with respect to  $w_n$ . (This step may be skipped to obtain the normalized system design.)

GH(s) = K.

$$\frac{(s/w_n + z)}{(s/w_n)^2(s/w_n+p)}$$

$$\longrightarrow K \longrightarrow K. w_n^2$$

$$z \longrightarrow z. w_n$$

$p \rightarrow p. w_n$

6. Realize the system, where  $GH(s) = \frac{K_{\psi} . K_{v}}{N.s}$ . GLp(s) as given

previously. A proper loop filter can be given as

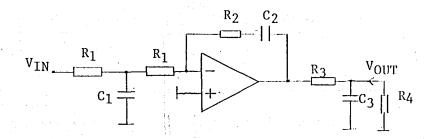

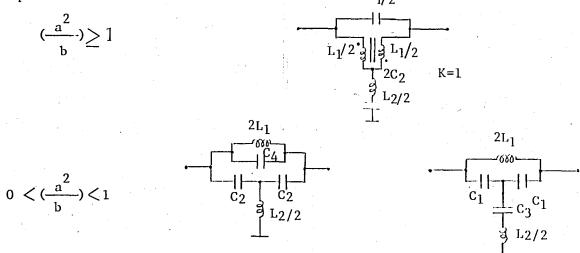

$$G_{LP}(s) = -\frac{1}{2R_{1}C_{2}} \cdot \frac{(1 + s/w_{2})}{s(1 + s/w_{1})}$$

$$w_{1} = \frac{2}{R_{1}C_{1}}$$

$$w_{2} = \frac{1}{R_{2}C_{2}}$$

$$V_{1N} = \frac{R_{1}}{R_{1}} \cdot \frac{R_{1}}{R_{1}} \cdot \frac{R_{2}}{R_{1}} \cdot \frac{C_{2}}{R_{1}C_{1}}$$

$$G_{LP}(s) = \frac{V_{OUT}(s)}{V_{1N}(s)}$$

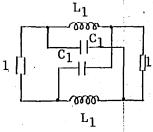

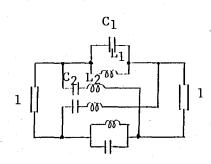

Fourth order type-2 system. 60°  $-\frac{(b+c-a)}{3}$ & line

Loop gain, GH(s), and  $\frac{GH(s)}{1 + GH(s)} = G_f(s)$  are defined as

GII(s) = K.

$$\frac{(s + a)}{s^2(s+b)(s+c)}$$

$$G_f(s) = \frac{GH(s)}{1 + GH(s)} = K' \frac{(s+a')}{(s^2+2\xi s+1)(s+b')(s+c')}$$

where primed symbols denote the closed loop parameters. By choosing the closed loop zero (a') and the closed loop pole (b') (see root locus plot) very close to each other, their individual effects, on the closed loop transfer function, cancel out. So, closed loop system behaves like to third order system, having transfer function:

$$G_f(s) = K' \cdot \frac{1}{(s^2 + 2 (s+1) (s+c))}$$

The operation of this system is usually optimized with respect to the rejection of the reference harmonics, generated by phase the detector, and in this case, one design algorithm is given as follows.

1. Choose  $w_n$ ,  $\zeta$  , closed loop pole (ć) and (b/a) ratio.

By design (b'/a) ratio is made as close to unity as possible and c with can be choosen, such that, the closed loop transfer function,  $G_f(s)$ , performs a prescribed third order filter function. (Sometimes the value of c needs to corrected.)

2. Use equations below to find the values of the open loop parameters. (K, a,b,c.)

a).

$$K = K' = (b'/a') \cdot c'$$

b).

$$b' = \frac{k'-c'}{2\xi c'+1} = \frac{(b'/a')-1}{2\xi c'+1}$$

.c'

c).

$$a = a' = \frac{b'}{(b'/a')}$$

d).

$$b.c = 1 + b.c' + 2\xi(b+c)$$

$b+c = 2\xi + b+c'$

3. Denormalize the open loop transfer function with respect to  $w_n$ . (This step may be skipped to obtain the normalized system design).

GH(s) = K.

$$\frac{(s/w_n + a)}{(s/w_n)^2(s/w_n+b)(s/w_n+c)}$$

$$\Longrightarrow \qquad K \leftarrow K. \ w_n^3$$

$$a \leftarrow a. \ w_n$$

$$b \leftarrow b. \ w_n$$

$$c \leftarrow c \ w_n$$

4. Realize the system, where  $GH(s) = \frac{K_{\phi} \cdot K_{V}}{N.s} G_{J,P}(s)$  as given previously. Two proper loop filters are given as:

$$V_{1N}$$

$R_{1}$

$R_{1}$

$R_{1}$

$C_{3}$

$V_{OUT}$

$C_{1}$

$C_{1}$

$C_{2}$

$C_{3}$

$C_{3}$

$C_{4}$

$C_{5}$

$C_{1}$

$C_{1}$

$C_{1}$

$C_{2}$

$C_{3}$

$C_{4}$

$C_{5}$

$C_{5}$

$C_{1}$

$C_{1}$

$C_{2}$

$C_{3}$

$C_{2}$

$C_{3}$

$C_{4}$

$C_{5}$

$C_{5}$

$C_{7}$

$C_{1}$

$C_{1}$

$C_{2}$

$C_{3}$

$C_{2}$

$C_{3}$

$C_{4}$

$C_{5}$

$C_{5}$

$C_{5}$

$C_{7}$

$C_{1}$

$C_{1}$

$C_{2}$

$C_{3}$

$C_{4}$

$C_{5}$

$C_{5}$

$C_{5}$

$C_{7}$

$C_{1}$

$C_{1}$

$C_{2}$

$C_{3}$

$C_{2}$

$C_{3}$

$C_{4}$

$C_{5}$

$C_{5}$

$C_{5}$

$C_{5}$

$C_{7}$

$C_{1}$

$C_{1}$

$C_{2}$

$C_{3}$

$C_{2}$

$C_{3}$

$C_{4}$

$C_{5}$

$C$

$$w_1 = \frac{2}{R_1C_1}$$

$w_2 = \frac{1}{R_2C_2}$   $w_3 = \frac{1}{(C_2||C_3)R_2}$   $C_2||C_3 = \frac{C_2.C_3}{C_2+C_3}$

$$G_{LP}(s) = -\frac{1}{2R_1C_2} \cdot \frac{R_4}{R_3 + R_4} \cdot \frac{(1+s/w_2)}{s(1+s/w_1)(1+s/w_3)}$$

$$w_1 = \frac{2}{R_1 C_1}$$

;  $w_2 = \frac{1}{R_2 C_2}$ ;  $w_3 = \frac{1}{(R_3 || R_4) C_3} || R_4 = \frac{R_3 \cdot R_4}{R_3 + R_4}$

As a final step, one overall design algorithm can be given as follows

- 1). Start with closed loop parameters

- 2). Determine the values of the open loop parameters

- 3). Find phase and gain margins

- 4). Find the loop filter transfer function

- 5.) Check if the sideband to carrier suppression is satisfied.

If any of the above conditions fails, then