# APPLICATION MAPPING AND OPTIMIZATION FOR CMP BASED ARCHITECTURES

## by

## Betül Demiröz

B.S., Computer Engineering, Marmara University, 2002M.S., Computer Engineering, Marmara University, 2004

Submitted to the Institute for Graduate Studies in Science and Engineering in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Graduate Program in Computer Engineering Boğaziçi University 2011

## ACKNOWLEDGEMENTS

I would like to express my gratitude to my thesis supervisors Prof. Oğuz Tosun and Prof. Haluk Topçuoğlu for their support and guidance throughout my graduate study and completion of this thesis. I also want to thank Prof. Mahmut Kandemir (from Pennsylvania State University) for his feedback and support. I gratefully acknowledge Assoc. Prof. Can Özturan, Assoc. Prof. Arda Yurdakul and Assist. Prof. Esin Onbaşıoğlu for their participation to my thesis jury, their useful comments and feedback.

I gratefully acknowledge the financial support of The Scientific and Technological Research Council of Turkey (TUBITAK) with a research grant (Project Number: 108E035). Additionally a partial fund is provided by Bogazici University Research Fund -08HA101D. I also want to acknowledge Georgia Institute of Technology, its Sony-Toshiba-IBM Center of Competence, and the National Science Foundation, for the use of Cell Broadband Engine resources that have contributed to this thesis.

I want to thank my dear friends Fatma Ergin, Sanem Arslan, Işıl Öz and Berna Kiraz for their friendship and support over the years. Finally I want to thank my parents Fehamet and Şenol, my brother Dündar and my dear husband İsmail for their encouragement, patience and support.

### ABSTRACT

# APPLICATION MAPPING AND OPTIMIZATION FOR CMP BASED ARCHITECTURES

Chip Multiprocessors (CMPs) are becoming standard and primary building blocks for personal computers as well as large scale parallel machines, including supercomputers. In this thesis, our main focus is on performance-aware mapping and optimization of application threads onto multicore architectures. Specifically, we propose three different approaches, which are data-to-core mapping methodology, threadto-core mapping methodology, and cache-centric data assignment methodology that includes data-to-thread mapping. For demonstrating data-to-core mapping methodology, we propose two novel parallel formulations for the Barnes-Hut method on the Cell Broadband Engine architecture by considering technical specifications and limitations of the Cell architecture. Our experimental evaluation indicates that the Barnes-Hut method performs much faster on the Cell architecture compared to the reference architecture, an Intel Xeon based system. To present thread-to-core mapping methodology, we propose a framework that uses helper threads running in parallel with application threads, which dynamically observe the behavior of application threads and their data access patterns. These helper threads calculate data sharing among application threads, cluster them to be mapped to available cores, use cache counters to calculate the efficiency of a mapping, and make the mapping decision after considering the execution needs. Our final methodology provides a locality-aware mapping algorithm, which targets to assign computations with similar data access patterns of an application to the same core. Our algorithm divides computations of the application into chunks to provide load balancing, and a set of chunks with high similarity is grouped into bins to provide data locality. We consider the sparse matrix-vector multiplication as the reference application.

## ÖZET

## YONGADA ÇOKLU-İŞLEMCİLİ MİMARİLER İÇİN UYGULAMA HARİTALAMASI VE ENİYİLEME

Yongada Çoklu-İşlemciler (CMP), kişisel bilgisayarların yanı sıra büyük ölçekli paralel makinaların ve süper bilgisayarların standart ve temel yapıtaşlarını oluşturmaya başlamıştır. Bu tezdeki temel amacımız, performansı arttıran haritalama ve optimizasyon yöntemleri geliştirerek, uygulama izleklerini çok çekirdekli mimarilere atamaktır. Bunu başarabilmek için üç farklı yöntem sunmaktayız, bunlar veri-çekirdek eşleme metodu, izlek-çekirdek eşleme metodu ve önbellek merkezli veri-izlek eşleme metodudur. Veri-çekirdek eşleme metodunda, Barnes-Hut algoritmasının bir CMP olan Cell Broadband Engine Mimarisinin teknik özelliklerini ve limitlerini göz önünde bulunduran iki özgün paralel formulasyonunu önermekteyiz. Yapılan deneysel değerlendirme, Barnes-Hut metodunun Cell mimarisi üzerindeki performansının karşılaştırma yapılan referans mimarisi olan Intel Xeon tabanlı sisteme göre belirgin oranda daha hızlı olduğunu göstermektedir. Izlek-çekirdek eşleme metodunu sunmak için, uygulama izlekleri ile paralel çalışan yardımcı izlekler kullanan ve dinamik olarak uygulama izleklerinin davranışlarını ve eriştikleri veri düzenini gözlemleyen bir sistem önerilmiştir. Yardımcı izlekler uygulama izleklerinin veri paylaşım miktarını hesaplayarak, bunları çekirdeklere eşlenmeleri için gruplara ayırır, eşlemelerin verimliliğini hesaplayabilmek için ön bellek sayaçları kullanır, ve çalışma zamanı ihtiyaçlarına bağlı olarak eşleme kararını alır. Önerilmiş olan son metodumuzda, benzer veri erişim şekline sahip olan hesaplamaları aynı çekirdeğe atamayı hedefleyen, veri yerelliğini sağlayan bir eşleme algoritması tasarlanmıştır. Onerilen algoritma verilen uygulamanın hesaplamalarını yükün eşit dağılımını sağlayabilmek için parçalara ayırır ve veri yerelliliğini sağlamak için yüksek benzerliğe sahip olan parçalar gruplandırılırlar. Metodun performansını ölçmek için, referans uygulama olarak seyrek matris-vektör çarpımı kullanılmıştır.

## TABLE OF CONTENTS

| A(  | CKNC | )WLED   | GEMEN'      | $\Gamma S$                                    | iii |

|-----|------|---------|-------------|-----------------------------------------------|-----|

| AF  | BSTR | ACT     |             |                                               | iv  |

| ÖZ  | ZET  |         |             |                                               | v   |

| LIS | ST O | F FIGU  | JRES        |                                               | ix  |

| LIS | ST O | F TAB   | LES         |                                               | xiv |

| LIS | ST O | F SYM   | BOLS        |                                               | xv  |

| LIS | ST O | F ACR   | ONYMS/      | ABBREVIATIONS                                 | xvi |

| 1.  | INT  | RODU    | CTION .     |                                               | 1   |

|     | 1.1. | Resear  | ch Objec    | tives and Contributions                       | 2   |

|     | 1.2. | Outlin  | e of the T  | Chesis                                        | 5   |

| 2.  | SUR  | VEY C   | N APPL      | ICATION MAPPING AND SCHEDULING FOR MUL-       |     |

|     | TIC  | ORE A   | RCHITE      | CTURES                                        | 6   |

|     | 2.1. | Overvi  | iew of Mu   | lticore Architectures                         | 6   |

|     | 2.2. | Applie  | ation Ma    | pping and Scheduling                          | 11  |

| 3.  | DAT  | A-TO-   | CORE AS     | SSIGNMENT METHODOLOGY: A DEMONSTRATION        |     |

|     | ON   | IBM Cl  | ELL ARC     | HITECTURE                                     | 14  |

|     | 3.1. | N-bod   | y Problen   | n and Barnes-Hut Method                       | 15  |

|     | 3.2. | IBM (   | Cell Broad  | band Engine Architecture                      | 17  |

|     | 3.3. | Paralle | elization o | of Barnes-Hut Algorithm on the Cell Processor | 20  |

|     |      | 3.3.1.  | Initial P   | arallelization of the Barnes-Hut Method       | 23  |

|     |      |         | 3.3.1.1.    | Domain Decomposition                          | 23  |

|     |      |         | 3.3.1.2.    | Tree Construction and Force Calculation       | 23  |

|     |      |         | 3.3.1.3.    | Position and Velocity Updates                 | 26  |

|     |      | 3.3.2.  | Enhance     | d Parallelization of the Barnes-Hut Method    | 26  |

|     |      |         | 3.3.2.1.    | Global Tree Construction                      | 27  |

|     |      |         | 3.3.2.2.    | Tree Construction and Force Calculation       | 29  |

|     |      | 3.3.3.  | Experim     | ental Work and Analysis of Results            | 30  |

| 4.  | THE  | READ-T  | ΓO-CORE     | ASSIGNMENT METHODOLOGY: A DEMONSTRA-          |     |

| TIC    | ON ON GENERIC MULTICORE ARCHITECTURES                  | 39 |

|--------|--------------------------------------------------------|----|

| 4.1.   | Proposed Framework for Dynamic Thread-to-Core Mapping  | 39 |

|        | 4.1.1. Clustering Thread                               | 42 |

|        | 4.1.2. Cost and Benefit Analysis Thread                | 44 |

|        | 4.1.3. Counter Thread                                  | 46 |

|        | 4.1.4. Mapping Thread                                  | 48 |

| 4.2.   | Enhancements on Our Framework for Decreasing Overheads | 48 |

|        | 4.2.1. Overhead of Thread Migration                    | 48 |

|        | 4.2.2. Overhead of Helper Threads                      | 50 |

| 4.3.   | Setup and Experimental Evaluation                      | 51 |

|        | 4.3.1. Simulation Platform Simics                      | 51 |

|        | 4.3.2. Applications                                    | 52 |

| 4.4.   | Results and Discussion                                 | 53 |

|        | 4.4.1. Scalability Results                             | 54 |

|        | 4.4.2. Quantifying Overheads                           | 56 |

|        | 4.4.3. Performance of Helper Threads                   | 57 |

|        | 4.4.4. Sensitivity Analysis                            | 59 |

| 5. A C | ACHE-CENTRIC DATA ASSIGNMENT METHODOLOGY ON GENERIC    | 7  |

| MU     | LTICORE ARCHITECTURES                                  | 65 |

| 5.1.   | Proposed Algorithm for Locality-aware Dynamic Mapping  | 67 |

| 5.2.   | Setup and Experimental Evaluation                      | 74 |

| 5.3.   | Results and Discussion                                 | 75 |

|        | 5.3.1. Performance of Dynamic Locality-aware Mapping   | 78 |

|        | 5.3.2. Sensitivity Analysis                            | 81 |

| 6. CO  | NCLUSIONS AND FUTURE WORK                              | 85 |

| APPEN  | NDIX A: IBM CELL BROADBAND ENGINE                      | 88 |

| A.1.   | IBM Cell Broadband Engine Architecture                 | 88 |

|        | A.1.1. Power Processing Element                        | 88 |

|        | A.1.2. Synergistic Processor Elements                  | 89 |

|        | A.1.3. Element Interconnect Bus                        | 92 |

| A.2    | Application Development on IBM Cell Broadband Engine   | 92 |

## LIST OF FIGURES

| Figure 2.1. | Conventional microprocessor                                                                                                                                                                  | 8  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.2. | A simple chip multiprocessor                                                                                                                                                                 | 8  |

| Figure 2.3. | Shared-cache chip multiprocessors                                                                                                                                                            | 9  |

| Figure 2.4. | Multithreaded shared-cache chip multiprocessors                                                                                                                                              | 9  |

| Figure 3.1. | Sequential version of Barnes-Hut algorithm                                                                                                                                                   | 18 |

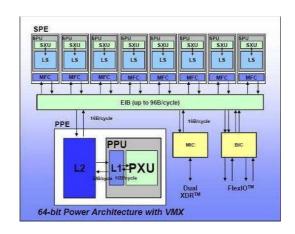

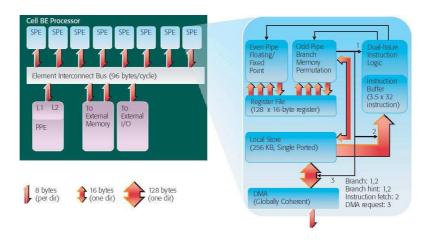

| Figure 3.2. | Cell Broadband Engine Architecture [37]                                                                                                                                                      | 19 |

| Figure 3.3. | View within PPE for the initial parallelization                                                                                                                                              | 21 |

| Figure 3.4. | View within SPE for the initial parallelization                                                                                                                                              | 22 |

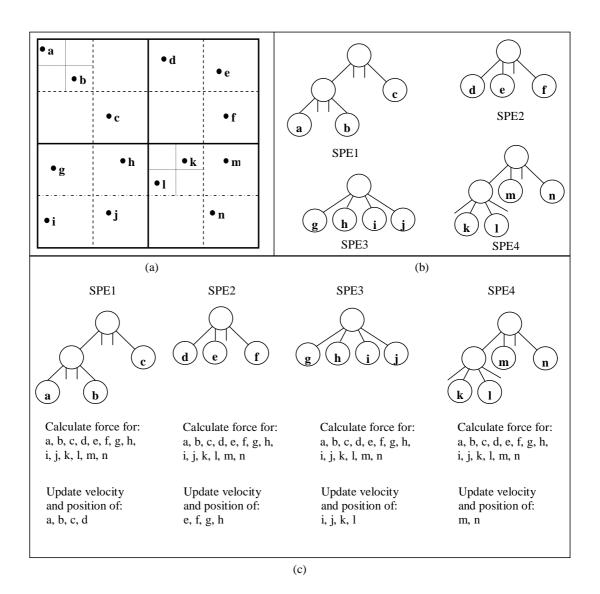

| Figure 3.5. | A typical step of the first parallel version with 14 particles using 4 SPEs. (a) Domain decomposition (b) Local tree construction in SPEs (c) Force calculation and position updates in SPEs | 25 |

| Figure 3.6. | View within PPE for the enhanced parallelization                                                                                                                                             | 27 |

| Figure 3.7. | View within SPE for the enhanced parallelization                                                                                                                                             | 28 |

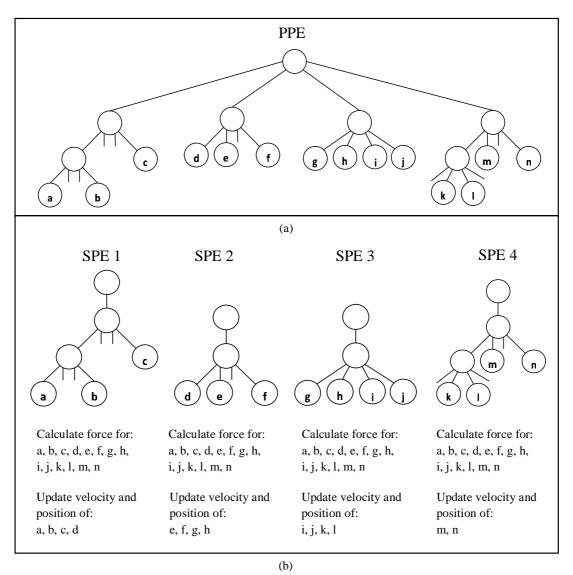

| Figure 3.8. | A typical step of the second parallel version with 14 particles using 4 SPEs. (a) Global tree construction (b) Local tree construction, force calculation and position updates in SPEs       | 30 |

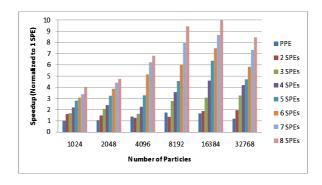

| Figure 3.9.  | Speedup with respect to different number of SPEs and PPE - initial parallelization                                                            | 31 |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.10. | Speedup with respect to different number of SPEs and PPE - enhanced parallelization                                                           | 32 |

| Figure 3.11. | Speedup of 8 SPEs relative to the Intel Xeon with respect to different number of particles                                                    | 33 |

| Figure 3.12. | Performance comparison with respect to number of particles given in the range [1024-4096]                                                     | 34 |

| Figure 3.13. | Performance comparison with respect to number of particles given in the range [8192-32768]                                                    | 34 |

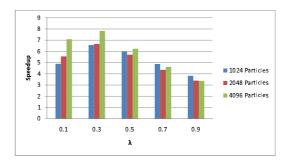

| Figure 3.14. | Speedup of 8 SPEs relative to the Intel Xeon with respect to different $\lambda$ values - initial parallelization                             | 36 |

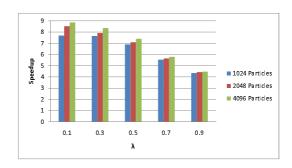

| Figure 3.15. | Speedup of 8 SPEs relative to the Intel Xeon with respect to different $\lambda$ values - enhanced parallelization                            | 38 |

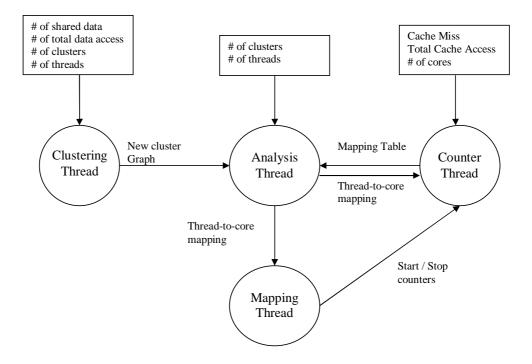

| Figure 4.1.  | The relationship among the four helper threads considered in our framework                                                                    | 41 |

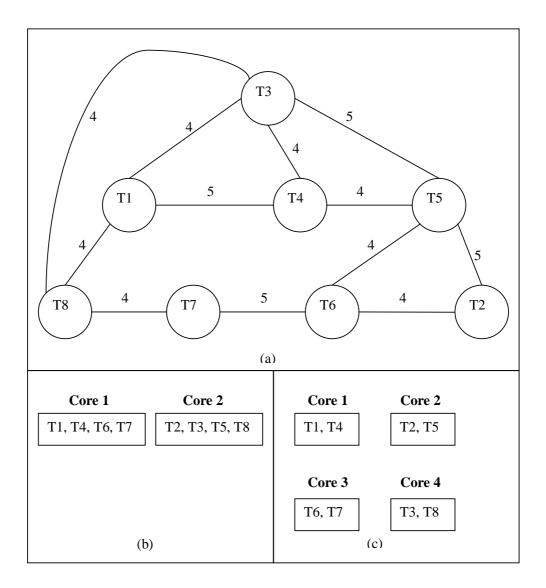

| Figure 4.2.  | An example thread sharing and thread mapping scenario. (a) Weight sharing graph (b) Thread mapping for 2 cores (c) Thread mapping for 4 cores | 43 |

| Figure 4.3.  | New mapping construction by the cost and benefit analysis thread.                                                                             | 45 |

| Figure 4.4.  | Inline assembly code for Solaris running on serengeti architecture.                                                                           | 47 |

| Figure 4.5.  | Gcc inline assembly code for Linux running on x86 Intel architecture.                                    | 47 |

|--------------|----------------------------------------------------------------------------------------------------------|----|

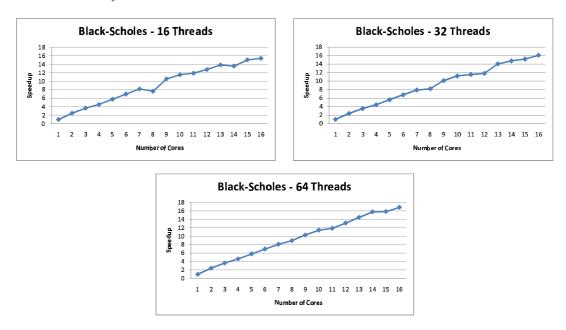

| Figure 4.6.  | Scalibility of Black-Scholes application with 16, 32 and 64 threads.                                     | 55 |

| Figure 4.7.  | Scalibility of Jacobian application with 16, 32 and 64 threads. $$                                       | 55 |

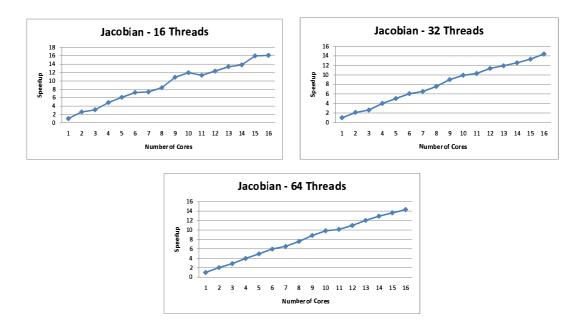

| Figure 4.8.  | Scalibility of SpMV application with 4 threads per core                                                  | 56 |

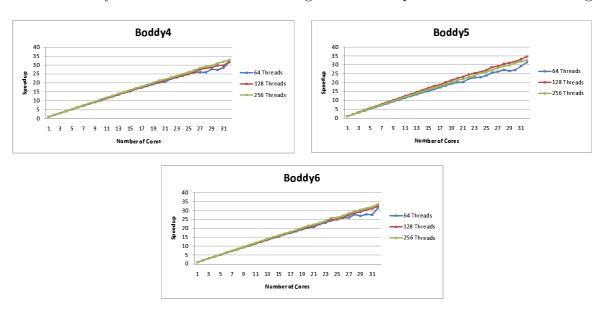

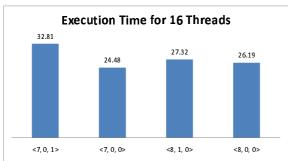

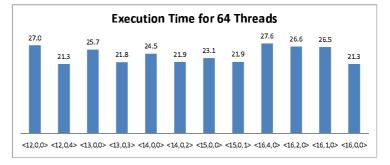

| Figure 4.9.  | Overhead of running helper threads with 64 application threads on 16 cores for SpMV application          | 57 |

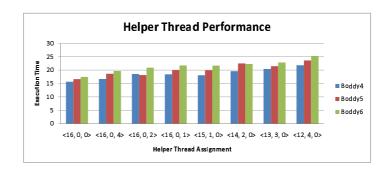

| Figure 4.10. | Performance of helper threads running with application threads on 8 Cores for Black-Scholes application  | 58 |

| Figure 4.11. | Performance of helper threads running with application threads on 16 cores for Black-Scholes application | 58 |

| Figure 4.12. | Performance of helper threads running with application threads for Jacobian Matrix Multiplication        | 59 |

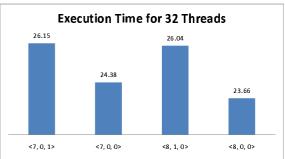

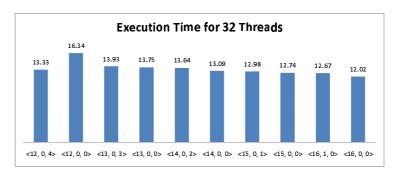

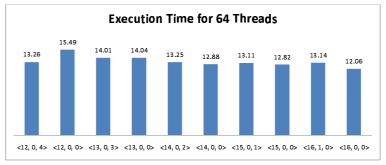

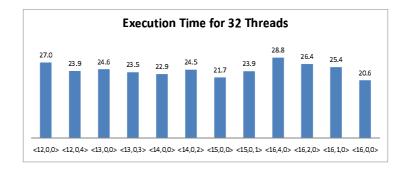

| Figure 4.13. | Performance of helper threads running with application threads for SpMV                                  | 60 |

| Figure 4.14. | Performance of enhanced helper threads running with application threads for SpMV                         | 60 |

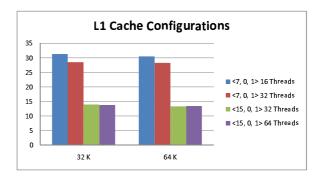

| Figure 4.15. | Performance of helper threads for different L1 cache configurations for Black-Scholes application        | 61 |

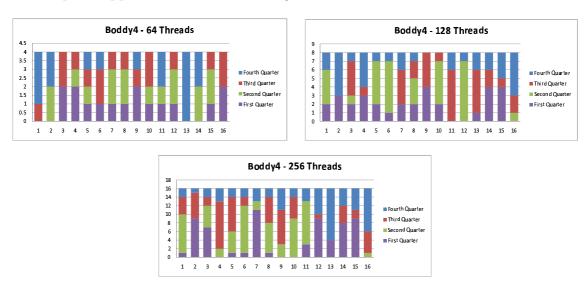

| Figure 4.16. | Load distribution among cores for 64, 128, 256 application threads on 16 cores for SpMV application      | 62 |

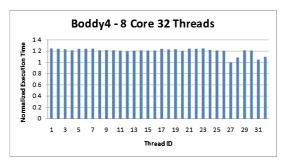

| Figure 4.17. | Normalized execution time of application threads on 8 cores for SpMV                                               | 63 |

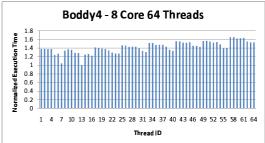

|--------------|--------------------------------------------------------------------------------------------------------------------|----|

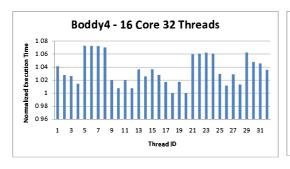

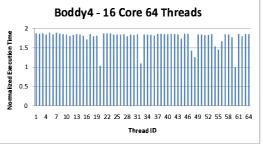

| Figure 4.18. | Normalized execution time of application threads on 16 cores for SpMV                                              | 63 |

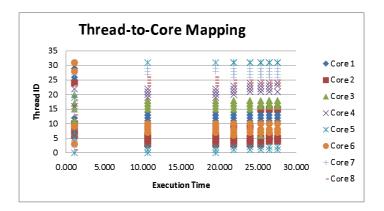

| Figure 4.19. | Dynamic distribution of 32 application threads to 8 cores for SpMV.                                                | 63 |

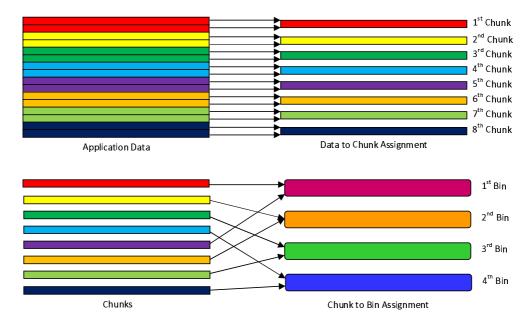

| Figure 5.1.  | The layout of our framework including chunk and bin representations.                                               | 68 |

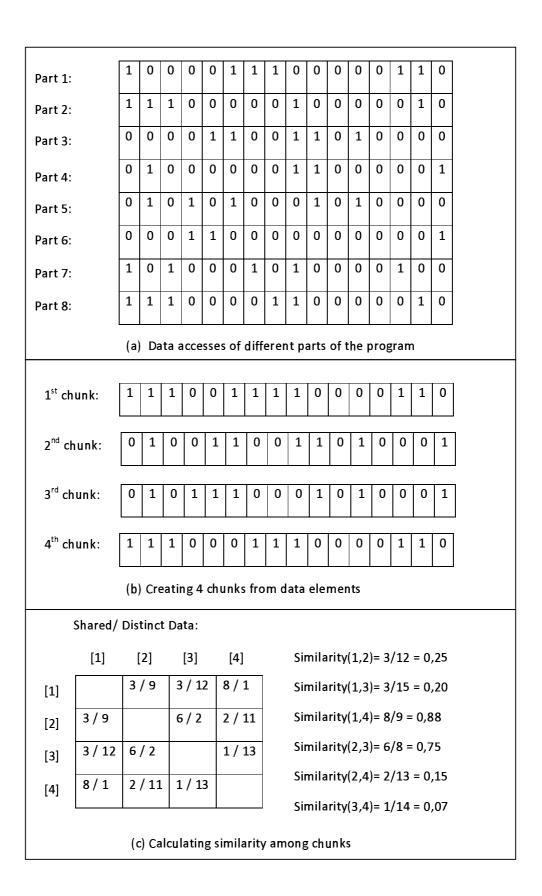

| Figure 5.2.  | The algorithm for calculating similarities among chunks                                                            | 69 |

| Figure 5.3.  | Chunk-to-bin assignment                                                                                            | 72 |

| Figure 5.4.  | Calculating similarity values for the case of 4 chunks with 2 bins                                                 | 73 |

| Figure 5.5.  | Sparse matrix-vector multiplication algorithm with CSR storage. $\boldsymbol{.}$                                   | 76 |

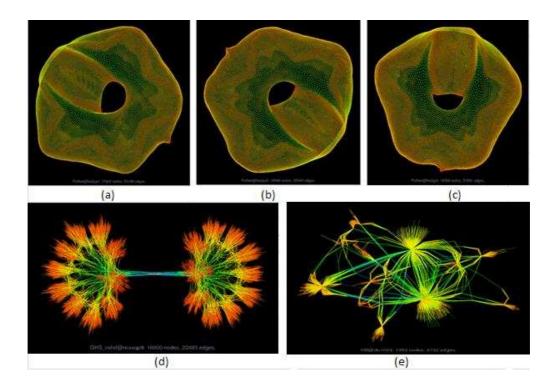

| Figure 5.6.  | The shapes of input matrices used by SpVM application [78] (a)Boddy4 (b)Boddy5, (c)Boddy6, (d)Ncvxqp9, (e)Illc1033 |    |

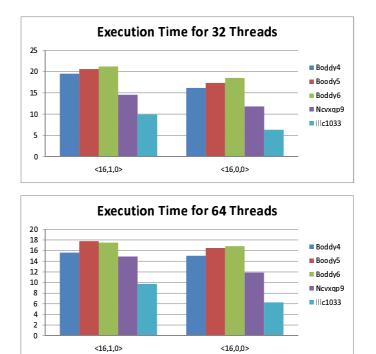

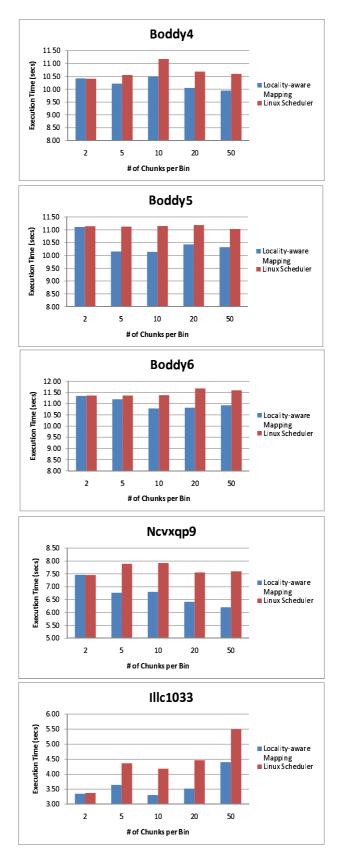

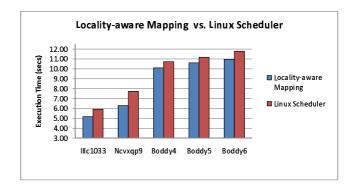

| Figure 5.7.  | Performance of locality-aware dynamic mapping method and Linux scheduler for various input files                   | 80 |

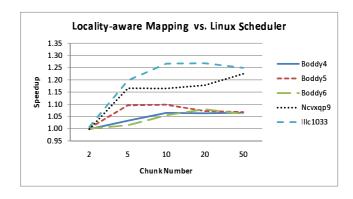

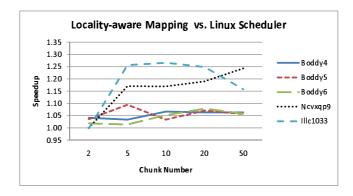

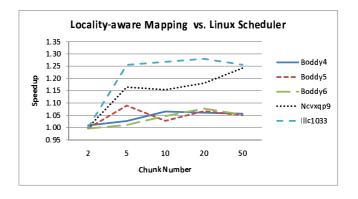

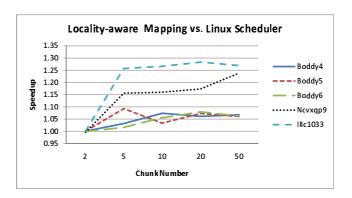

| Figure 5.8.  | Speedup values for different number of chunks                                                                      | 81 |

| Figure 5.9.  | Speedup values when 4K L1 cache / 16K L2 cache combination is considered                                           | 82 |

| Figure 5.10. | Speedup values when 16K L1 cache / 64K L2 cache combination is considered                                          | 82 |

| Figure 5.11. | Speedup values when 32K L1 cache / 128K L2 cache combination   |    |

|--------------|----------------------------------------------------------------|----|

|              | is considered                                                  | 83 |

| Figure 5.12. | Performance of locality-aware dynamic mapping method and Linux |    |

|              | scheduler when maximum number of chunks are considered         | 83 |

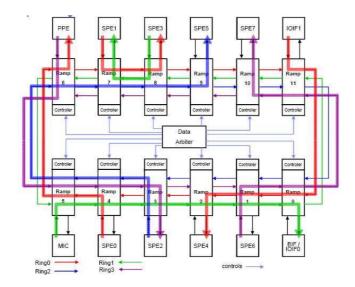

| Figure A.1.  | SPE block diagram [55]                                         | 89 |

| Figure A.2.  | SPE Architecture [55]                                          | 90 |

| Figure A.3.  | Internal structure of Cell B./E. [57]                          | 92 |

| Figure A.4.  | Example of eight concurrent data transfers [58]                | 93 |

## LIST OF TABLES

| Table 3.1. | Communication and computation times (in msecs.) for various                                                                                                  |    |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|            | phases of the enhanced parallelization of the Barnes-Hut method. $\boldsymbol{.}$                                                                            | 35 |

| Table 3.2. | Execution time (in seconds) of the enhanced parallelization of Barnes-Hut method with compiler optimization flags for different number of SPEs and particles | 37 |

| Table 4.1. | Simulation parameters for performing experiments                                                                                                             | 54 |

| Table 5.1. | Simulated architecture parameters of experimental study                                                                                                      | 75 |

| Table 5.2. | Input matrices of SpMV application                                                                                                                           | 77 |

| Table 5.3. | L1 and L2 cache counts (in millions) for Boddy5 and Illc1033 input matrices                                                                                  | 79 |

| Table 5.4. | L1 and L2 cache counts (in millions) for the case of maximum number of chunks                                                                                | 84 |

## LIST OF SYMBOLS

$access_i$  Total number of data accessed by  $thread_i$

$chunk_{ij}$  Bit vector representing data accessed by  $chunk_i$

$sharing_{i,j}$  Total number of shared data between  $thread_i$  and  $thread_j$

$W_{ij}$  Similarity weight of  $thread_i$  and  $thread_j$

$\delta$  Constant used in variation calculation of two mappings

$\Delta_{miss\ ratio}$  Miss ratio fraction of previous and current mapping

$\lambda$  Constant for MAC Criteria

## LIST OF ACRONYMS/ABBREVIATIONS

Cell/B.E. Cell Broadband Engine

CM Current Mapping

CMP Chip Multi-Processor

CPI Cycle Per InstructionCPU Central Processing Unit

CSR Compressed Sparse Row

DMA Direct Memory Access

DML Device Modeling Language

EIB Element Interconnect Bus

FFT Fast Fourier Transform

GPU Graphics Processing Unit

ILP Instruction Level Parallelism

IPC Instructions Per Cycle

LS Local Store

MAC Multipole Acceptance Criteria

MFC Memory Flow Control Unit

MM Main Memory

MRc Cache Miss Ratio of Current Mapping

MRp Cache Miss Ratio of Previous Mapping

New Mapping

NoC Network-on-Chip

PPE PowerPC Processing Element

SIMD Single Instruction Multiple Data

SPE Synergistic Processor Element

SpMV Sparse Matrix-Vector Multiplication

SPU Synergistic Control Unit

TLP Thread Level Parallelism

### 1. INTRODUCTION

As the chip manufacturing technology moves toward deep sub-micron ranges, transistors become smaller, and operating frequencies keep getting faster. As a result, chip components are becoming increasingly unreliable. An architectural response to these critical challenges is the emerging Chip Multiprocessors (CMPs). A CMP contains multiple Central processing units (CPUs), an interconnection fabric, and some memory components, all packaged into a single chip. Almost all major chip manufacturers in the world are now considering CMP design and optimization, and CMPs have become the standard and primary building blocks for personal computers as well as large-scale parallel machines, including supercomputers. Nowadays, there are dual core chips on the market from major manufactures (Intel Montecito [1] and AMD Athlon [2]). Complex configurations with higher number of cores have also been delivered or prototyped, including Sun UltraSPARC T1 (formerly Niagara) [3], IBM's Cell [4], and Intel's 80-core TeraFlop [6], RAW [7], TRIPS [8], WaveScalar [9], and SmartMemories [10] in academia.

The focus of this thesis is to explore ways to map and adapt the execution of an application to the underlying hardware in CMPs. The assignment of application threads onto cores and the data they manipulate onto memory components is a challenging task. One option is to use static assignment of data and application threads to CMPs and keep this assignment throughout the execution of the application. With this static mapping, we are not able to capture data access patterns of application threads that are dynamically changing.

The other option is to use dynamic mapping strategies that can detect changes in data access patterns of application threads throughout the execution and can adjust the application threads to adapt dynamic data sharing patterns. Dynamic mapping strategies can be useful if their overheads can be kept low.

### 1.1. Research Objectives and Contributions

Our goal is the efficient exploitation of emerging CMPs using application mapping and adaptation techniques. The aim of our approach is to reduce execution latencies. To achieve this, we have designed mechanisms that take full advantage of the resources, especially the memory components available in CMPs. Our proposed work is demonstrated first using the IBM Cell chip multiprocessor, and then generic multicore processors that are simulated using an enhanced version of SIMICS.

We started our work by studying various static application and data mapping strategies for CMPs. We then decided on the mechanisms to collect runtime information about the state of the architecture and the state of the application. Our approach has both "static" and "dynamic" components for application mapping and optimization, targeting CMP architectures. These approaches can be listed as thread-to-core mapping and data-to-thread mapping. In our first approach, static thread-to-core mapping and dynamic data-to-thread mapping are considered. The second approach involves static data-to-thread mapping and dynamic thread-to-core mapping. In our final approach, we consider a cache-centric mapping that includes dynamic data-to-thread mapping.

Our first approach has three phases: code parallelization, thread-to-core mapping, and data-to-memory mapping. In the first phase, the behavior of the application is analyzed in detail, and two parallel implementations that consider the characteristics of the application are proposed. Additionally, both the CMP characteristics and the unique features of the target HW are considered in the implementation. These features include vector operations (most of the computations are SIMDized) and memory access operations that are overlapped with computation by using double buffering. Branches are also eliminated by using select bits, loop unrolling, and nonrecursive implementation. The second step maps threads to the available CPUs. In this phase, the number of threads created is equal to the number of cores used. In the third step, data is mapped to on-chip memory components. In this step, we exploit the affinity

(data-computation relationship) as much as possible. Also, in this step, data is dynamically mapped to threads due to the size of the on-chip memory components and the dynamic nature of the application used.

In our second approach, we focus on the development of a framework that includes a dynamic thread-to-core assignment that aims to maximize data reuse of onchip memory components. Because we use CMPs as our target architecture, effective thread-to-core assignment at runtime requires several adjustments. First of all, not every piece of information that could be collected through counters is valuable, so the data is processed before we can make adaptation decisions based on it. Second, inexpensive but effective analysis and decision algorithms are designed and implemented. An important question here is how to structure the decision mechanism. Performing effective adaptation decisions also requires predicting the application's data access pattern. Third, fast activation of optimizations at runtime is important. Costly optimizations cannot be implemented, as their overhead can offset the potential benefits.

Major challenges that are investigated as part of our second approach include the following: (i) given the runtime execution constraints and application characteristics, deciding what type of statistics we need to collect (statically and dynamically), (ii) determining mechanisms for collecting dynamic statistics during execution, and (iii) selecting the set of optimizations to apply. Our approach employs four helper threads to adapt the application execution to continuously changing runtime conditions. Dynamic mapping is triggered as a reaction to an interesting execution pattern, which presents opportunities for optimization. The goal of our framework is to eliminate performance bottlenecks of the given application by increasing the data reusability of on-chip memory components.

In our framework, four helper threads that run parallel with the application threads are used to achieve our goals. The responsibilities of the helper threads are the following:

- The clustering thread collects the data access pattern of all application threads and calculates their data sharing. This thread constructs clusters of application threads which have highest data sharing. These clusters are then assigned to cores to maximize data reuse of on-chip memory components.

- The counter thread makes use of performance counters and calculates the overall miss ratio of a specific interval. This helper thread uses the total hit and miss number of data read and write of on-chip memory components of all cores used.

- The cost and benefit analysis thread decides whether dynamic thread mapping is necessary, and if it is, this thread generates the next formation of threads. While making this decision, it predicts the behavior of the application in the near future based on the previous information collected through other helper threads. The metrics used in the decision process are the application threads' data sharing pattern, past execution history, and current counter data. The cost and benefit analysis thread is the main decision mechanism of the framework, so it coordinates all other helper threads.

- The mapping thread obtains the mapping decision from the cost and benefit

analysis thread and uses this information to dynamically migrate threads among

cores.

In our final approach, our aim is to obtain a general view of different parts of the application by using a locality analysis, which provides details of the cache requirements and data access patterns of application threads. In this work, our objective is to increase the probability of data reuse of on-chip memory components by assigning computations with similar data access patterns to same cores. It is built on a hierarchically data-to-thread and thread-to-core assignment methodology, which includes similarity calculation, data-to-bin, bin-to-thread, and thread-to-core assignment phases.

In similarity calculation, the input data is divided into smaller computations, and these computations are processed to find the total number of shared and distinct elements that will be used by application threads. Then data elements are clustered according to the highest data similarity into bins, which are dynamically assigned to threads. Similarity calculation and data-to-bin phases are completed before the execution of the application threads starts. As soon as threads begin their execution, bins are assigned to threads. This work improves the performance of the application by balancing the load among threads and increasing the cache reuse of on-chip memory components shared by application threads. To achieve load balance, data in bins are mapped to threads dynamically. We increase cache reuse by assigning the bins with maximum similarity to threads sharing the same on-chip memory component.

#### 1.2. Outline of the Thesis

Chapter 2 provides a brief background of application scheduling and mapping for multicore architectures. This chapter also surveys various scheduling algorithms on parallel and distributed systems. Chapter 3 presents and evaluates our data-to-core assignment methodology. This chapter describes the N-Body problem and the Barnes-Hut Method, which is used as the base application for experimental evaluation. It also gives the details of the Cell Broadband Engine Architecture. Chapter 4 presents a novel thread-to-core mapping framework that considers four helper threads. It also discusses the methods used for cache optimization and gives details on three benchmarks used, namely the Black-Scholes application, Jacobian Matrix Calculation, and Sparse Matrix-Vector Multiplication. Chapter 5 focuses on a cache-centric data assignment methodology based on a locality analysis of data computations of applications. Finally Chapter 6 summarizes the contributions of the application mapping approaches proposed in this thesis.

# 2. SURVEY ON APPLICATION MAPPING AND SCHEDULING FOR MULTICORE ARCHITECTURES

In this chapter, we first give a brief overview of multicore architectures. This is followed by a survey on application mapping and optimization on CMP architectures.

#### 2.1. Overview of Multicore Architectures

The performance of microprocessors has increased exponentially for two main reasons: the increased number of transistors available and increased parallelism exploited in software. The growing number of transistors has also increased the amount of power used. The processor designs should utilize the number of transistors available to enhance performance by minimizing design complexity and power usage.

By using the same number of transistors, we can obtain either a single high-performance processor running a single, high-performance thread or a group of simpler cores running multiple threads in parallel. If the same budget is used, multi-cores obtain higher performance compared to a monolithic processor; in addition, multi-core designs are simpler, and design and verification costs are lower. As a result, the new processor designs target CMPs.

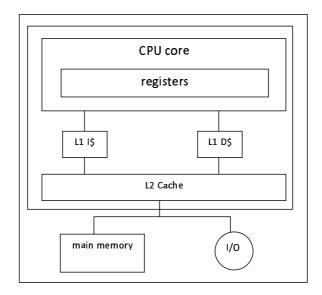

Individual CPUs in a CMP architecture can be simpler than a single CPU-based system and can thus operate with lower frequencies and less aggressive supply voltages (as we have multiples of them), thereby helping with both the power and the reliability problem. Single-processor systems as shown in Figure 2.1 faced some major difficulties in further increasing processor performance, and CMPs overcome these problems [11]. These difficulties can be listed as follows:

• Memory Stall Latency: The speed of processor is increasing faster than the main memory (MM), and while data or instructions are fetched from memory, the

CPU waits for the memory operation to finish; as a result, memory stall latency determines a major part of total execution time. Previous designs proposed two solutions to solve this problem: larger caches and exploitation of instruction level parallelism (ILP). CMPs solve this problem by using thread level parallelism (TLP). While one thread uses the CPU, the other fetches data or instructions from memory, and for the entire core to be idle would mean that all threads have overlapping memory stalls, which has a very low possibility.

- Branch Prediction: Long pipelines are used in single-core systems, and when a branch miss-prediction occurs, the entire instruction is replaced with a new one, so it has a high penalty. CMPs support one pipeline in each core shared by multiple threads, so when a branch miss-prediction occurs during the execution of a thread, another thread uses the pipeline; meanwhile, the other thread fetches the new instruction from memory.

- Power Consumption: Power consumption increases exponentially as more transistors are used in core designs. CMP systems can yield the same performance by decreasing the amount of power used. Individual CPUs in a CMP architecture can be simpler than a single CPU-based system and thus can be operated with low frequencies and supply voltages, thereby helping with the power problem.

- Die Size: CMP cores are simple and small, and adding a new core to the current architecture results in minor increases in die size.

- Complexity: CMP cores are easy to design and verify, whereas single-core CPUs are much more complex and difficult to design.

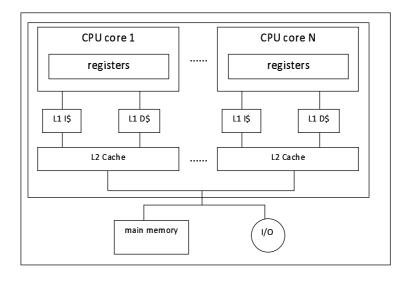

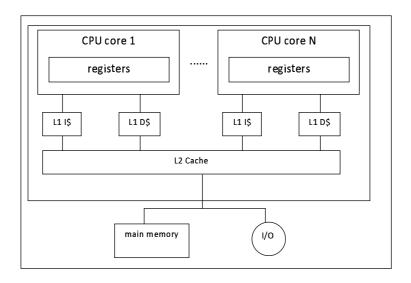

There are different ways of implementing CMPs, but all CMPs contain multiple CPUs, an interconnection fabric, and some memory components, all packaged into a single chip. CMP implementation can vary according to shared components in the chip [12]. Some CMPs share only the system interface between cores as in Figure 2.2, so each core has its own L1 and L2 cache; while others (an example architecture is shown in Figure 2.3) may share an on-chip cache.

Figure 2.1. Conventional microprocessor.

Figure 2.2. A simple chip multiprocessor.

Figure 2.3. Shared-cache chip multiprocessors.

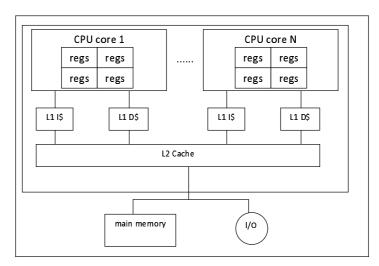

To distribute threads over the cores less in number then the cores, each core should support the execution of multiple threads, simultaneously. The CMP configuration in Figure 2.4 employs cores with multiple register files to provide simultaneous multithreading.

Figure 2.4. Multithreaded shared-cache chip multiprocessors.

The cores used in CMP architecture can be homogeneous or heterogeneous. Homogeneous CMPs are simple and easy to design, the same core is replicated several times, but heterogeneous CMPs contain high and low complexity cores. The size and strength of a replicated core varies according to application needs. Server applications focus on throughput per cost and power, so using many small low-power cores is attractive. In case applications require high performance, few large size cores may be preferred.

In reality, application's execution time requirements are not easily characterized; an application may have different phases (phases that can be executed on a simple core and phases that require a high-performance core), so different applications have different requirements, and these requirements may vary over time. Another core replication alternative is to use both high-performance and low-performance cores together to map application needs. Heterogeneous CMPs [13] may match the processor and system resources to each application's need efficiently. They may improve system throughput and reduce processor power. Heterogeneous CMPs may outperform homogeneous CMPs if a heterogeneous CMP can map each application to the core best suited to its performance demands and if it can answer to different workload demands, ranging from low TLP to high TLP.

Kumar et al. proposed a CMP architecture [14] that reduces processor power dissipation by using heterogeneous cores and mapping a given application to the most appropriate core to meet performance and power requirements. In this study, dynamic switch between cores is allowed, and the core selection depends on two metrics for power minimization: energy metric and energy-delay metric. In energy metric, the core that has the lowest energy consumption is chosen with the constraint that the performance should be within 10% of the fastest core in the chip. But for energy-delay metric, energy and response time have equal importance. Another study [15] examines policies for heterogeneous CMP architectures with and without multithreading cores.

In an efficient CMP design, the die size area and computational efficiency are two important factors. If topologically feasible resources can be shared, then the die area can be reduced, and overall computational efficiency can be improved as described in Kumar et al.'s study [16]. This work investigates the possible sharing of floating-point

units, crossbar parts, instruction caches, and data caches between adjacent pairs of processors. The sharing of resources results in area savings if the resources shared are large enough that additional wiring overhead does not outweigh the area benefits.

### 2.2. Application Mapping and Scheduling

Efficient task scheduling and mapping is critical for achieving high performance in heterogeneous parallel and distributed systems. This problem has been shown to be NP-complete in general cases as well as in several restricted cases. Due to its key importance, the scheduling and mapping problem has been extensively studied, and various algorithms have been proposed in the literature. On the other hand, thread-level granularity is important for emerging architectures, including multicore systems, and efficient thread-to-core mapping mechanisms are crucial to improve the performance of multithreaded applications in multicore systems.

There are many scheduling algorithms for parallel and distributed systems in literature, and these algorithms are divided into two groups according to when scheduling action will be taken. In static scheduling, decision and mapping of tasks to processors is taken at compile time, whereas in dynamic scheduling, this decision is taken at runtime. Both static and dynamic assignment techniques will be considered in this work. Mapping of the algorithms in the literature directly, as they are to the CMP architecture is not suitable, because the communication cost in CMPs is much lower than that of conventional systems. Therefore, new scheduling algorithms considering CMP characteristics are proposed in the thesis.

Static scheduling techniques do not consider the runtime behavior of threads that vary throughout execution [17] and [18], so it is beneficial to use dynamic thread assignment techniques. Becchi et al. calculates the instructions per cycle (IPC) values on heterogeneous cores for each thread and uses the ratio of the IPC values to assign the application threads to cores at runtime [19].

Additionally, to efficiently utilize the underlying systems, it is important to observe the runtime behaviors of the running threads and to provide a dynamic thread-to-core mapping by exploiting thread migration between the cores. In Anderson et al.'s study [20] and Sondag et al.'s study [21], instead of using an applications execution trace, the similarity between programs' phases are used to make the thread assignment decision. This work contains two phases; the first phase uses a static analysis technique to group similar sections in a program, and the second phase deals with scheduling. Another dynamic scheduling method is given in Tam et al.'s study [22], which clusters the application threads that share the same cache access pattern to the same core. Cache access patterns are collected with performance monitoring units and are stored in a summary vector called shMap; and the similarity among threads' access patterns are measured using a similarity metric. If the similarity between two shMap vectors is greater than a given threshold, these two threads are assigned to the same cluster. After clusters are formed, each cluster is assigned to a core.

Process variation aware thread mapping algorithm is proposed in Hong et al.'s study [23]. This work focuses in the latency variations of identical processor cores and proposes a dynamic thread remapping algorithm which allows all processors to operate at their individual peak frequency. This algorithm has two phases, detection phase and stable phase. In detection phase the variations of execution latencies between application threads are detected. Based on the variations encountered, the application threads are remapped. As long as the variations of execution latencies stay the same, the algorithm remains in the stable phase. These two phases are repeated as long as the execution of the application continues. There are other studies that considers the effect of process variation on performance [24, 25].

For efficient use of heterogeneous multicore systems, runtime systems such as StarPU [26] are also developed. StarPU distributes parallel tasks to heterogeneous multicore architectures, and it provides an execution model that uses scheduling strategies to balance load and improve data locality among tasks.

Machine learning based approaches are also used for predicting the best thread-to-core mapping. A compiler based approach that maps a parallel program to a multi-core processor by predicting the number of threads and the scheduling policy, is proposed in Wang et al.'s study [27].

Data and computation mapping for multiprocessors are also widely studied. These algorithms propose data partitioning approaches applicable to a given multicore architecture. In Balasundaram et al.'s study [28] data partitioning decisions are guided with a static performance estimator. Static and dynamic algorithms to partition the on-chip memory components are proposed in Kim et al.'s study [29]. Dynamic thread and data mapping approaches on CMP-based network-on-chip (NOC) architectures are also presented. One of these works [30] aims to reduce the distance between the location of the requested data and the core whose local memory contains it. In this study, a helper thread is used to make the thread-to-core assignment.

Cache performance is an important issue regarding the performance of CMPs and shared cache contention degrades performance of the application, so studies including cache behavior of the application parts have been introduced. One of these works introduces a locality model [31] which predicts the behavior of jobs and schedules them accordingly by using concurrent reuse distance [32]. To improve the management of the L2 Cache, CASC [33] schedules threads with low L2 miss rate and gives priority to threads that has low L2 space requirements.

Chen et al.'s study [34] analyze the performance of different thread schedulers to increase the hit ratio of off-chip memory components. In Chandra et al.'s study [35] several performance models are proposed to predict the effect of L2 cache sharing with multiprogram workloads. Pichel et al. [36] proposed a technique for increasing the locality of sparse matrix-vector multiplication (SpMV) application on multicore platforms.

# 3. DATA-TO-CORE ASSIGNMENT METHODOLOGY: A DEMONSTRATION ON IBM CELL ARCHITECTURE

IBM Cell Architecture [4,37,38] is an example of heterogeneous multi-core architectures, jointly designed by IBM, Toshiba, and Sony. The IBM Cell engine contains a traditional microprocessor called the power processing element (PPE), which deals with the orchestration and the coordination of the synergistic processing elements (SPEs). The tasks are performed by eight SPEs that work in parallel, and all components on the chip are connected via an element interconnect bus. IBM Cell is suitable for applications demanding high performance since it offers high computational power.

N-body is an important problem that can be applied to extensive applications from various domains in engineering and science, and it is one of the computation-intensive problems in the 13 dwarfs [46]. This problem simulates the motion of particles under pairwise interaction among n bodies for a predefined time period. At each time step, pairwise forces are calculated for all particles; this requires  $O(n^2)$  computations, which are not feasible when millions of particles are considered. Therefore, in order to reduce the complexity of the problem, many approximation algorithms are proposed. The Barnes-Hut method [47] is one of the most popular approximation algorithms, which reduces the computational complexity of the N-body problem to  $O(n \log n)$ . It is widely used due to its simplicity and easily programmable nature without requiring complicated data structures.

Many algorithms from a variety of domains have been parallelized and developed on the Cell architecture to take advantage of the performance and power utilization of the Cell processor. The potential of the Cell processor for several scientific computing kernels and the performance and power efficiency of the Cell architecture for these kernels have been presented [39]. The parallel implementation of fast fourier transform (FFT) on the Cell processor is also shown in the literature [40–42]. Additionally, a complexity model for algorithm designs on the Cell with an implementation of the list

ranking problem is given in Bader et al.'s study [43]. The performance and design choices of the breadth-first search algorithm is explored in Villa et al.'s study [44]. Bio-informatics applications [45] also have been tested on the Cell processor. These studies highlight the performance and the architectural restrictions of the Cell processor for various applications.

N-body is an important problem that can be applied to extensive applications from various domains in engineering and science, and it is one of the computation intensive problems in the 13 dwarfs [46]. This problem simulates the motion of particles under pairwise interaction among n bodies for a predefined time period. At each time step, pairwise forces are calculated for all particles; this requires  $O(n^2)$  computations, which is not feasible when millions of particles are considered. Therefore, to reduce the complexity of the problem, many approximation algorithms are proposed. The Barnes-Hut method [47] is one of the most popular approximation algorithms, which reduces the computational complexity of the N-body problem to  $O(n \log n)$ . It is widely used due to its simplicity and easily programmable nature without requiring complicated data structures.

This work presents the dynamic data-to-core assignment methodology by mapping our parallel implementations of the Barnes-Hut algorithm onto the Cell BE Architecture [48]. Although Cell Architecture is suitable for computation-intensive parallel applications such as Barnes Hut algorithm, programming the Cell Architecture is quite difficult due to its architecture-specific limitations and empirical optimization schemes. While designing our parallel methods, these limitations are considered.

#### 3.1. N-body Problem and Barnes-Hut Method

The N-body problem is used to simulate the evolution of n particles in a space by calculating the pairwise forces among them. Due to the interactions among particles, a net force is exerted on each particle, which causes them to move within a specified time. In each time step, with the movement of the particles, the forces are recalculated,

because the force is dependent on the distance between particles. Some application areas of the problem are astrophysics, molecular dynamics, plasma physics, embedded SAR data processing, and protein folding.

At each time step, the N-body problem requires  $n^2$  interactions; it calculates all pairwise forces, so the exact formulation of this problem requires  $O(n^2)$  computations. To reduce the complexity of the problem, many methods have been proposed. The Barnes-Hut method [47,49], which has a computational complexity of  $O(n \log n)$ , is a popular algorithm due to its simplicity. Another approximation algorithm is the Fast Multipole Method [50] with a complexity of O(n), which has working principals similar to those of the Barnes-Hut method except that it uses complex data structures.

The Barnes-Hut method uses a hierarchical tree representation of space and reduces the number of interactions among particles by grouping relatively close particles under a single tree node. The sequential implementation of this method has two phases: tree construction phase and force computation phase. In the tree construction phase, the domain is represented with a tree in which the leaves are the particles themselves, and internal nodes are the clusters grouping nearby bodies (i.e., particles). This phase starts with an empty space, and particles are added to the domain one by one. For a 2D space, the domain is recursively divided into four equal sub-domains if the domain contains more than one particle. This process is repeated until each sub-domain contains a single particle at each time step. The force acting on particles is calculated in the force computation phase. Instead of calculating pairwise interactions among the particles, the force between the nodes of the tree and particles is calculated using the distance between the particle and the center of mass of the node.

To cluster particles and represent the clusters with internal nodes, the center of mass and the total mass of the particles in the cluster are calculated, and this information is stored in each internal node. The net force on each particle is calculated by traversing all nodes of the tree, starting from the root. If the center of mass of an internal node is sufficiently far away from the particle, the particles contained in the

internal node are approximated as a single particle, and the net force acting on the particle is calculated using internal nodes' mass and center of mass information. If the center of mass of an internal node is not sufficiently far away from the particle, then each of the sub-nodes of the internal node is explored and traversed recursively.

The multipole acceptance criteria (MAC) [47] determines whether a node is at a sufficient distance from a particle, and it is equal to the ratio of the dimension of the domain to the distance of the particle from the center of mass of the domain. If this ratio is less than the predefined constant  $\lambda$ , the node is at a sufficient distance from the particle and an interaction can be computed; otherwise, the node is expanded to its sub-nodes, and the force between the particle and center of mass of the sub-nodes is computed recursively. The speed and accuracy of the simulation is determined by setting a proper value for  $\lambda$ . The value of  $\lambda$  is in the given range  $0 \le \lambda \le 1.0$ ; and if it is equal to 0, the Barnes-Hut application is turned into the N-Body problem in which all nodes are explored and the pairwise force among all particles is calculated. The increase in  $\lambda$  value decreases the number of nodes explored and also decreases the accuracy of the calculations performed.

Although there are various parallel implementations of the Barnes-Hut method in the literature [49,51], which are either for message-passing architectures [52] or shared-memory architectures [53], they can not be directly mapped to the Cell architecture. The sequential non-recursive Barnes-Hut algorithm given in Figure 3.1 is the basis of our parallel implementation running on the Cell architecture.

## 3.2. IBM Cell Broadband Engine Architecture

The Cell Broadband Engine (the Cell B./E.) [37, 38] is a high-performance architecture designed by Sony, Toshiba, and IBM that targets multimedia and gaming applications. The Cell is used in Sony's Play Station 3 gaming console, Mercury Computer System's dual Cell-based blade servers, IBM's QS20 - QS21 - QS22 Cell Blades, and Roadrunner, which has a speed of 1.06 Petaflops. The Cell is designed to increase

```

1. for time=0 to endTime do

2.

for i=0 to particleNumber do

3.

Insert particle i to the tree

Update center of mass and total mass of each internal node on the way

4.

5.

end for

for i=0 to particleNumber do

6.

7.

Add root node to visitList

while visitList is not empty do

8.

9.

Calculate distance between particle i and center of mass of node

if center of mass of the node and particle i are distantthen

10.

Calculate force acting on particle i

11.

12.

else

Add children of node to visitList

13.

14.

end if

end while

15.

end for

16.

17.

for i=0 to particleNumber do

18.

Update position and velocity of particle i

end for

19.

20. end for

```

Figure 3.1. Sequential version of Barnes-Hut algorithm.

microprocessor efficiency in terms of both power and performance. The clock speed of the Cell processor is 3.2 GHz and it has a single-precision peak performance of 204.8 Gflops/s and double-precision peak performance of 14.6 Gflops/s.

Figure 3.2. Cell Broadband Engine Architecture [37].

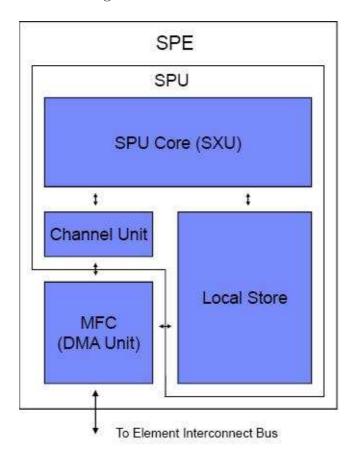

The Cell B./E. consists of a traditional microprocessor (power processing element-PPE), 8 smaller and simpler processors (SPEs) and an element interconnect bus (EIB) which connects the processors and provides access to main memory and I/O devices. General overview of the Cell Broadband Engine Architecture can be seen in Figure 3.2. The PPE is a dual-issue processor so it supports two-way simultaneous multithreading. Each SPE consists of a Synergistic Processor Unit (SPU), a Local Store (LS) and a Memory Flow Controller Unit (MFC). The instruction set of SPEs is designed to take advantage of 128-bit registers, and most of the instructions are single instruction multiple data (SIMD) instructions. Memory operations access 128-bits at a time even if the request data is 8-bits, so for an efficient implementation, the programmer should request 128-bits in each memory operation. SPEs are in-order processors with two instruction pipelines, namely the even pipeline and the odd pipeline. The even pipeline is responsible for arithmetic operations, and the odd pipeline deals with memory and branch instructions.

In a single clock cycle, SPEs can dispatch two instructions if these instructions have no data dependency. SPEs do not have a cache, but they have a 256 Kbyte LS

which can be called private memory. Both the program and the data should be in LS to be executed. SPEs have no direct access to main memory and a direct memory access (DMA) controller is used to perform high bandwidth data transfers among the local store, main memory and other local stores. EIB connects all components of the Cell processor including the PPE, the SPEs, the main memory, and I/O. It supports a peak bandwidth of 204.8 Gbytes/s [56]. EIB is build of 16-byte wide four unidirectional rings, two in each direction.

The details of the Cell B.E. Architecture and Cell programming models are given in Appendix A.

## 3.3. Parallelization of Barnes-Hut Algorithm on the Cell Processor

This section presents common characteristics of our two parallel implementations of the sequential Barnes-Hut Algorithm (given in Figure 3.1) for the Cell Architecture. As part of parallelization, we aim to distribute data across SPEs. Since our workspace contains large number of particles and each SPE contains a 256KB Local Store, it is not possible to hold all data and the tree on each SPE. Therefore, the tree representing a part of the domain is gradually constructed in the SPEs and the force calculation is replicated for each local tree of the SPEs. In our initial parallelization, the number of particles in the domain is distributed equally among all SPEs to overcome both the limited size of the local stores and the time wasted on the synchronization barrier due to load imbalances among SPEs. The total number of nodes in the global tree is distributed among the SPEs in our enhanced parallelization.

To exploit the unique features of the Cell Architecture, a set of issues such as avoiding branches, vectorizing the corresponding code, and overlapping memory access with computation should be considered [61]. Since the Cell Engine has no branch prediction mechanism, we consider the non-recursive version of the Barnes-Hut algorithm as the starting point. Some of the if-then-else statements in the code are replaced with *select bits* instruction for eliminating branches. Additionally, the

loops in the code are unrolled partially by decreasing the number of iterations and replicating the instructions in the loops. To reduce memory access latencies, DMA transfers and computations are overlapped through double buffering. The Barnes-Hut method performs the same computations on a large amount of 3D data repeating in each direction. In the force calculation phase (which is common in our two parallel implementations, as explained below), pairwise computations between particles and tree nodes are performed, where each computation is between a particle and the center of mass of a tree node. Each particle and the tree node is represented with a vector, and all operations performed are SIMDized. All data transferred between memory and the local store are stored contiguously in memory. Double-buffering usage is efficient for this type of implementation. After both the force calculation and the position and velocity updates are performed, the SPEs are synchronized using mailboxes that send and receive 32 bit messages.

- 1. Initialize data structures

- 2. Create SPEs

- 3. DMA: Initiate transfers to put blocks of particle coordinates to LS

- 4. Synchronization using mailbox

- 5. for time=0 to endTime do

- 6. Arrange all particles in the sub-domains

- 7. Use load information of the sub-domains and distribute load between SPEs

- 8. Map sub-domains to SPEs

- 9. Wait for SPEs to finish tree construction and force calculation

- 10. Synchronization using mailbox

- 11. Wait for SPEs to finish position and velocity updates

- 12. Synchronization using mailbox

- 13. end for

Figure 3.3. View within PPE for the initial parallelization.

```

1. DMA: Initiate transfers to get blocks of particle coordinates

2. for i=0 to particleNumber do

Determine which sub-domain particle i belongs to

4. end for

5. DMA: Put the data with its sub-domain information from LS back to MM

6. Synchronization using mailbox

7. for time=0 to endTime do

while more sub-domains to visit

while more blocks to process

9.

10

DMA: Load mass and coordinates of particles in the sub-domain from MM into LS

11.

for i=0 to subParticles do

12.

Insert particle i to the tree

Update center of mass and total mass of each internal node on the way

13.

end for

14.

end while

15.

16.

while more blocks to process

17.

DMA: Load mass and coordinates of all particles in the space

18.

DMA: Load force of all particles in the space

19.

for i=0 to allParticles do

Add root node to visitList

20.

21.

while visitList is not empty

22.

Calculate distance between particle i and the center of mass of the node

23.

if center of mass of the node and particle i are distant then

24.

Calculate force acting on particle i

25.

else

Add children of the node to visitList

26.

end if

27.

end while

28

29

end for

DMA: Put force of all particles in the space to MM

30

end while

31.

DMA: Put load information of sub-domain into MM

32.

33.

end while

34.

Synchronization using mailbox

35.

while more blocks to process

36.

for i=0 to particleNumber do

37.

DMA: Get force exerted by other SPEs on particle i

Calculate total force acting on particle i

38.

Update position and velocity of particle i

39.

40.

Determine which sub-domain particle i belongs to

41.

DMA:Put new position, sub-domain and velocity of particles from LS to MM

42.

43.

end while

44.

Synchronization using mailbox

45. end for

```

Figure 3.4. View within SPE for the initial parallelization.

#### 3.3.1. Initial Parallelization of the Barnes-Hut Method

Our initial parallelization has three phases: the domain decomposition phase, the tree construction and the force calculation phase, and the position and velocity updates phase. The following subsections explain these phases in detail. The related pseudocodes for the PPE-specific and SPE-specific parts are given in Figure 3.3 and Figure 3.4, respectively.

3.3.1.1. Domain Decomposition. The domain is decomposed into smaller parts (called sub-domains) in which each part contains a limited number of particles that can fit in the LS of each SPE. Initially, the PPE fetches the positions, velocities, and masses of particles, and it distributes the position of particles equally to the SPEs to obtain their sub-domain information. After the PPE obtains this information from the SPEs, it constructs sub-domains and uses the load information of sub-domains to give equal workload to each SPE. In the first iteration, the workload is divided into w equal units of data, where total number of particles in the workload is equal to w\*p, and p is the number of SPEs used in execution. When the first iteration ends, the number of nodes explored by the local tree representing a sub-domain during force calculation in the previous iteration is used as the workload metric of the sub-domain for the current iteration. After the PPE completes sub-domain allocation, it sends the sub-domains to the SPEs on which they will operate. Finally, each SPE fetches its data from memory and starts its local tree construction.

3.3.1.2. Tree Construction and Force Calculation. In this phase, an octree representing the particles in a sub-domain is constructed by each SPE. Then, the force acting on all particles in the workload is calculated on all SPEs using their own local trees. Since the SPEs have local stores of limited size, they operate on many sub-domains by obtaining each sub-domain one by one. When the local tree representation of the sub-domain is finished, it starts the force calculation among the particles and the sub-nodes by traversing the tree starting from the root.

Interactions with the top nodes of the tree are calculated first, and then the sub-nodes are explored, if necessary. If the center of mass of an internal node is sufficiently far away from the particle, the particles contained in the internal node are approximated as a single particle, and the net force acting on the particle is calculated using the internal nodes' mass and center of mass information. To determine whether a node is sufficiently far away from a particle, MAC [47] is computed, which is the ratio of the dimension of the sub-domain to the distance of the particle from the center of mass of the given sub-domain. If a particle is too distant from a cluster of particles (where MAC is less than a predefined  $\lambda$  value), the particles contained in the cluster are represented with a single particle.

Each SPE is responsible for different sub-domains, and there will be more interactions between particles and nodes that are close to each other in the domain. As soon as the force calculation ends, each SPE writes back the calculated force values of all particles in its local tree to the memory and obtains the data of the new sub-domain. The tree construction and force calculation phase continues until all sub-domains assigned to the SPEs are processed.

Figure 3.5 shows the local trees that are constructed by each SPE for the given domain ((a) in Figure 3.5). There are 14 particles in this domain, which are processed by 4 SPEs. In the first phase, the domain information of particles is obtained by using their x and y coordinates, and each SPE is assigned an equal number of particles to work on. Therefore, SPE1, SPE2 and SPE3 receive 4 particles each, and SPE4 receives the remaining 2 particles. In the second phase, sub-domains are distributed among SPEs. There are 4 sub-domains, so each SPE handles one sub-domain. According to the number of particles in the sub-domains, SPE1 and SPE2 receive 3 particles, SPE3 and SPE4 receive 4 particles. Although SPE1 and SPE2 have the same number of particles, their tree construction times differ, as the depths of their trees are not the same.

Figure 3.5. A typical step of the first parallel version with 14 particles using 4 SPEs.

(a) Domain decomposition (b) Local tree construction in SPEs (c) Force calculation and position updates in SPEs.

When the number of the nodes used to construct the local trees ((b) in Figure 3.5) are compared, SPE1 and SPE3 have 5 nodes, SPE2 has 4 nodes, and SPE4 has 6 nodes. Therefore, SPE2 has the lowest running time for tree construction, and SPE4 has the highest running time. It should be noted that SPE1 and SPE2 differ in terms of the running times for tree construction, although they have an equal number of particles in their sub-domains. In the force calculation phase, the local tree is explored for each particle ((c) in Figure 3.5). The running time of this phase is much longer than that of the tree construction phase. Additionally, the running time of this phase may vary among the SPEs due to the different number of nodes to be explored by themselves, which results in an unbalanced load among SPEs.

3.3.1.3. Position and Velocity Updates. After the force calculation phase is completed, the net force acting on each particle is calculated using all force values calculated on all local trees. Then, the particle's velocity and position values are updated accordingly. This process is repeated for a predefined number of iterations, and at the end of the simulation, each particle has a new position and velocity value.

#### 3.3.2. Enhanced Parallelization of the Barnes-Hut Method

In our initial parallelization, implementation of the tree construction phase by using only the particles in the sub-domains causes loss of clusters of the domain. The tree construction phase is the heart of the Barnes-Hut algorithm. A good clustering of particles results in less computation for the force calculation phase. Therefore, our second parallel implementation is built on the idea of obtaining better clustering of the particles in the domain. Although the global tree is required in order to achieve this goal, it cannot be stored in the LS of the SPEs due to memory limitations. Therefore, the first phase of our enhanced parallelization is the sequential tree construction phase, where PPE constructs the global tree by using all particles in the domain, dividing global tree into sub-trees. The second phase of the enhanced parallelization is the local tree construction and force calculation phase, where SPEs use sub-trees to construct their local trees. The last phase, the position and velocity updates phase, is the same as

the previous parallelization; therefore, it is not repeated in the following subsections. The related pseudo-codes are given in Figure 3.6 and Figure 3.7.

- 1. Initialize data structures

- 2. Generate global tree

- 3. Create sub-trees and store node information to tree array

- 4. Map sub-trees to SPEs

- 5. Create SPEs

- 6. for time=0 to endTime do

- 7. Wait for SPEs to finish tree construction and force calculation

- 8. Synchronization using mailbox

- 9. Wait for SPEs to finish position and velocity updates

- 10. Generate global tree

- 11. Create sub-trees and store node information to tree array

- 12. Map sub-trees to SPEs

- 13. Synchronization using mailbox

- 14. end for

Figure 3.6. View within PPE for the enhanced parallelization.

3.3.2.1. Global Tree Construction. In this phase, PPE constructs a global tree that contains all the particles in the domain, and then it divides the global tree into subtrees by using depth first search. The number of sub-trees depends on the total number of nodes generated in the global tree and the number of SPEs in use. In this parallelization, the total number of nodes are distributed equally among SPEs to have better load balancing. These sub-trees are stored as contiguous data in order to have a predictable memory access pattern. Each element in the array represents a node in the tree and contains the center, the total mass, the total number of children nodes, and the dimensions of the domain represented by the node. After PPE completes the generation of sub-trees, SPEs fetch their data from memory and start local calculations.

```

1. for time=0 to endTime do

2.

while more trees to generate

3.

while more blocks to process

DMA: Load tree nodes information from MM into LS

4.

5.

for i=0 to nodeNumber do

6.

Insert node i to the tree

end for

7.

end while

8.

while more blocks to process

9.

10.

DMA: Load mass and coordinates of all particles in the space

DMA: Load force of all particles in the space

11.

for i=0 to particleNumber do

12.

Add root node to visitList

13.

while visitList is not empty

14.

15.

Calculate distance between particle i and the center of mass of the node

if center of mass of the node and particle i are distant then

16.

17.

Calculate force acting on particle i

18.

19.

Add children of the node to visitList

20.

end if

21.

end while

22.

end for

23.

DMA: Put force of all particles in the space to MM

24.

end while

end while

25.

26.

Synchronization using mailbox

while more blocks to process

27.

28.

\mathbf{for} \ \mathbf{i} = \mathbf{0} \ \mathbf{to} \ \mathbf{particleNumber} \ \mathbf{do}

29.

DMA: Get force exerted by other SPEs on particle i

30.

Calculate total force acting on particle i

31.

Update position and velocity of particle i

32.

33.

DMA:Put new position and velocity of particles from LS to MM

34.

end while

Synchronization using mailbox

36. end for

```

Figure 3.7. View within SPE for the enhanced parallelization.

3.3.2.2. Tree Construction and Force Calculation. In this phase of the algorithm, each SPE obtains the number of sub-trees assigned to it and loads the nodes of the trees from memory to its local store one by one. The tree construction phase is simpler in this parallel implementation because the positions of the nodes are not searched in the whole local tree. Instead, this information is calculated by the PPE and is stored in the tree array. One disadvantage of this method is that additional variables are needed to store upper levels of the tree nodes, and this reduces the available space reserved for keeping local trees. On the other hand, this method has two advantages. It decreases the number of comparisons in finding the position of the particles in the trees thus reduces tree construction time. In addition, the upper levels of the local trees that contain the clustering information of the domain are included in the local trees generated. This reduces the total execution time of the force calculation phase by decreasing the number of comparisons in this phase. After local trees are constructed, the tree is traversed starting from the root, and the force acting on each particle in the domain is calculated. It should be noted that force calculation phase implementation is the same as described in Section 3.3.1.2. This phase continues until all local trees assigned to the SPEs are processed.

Figure 3.8 shows the global tree that is sequentially constructed by the PPE for the same domain used in initial parallelization ((a) in Figure 3.5). The global tree contains 20 nodes (excluding the root node), and the root node is replicated in all local trees assigned to 4 SPEs. The number of nodes distributed is 24, and each SPE should obtain approximately 6 nodes. While constructing the local trees, the PPE first considers keeping the clusters together; then, it takes the number of nodes into account. In this enhanced parallelization, the number of nodes is considered, which is different than the initial parallelization in which the number of particles is considered instead. This change aims to balance load among SPEs.

Figure 3.8 shows the local trees constructed by SPEs and the particles used in force calculation, as well as position and velocity update phases. The local tree includes upper level tree information ((b) in Figure 3.8). For a higher number of particles, this

information is very valuable, because it decreases the number of nodes explored.

Figure 3.8. A typical step of the second parallel version with 14 particles using 4 SPEs. (a) Global tree construction (b) Local tree construction, force calculation and position updates in SPEs.

## 3.3.3. Experimental Work and Analysis of Results

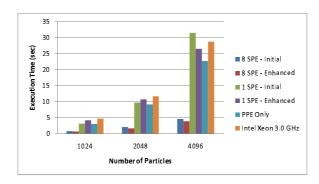

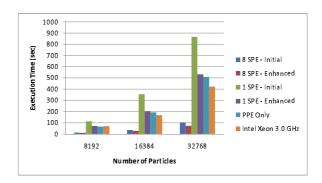

The performance results presented in this section are from actual runs on an IBM Blade Center QS20 with two 3.2GHz Cell BE processors, 512 KB Level 2 cache per processor and 1 GB memory. Our code is compiled using gcc compiler in the Cell SDK

3.1 with -O3 optimization flag for performance analysis. As mentioned before, loop unrolling, double-buffering, and vectorization are used to decrease execution time on the SPEs. The code running on the PPE is also optimized by loop unrolling, branch elimination, and vectorization. In all experiments performed, the number of particles used varies from 1024 to 32768, the number of buffers used is 2,  $\lambda$  is 0.5, and the number of iterations is 50, unless otherwise stated.

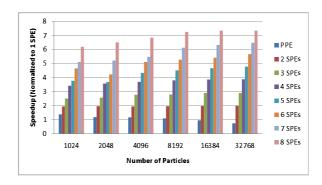

Figure 3.9. Speedup with respect to different number of SPEs and PPE - initial parallelization.

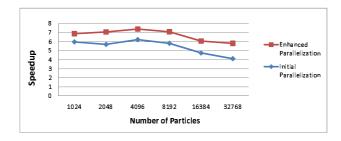

In the first set of tests, the performance of our algorithm is measured by varying the number of the SPEs used for different particle sizes. Figure 3.9 and Figure 3.10 show the speedup values that are normalized to a single SPE for the initial and enhanced parallelizations, respectively. The running time of the PPE is also included in the experiments. Considering that the Barnes-Hut algorithm is branchy, the PPE runs the code faster than a single SPE does. When 1024 particles are considered, 2 SPEs run 1.61, 4 SPEs run 2.2, and 8 SPEs run 3.98 times faster than 1 SPE in the initial parallelization. Similarly, in the enhanced parallelization, 2 SPEs run 1.93, 4 SPEs run 3.4, and 8 SPEs run 6.17 times faster than 1 SPE.